在上期中,我們介紹了控制 PFC 并實現單位功率因數的新方法。

本期,為大家帶來的是《ADC 噪聲系數如何影響射頻接收器設計》,我們將深入探討如何計算射頻采樣 ADC 的噪聲系數,并說明ADC 噪聲系數對射頻信號鏈設計的影響。

引言

為了制造更小的數字接收器,航天和國防工業采用了現代直接射頻 (RF) 采樣模數轉換器 (ADC)。這些 ADC 消除了射頻混合級,并更靠近天線,從而簡化了數字接收器設計,同時還節省了成本和印刷電路板 (PCB) 面積。

一個關鍵(經常被誤解的)參數是 ADC 噪聲系數,該參數設置用于檢測極小信號的射頻增益量。本文介紹了如何計算射頻采樣 ADC 的噪聲系數,并說明了 ADC 噪聲系數對射頻信號鏈設計的影響。

為什么噪聲系數

在數字接收器設計中很重要

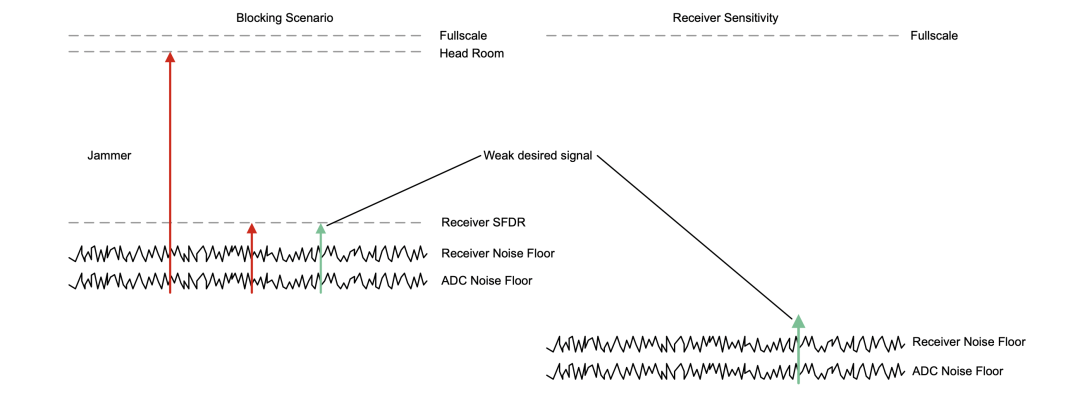

數字接收器在兩種不同場景下工作,如圖 1 所示。在阻斷情況下,存在干擾或干擾器,接收器必須以較低的射頻增益運行,以免使 ADC 飽和。在此設置中,ADC 被干擾信號驅動至接近滿量程;因此,ADC 的大信號信噪比 (SNR) 決定了可檢測到的信號微弱程度。還有其他降級機制,例如相位噪聲和無雜散動態范圍。

在第二種場景中,不存在干擾。檢測可能的最弱信號僅取決于接收器的固有本底噪聲,這種情況通常以接收器靈敏度進行測量。噪聲系數用于測量由接收器信號鏈中的元件引起的 SNR 降級。

圖 1. 阻斷或干擾情況與接收器靈敏度場景的比較

ADC 的噪聲系數通常是接收器的薄弱環節(約為 25dB 至 30dB),而低噪聲放大器 (LNA) 的噪聲系數低至 <1dB。不過,可以通過使用 LNA 向模擬射頻前端(靠近天線)添加增益來改善 ADC 噪聲系數。1dB 接收器系統噪聲系數和 2dB 接收器系統噪聲系數之間的差異約為 20%。這種差異意味著噪聲系數為 1dB 的接收器可以檢測振幅大約弱 20% 的信號。在軟件定義無線電 (SDR) 中,這意味著無線電輸出功率降低,從而延長電池壽命,而在雷達中,這使得覆蓋更遠的距離成為可能。

SDR 或數字雷達中的現代接收器設計使用直接射頻采樣 ADC 來減小尺寸、減輕重量并降低功耗。該架構無需射頻下變頻混頻級,從而簡化了接收器設計。ADC 噪聲系數越好,所需的增益越低,實現的節省越多。此外,使用更少的額外射頻增益意味著當存在干擾時,需要降低的增益更小,并在接收器中保持更高的動態范圍。

計算系統的噪聲系數

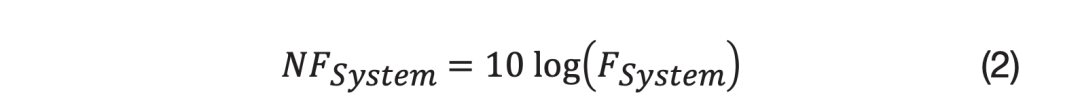

您可以使用 Friis 公式來計算接收器系統的噪聲系數。假定一個具有兩個放大器和一個 ADC 的簡化的理想接收器,如圖 2 中所示,方程式 1 按如下方式計算級聯系統噪聲因子:

方程式 1

其中 Fx 是噪聲因子,Gx 是功率增益。

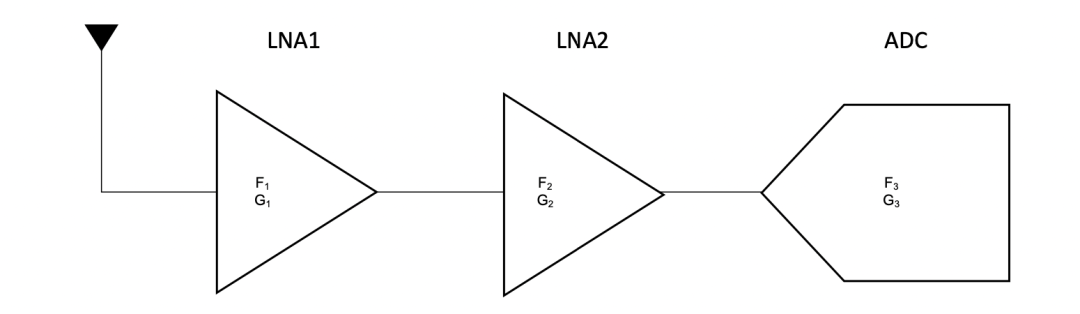

以分貝為單位的系統噪聲系數為:

方程式 2

圖 2. 典型接收信號鏈

此處需強調兩個要點:系統噪聲系數主要由第一個元件的噪聲系數 F1 決定,前提是增益 G1 和 G2 足夠大,以至于 ADC 噪聲系數 F3 可以忽略不計。

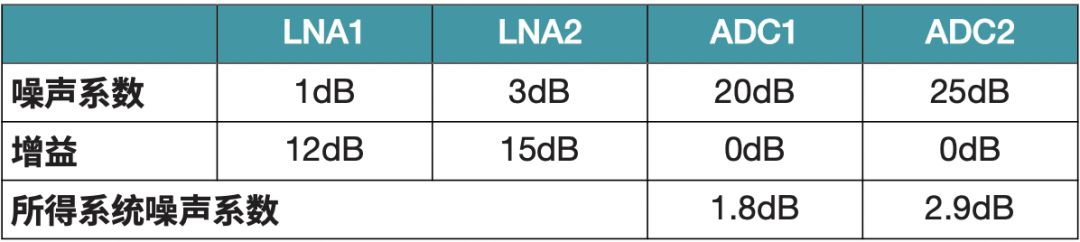

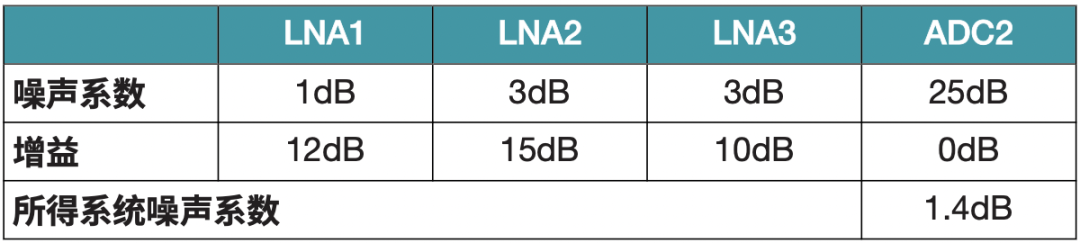

在具有兩個級聯 LNA 的系統中比較兩個分別具有20dB 與25dB 噪聲系數的不同 ADC,可以看出系統噪聲系數有很大差異(請參閱表 1)。

表 1. 具有兩個 LNA 級的系統噪聲系數

如表 2 所示,將 ADC2 列中列出的系統(噪聲系數相差5dB)設置為低于 2dB 的系統噪聲系數,將需要使用第三個 LNA(噪聲系數 = 3dB)額外增加 10dB 的增益。

表 2 突出了 ADC 噪聲系數對整體系統噪聲系數的影響。添加第三個 LNA 會增加成本、電路板面積(匹配元件、布線和電源)和系統功耗,并進一步降低滿量程余量。

表 2. 使用 ADC2 且具有

三個 LNA 級的系統噪聲系數

假設目標接收器靈敏度為 -172dBm,或非常弱的信號僅比絕對本底噪聲高 2dB (-174dBm + 2dB = -172dBm),則該接收器需要優于 2dB 的噪聲系數。在上面的示例中,我們使用 ADC1(噪聲系數為 20dB,如表 1 中所列),級聯系統噪聲系數為 1.8dB。

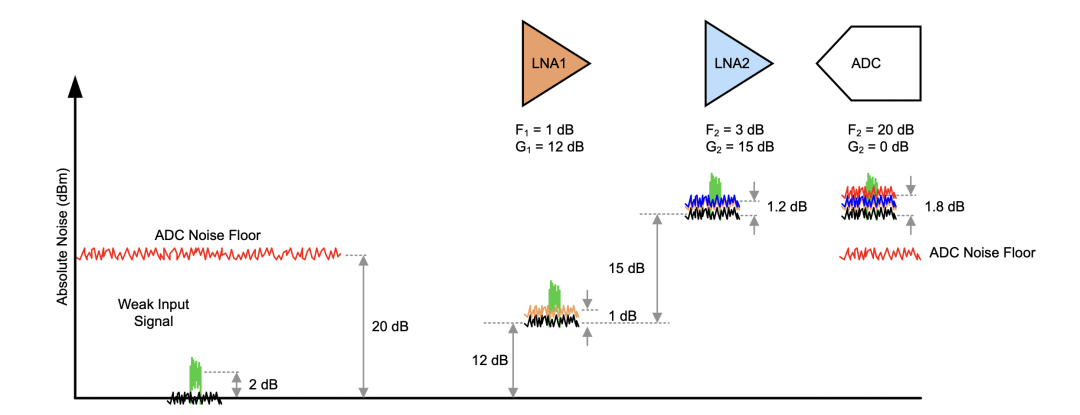

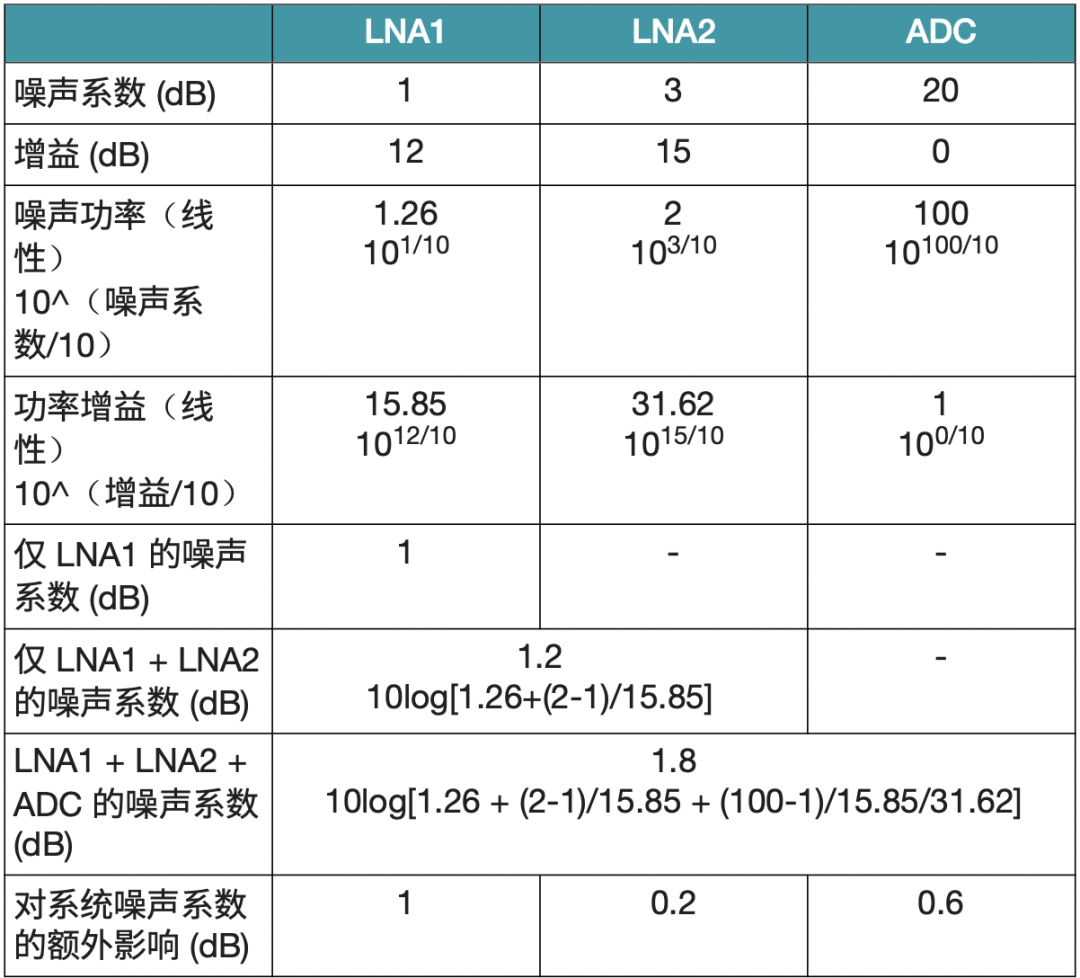

如圖 3 和表 3 所示,增益為 12dB 的 LNA1 將輸入信號和噪聲提高 12dB,而將噪聲系數降低 1dB(噪聲系數 LNA1= 1dB)。LNA2 將信號和噪聲提高了 15dB。盡管 LNA2 具有更高的固有噪聲圖 3dB,但由于 LNA1 的增益為 12dB,其影響僅降至 0.2dB。

最后,ADC1 的噪聲分量(噪聲系數 = 20dB)減少至僅 0.6dB,因為它會被兩個 LNA 的 27dB 增益降低。因此,您最終會得到 1.8dB 的系統噪聲系數,從而留下大約 0.2dB 的余量來檢測微弱的輸入信號。

圖 3. 接收信號鏈中各個噪聲系數貢獻的圖示

表 3. 計算各個噪聲系數的貢獻

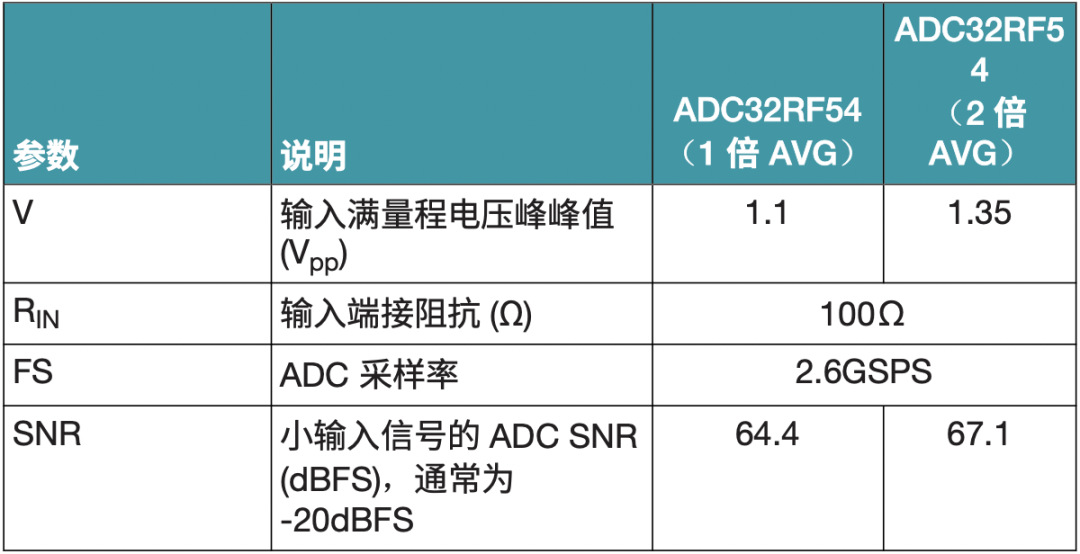

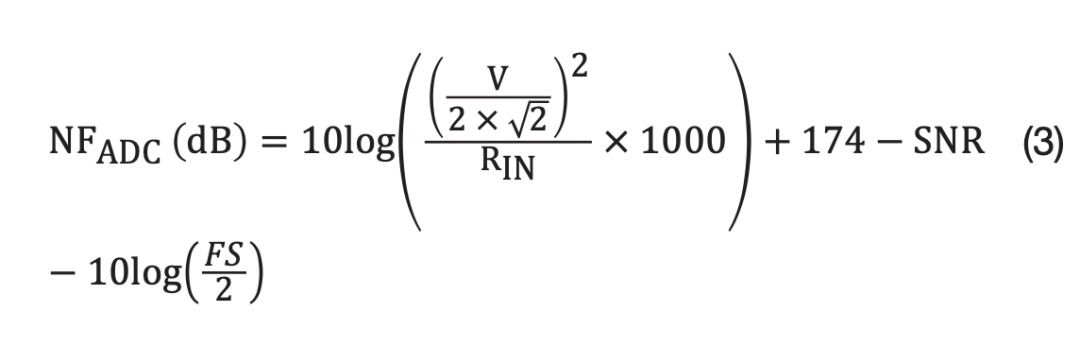

高速數據轉換器很少在器件特定數據表中列出噪聲系數。可以使用方程式 3根據 ADC32RF54 射頻采樣 ADC 的常用數據表參數(請參閱表 4)計算 ADC 的噪聲系數。

表 4. ADC32RF54 的數據表參數

ADC Noise figure (dB) = PSIG,dBm + 174 dBm – SNR (dBFS) – bandwidth (Hz)

方程式 3

對于 ADC32RF54,噪聲系數計算結果為:

噪聲系數(1 倍 AVG)= 20.3dB

10log[(1.1/2/sqrt(2))2/100 x 1000] + 174 - 64.4 -10log[2.6e9/2]

噪聲系數(2 倍 AVG)= 19.3dB

10log[(1.35/2/sqrt(2))2/100 x 1000] + 174 - 67.1 -10log[2.6e9/2]

結論

接收器噪聲系數是一個重要的系統設計參數,因為它決定了最弱可檢測信號。除了非常低的固有噪聲系數外,ADC32RF54 還提供了高 SNR,即使在輸入功率信號較大的情況下,也能讓系統保持其噪聲系數。具有相同噪聲系數但 SNR 更低的 ADC 需要降低輸入增益,以防止飽和,在這種情況下,ADC 噪聲系數開始增加總體噪聲。

-

adc

+關注

關注

98文章

6438瀏覽量

544090 -

信號鏈

+關注

關注

0文章

200瀏覽量

29803 -

噪聲系數

+關注

關注

1文章

66瀏覽量

16660 -

射頻接收器

+關注

關注

0文章

12瀏覽量

11094

原文標題:模擬芯視界 | ADC 噪聲系數如何影響射頻接收器設計

文章出處:【微信號:tisemi,微信公眾號:德州儀器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

計算ADC噪聲系數需知

測量射頻設備噪聲系數的三種方法

多通道射頻接收機測量噪聲系數的方法

如何進行噪聲系數測量?

手機接收通道噪聲系數測試

頻譜分析儀和噪聲系數測量

那些不可錯過的ADC噪聲系數詳解

ADC噪聲系數的認識及其分析

量化和熱噪聲如何確定ADC的有效噪聲系數

噪聲系數測量方法和公式

最經典的噪聲系數測試方法—Y因子法

ADC噪聲系數對射頻接收器的影響

ADC噪聲系數對射頻接收器的影響

評論