本文簡單介紹了高K金屬柵極的結構、材料、優勢以及工藝流程。

High-K Metal Gate(HKMG)技術是現代半導體制造中的關鍵技術之一,廣泛應用于45nm、32nm、22nm及以下節點的高性能的邏輯芯片和DRAM。

HKMG結構

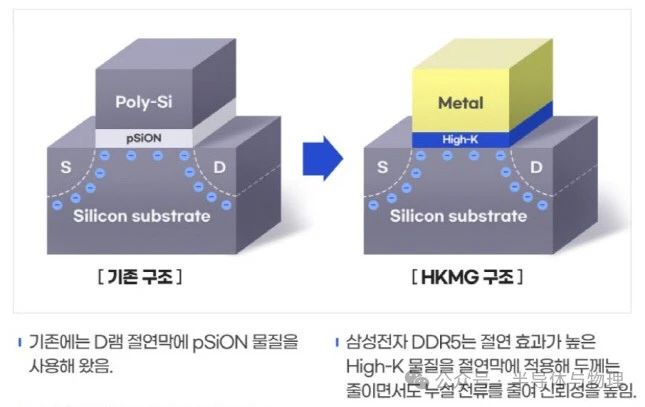

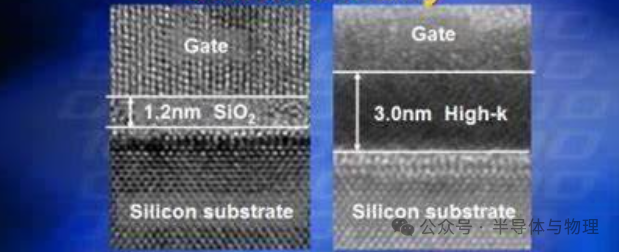

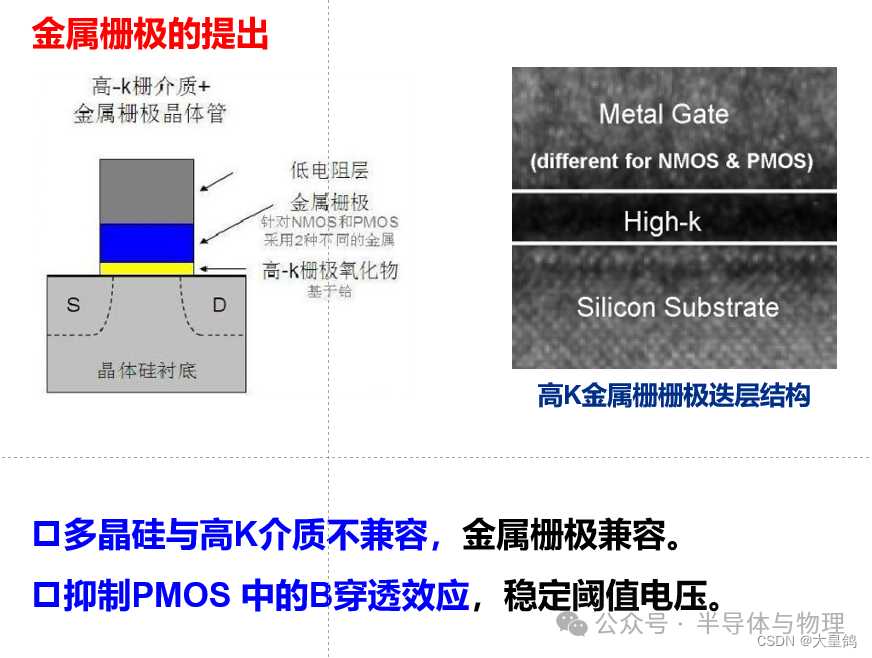

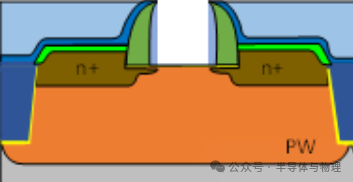

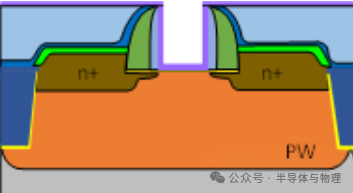

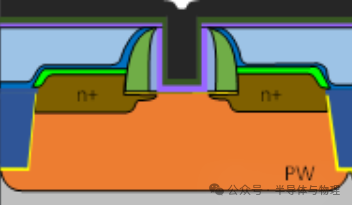

HKMG技術的核心在于使用高K材料替代傳統的二氧化硅(SiO2)作為柵介質層,并使用金屬材料替代多晶硅作為柵極電極。具體來說: 高K材料:高K材料具有較高的介電常數,可以有效減少柵極漏電流,提高晶體管的工作效率。 金屬柵極:金屬柵極材料具有良好的導電性和熱穩定性,能夠更好地控制閾值電壓,提升器件的開關速度。

常用材料

高K材料:常見的高K材料包括鉿基氧化物(如HfO2、HfSiO、HfSiON等)、鋁基氧化物(Al2O3)、鋯基氧化物(ZrO2)等。 金屬柵極材料:常用的金屬柵極材料包括鈦氮化物(TiN)、鉭氮化物(TaN)、鎢(W)、鈷(Co)等。

為什么需要HKMG

隨著半導體器件尺寸的不斷縮小,傳統的SiO2/Si柵極結構面臨諸多挑戰,主要包括: 柵極漏電流過大:隨著柵極厚度的減小,柵極漏電流顯著增加,導致器件功耗增大。 閾值電壓難以精確控制:多晶硅柵極在納米尺度下難以精確控制閾值電壓,影響器件的性能。 性能提升需求:高性能計算和低功耗應用對晶體管的開關速度和能效提出了更高的要求。 HKMG技術通過引入高K材料和金屬柵極,不僅解決了上述問題,還進一步提升了晶體管的性能,使得更小、更快、更節能的電子設備成為可能。

為什么速度快

HKMG技術之所以能夠提升晶體管的速度,主要有以下幾個原因: 減少柵極漏電:高k材料(如HfSiON)具有較高的介電常數,可以在保持相同電容的情況下使用更厚的物理厚度,從而大幅降低柵極漏電,減少靜態功耗。 增強柵控能力:高k材料允許使用更厚的柵極絕緣層,同時保持良好的柵控能力,提高晶體管的開關速度和能效。 改善載流子遷移率:金屬柵極材料(如TiN)具有更優的功函數匹配,減少載流子在界面處的散射,提高載流子遷移率,增加導通電流(Ion),加快開關速度。

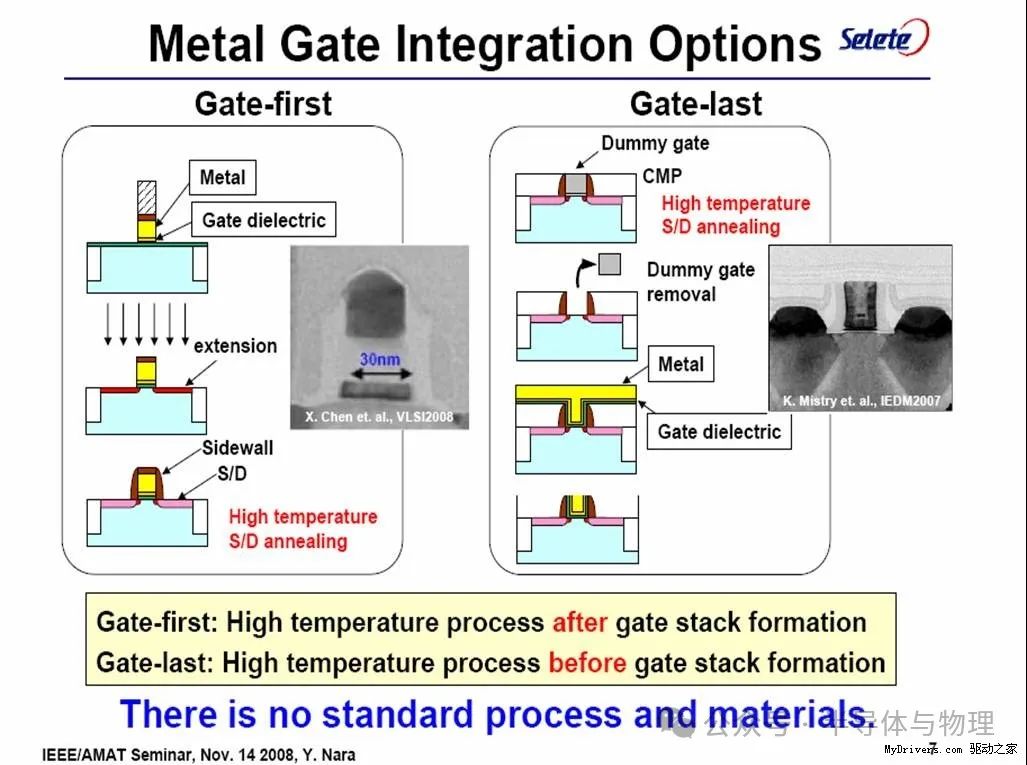

HKMG后柵工藝流程

HKMG技術的實現涉及多個復雜的工藝步驟,以下是一個典型的HKMG制程流程概述:

1.界面層沉積:

工藝技術淀積一層薄薄的SiON薄膜,目的是改善高K材料與襯底硅的界面態。

2.高K材料沉積: 通過金屬有機化學氣相沉積(MOCVD)淀積一層高K介質層HfSiO,然后再經過高溫氮化形成HfSiON。

3.金屬柵極沉積:

對于NMOS,通過原子層淀積(ALD)技術淀積厚度1nm的La2O3薄膜,形成覆蓋層,目的是通過改變NMOS柵極的功函數來調節NMOS的閾值電壓Vt。 通過ALD沉積厚度5nm~10nm的TiN金屬覆蓋層,形成金屬柵,改善柵極多晶硅耗盡。 對于PMOS,通過ALD技術淀積厚度1nm的Al2O3薄膜,形成覆蓋層,目的是通過改變PMOS柵極的功函數來調節PMOS的閾值電壓Vt。 通過ALD沉積厚度厚度5nm~10nm的TiN金屬覆蓋層,形成金屬柵,改善柵極多晶硅耗盡。

4.通過CMP進行平坦化,清除多余的金屬: 通過光刻和刻蝕技術定義出柵極的形狀和位置。

-

HKMG

+關注

關注

0文章

9瀏覽量

12860 -

半導體制造

+關注

關注

8文章

392瀏覽量

24040 -

金屬柵極

+關注

關注

0文章

5瀏覽量

5139

原文標題:高K金屬柵極(HKMG)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高K金屬柵極的結構、材料、優勢以及工藝流程

高K金屬柵極的結構、材料、優勢以及工藝流程

評論