Chiplet技術(shù)簡(jiǎn)介

Chiplet技術(shù),就像用樂(lè)高積木拼搭玩具一樣,將芯片的不同功能模塊,例如CPU、GPU、內(nèi)存等,分別制造成獨(dú)立的小芯片。然后,通過(guò)高速互聯(lián)技術(shù)將它們連接在一起,形成一個(gè)完整的芯片。比如說(shuō)NVIDIA最新發(fā)布的DGX B200,就是Chiplet技術(shù)下的產(chǎn)物。這也是NVIDIA第一款Chiplet GPU芯片,憑借 NVIDIA Blackwell 架構(gòu)在計(jì)算方面的進(jìn)步,DGX B200 的訓(xùn)練性能是 DGX H100 的 3 倍,推理性能是 DGX H100 的 15 倍,想了解更多Chiplet架構(gòu)的小伙伴,可以移步視頻號(hào)。

Chiplet的技術(shù)優(yōu)勢(shì)

01提高芯片良率

傳統(tǒng)的單芯片設(shè)計(jì)模式,隨著芯片尺寸的不斷縮小,邁入3nm、2nm制程后,芯片的良率成為一大挑戰(zhàn)。據(jù)悉,頭部晶圓大廠的3nm良率也僅在50%左右。而Chiplet技術(shù)將芯片設(shè)計(jì)分解成多個(gè)更小的模塊,每個(gè)模塊可以單獨(dú)進(jìn)行制造和測(cè)試,從而可以提高整體芯片的良率。

02降低芯片成本

隨著行業(yè)轉(zhuǎn)向更小的工藝節(jié)點(diǎn),生產(chǎn)大型芯片的成本持續(xù)增加。目前臺(tái)積電3納米晶圓每片成本為20,000美元,比5nm(16,000 美元)晶圓成本上漲了25%,而行業(yè)預(yù)計(jì)2nm晶圓成本將比3nm再增加50%。制造大型整體芯片將變得越來(lái)越不經(jīng)濟(jì)。在摩爾定律基本上不再帶來(lái)經(jīng)濟(jì)效益的情況下,Chiplet被認(rèn)為是最好的大芯片替代設(shè)計(jì)方法。Chiplet技術(shù)可以采用不同制程工藝、不同代工廠來(lái)制造不同的模塊,例如可以使用成熟的制程工藝來(lái)制造成熟的IP模塊,而使用更先進(jìn)的制程工藝來(lái)制造關(guān)鍵的性能模塊,這種混合制程工藝可以降低芯片的整體成本。

03提高芯片靈活性

Chiplet技術(shù)可以根據(jù)不同的需求定制芯片配置,例如可以根據(jù)客戶的需求選擇不同的IP模塊或調(diào)整模塊的數(shù)量。由于模塊化設(shè)計(jì)使得各個(gè)模塊獨(dú)立,設(shè)計(jì)者可以針對(duì)特定需求對(duì)特定模塊進(jìn)行優(yōu)化和迭代,而不會(huì)影響其他模塊。這種靈活性使得芯片能夠更好地滿足不同的市場(chǎng)需求。

Chiplet面臨的挑戰(zhàn)

1互聯(lián)技術(shù)挑戰(zhàn)

Chiplet技術(shù)需要使用高速互聯(lián)技術(shù)來(lái)將不同的Chiplet連接在一起。目前常用的互聯(lián)技術(shù)包括高速SerDes、PCI Express等,但這些技術(shù)的帶寬和成本都存在一定的限制。目前可以看到國(guó)際大廠在設(shè)計(jì)Chiplet芯片時(shí),都將互聯(lián)作為很重要的一環(huán)。像AMD的"Infinity Fabric"技術(shù)、英特爾的嵌入式多芯片互連橋 (EMIB) 等。

2封裝技術(shù)挑戰(zhàn)

Chiplet技術(shù)往往需要使用先進(jìn)的封裝技術(shù),如2.5D、3D封裝技術(shù)將不同的Chiplet封裝在一起,與此同時(shí),還要考慮散熱和功耗的要求。包括臺(tái)積電在內(nèi)的晶圓代工廠正在通過(guò)3D封裝技術(shù)來(lái)快速響應(yīng)Chiplet。

3生態(tài)系統(tǒng)挑戰(zhàn)

Chiplet技術(shù)需要一個(gè)完整的生態(tài)系統(tǒng)來(lái)支持,包括Chiplet設(shè)計(jì)工具、Chiplet制造工藝、Chiplet測(cè)試工具等。目前,Chiplet技術(shù)的生態(tài)系統(tǒng)還不完善,需要更多的企業(yè)和機(jī)構(gòu)加入到Chiplet生態(tài)系統(tǒng)的建設(shè)中來(lái)。

4標(biāo)準(zhǔn)化挑戰(zhàn)

Chiplet技術(shù)需要統(tǒng)一的標(biāo)準(zhǔn)來(lái)規(guī)范Chiplet的接口、互聯(lián)方式等。目前業(yè)界Chiplet的互聯(lián)標(biāo)準(zhǔn)規(guī)范有很多,有OIF聯(lián)盟的XSR,Open聯(lián)盟的BOW和OHBI,Chips Alliance的AIB,當(dāng)然,還有目前最熱的UCIe。UCIe(Universal chiplet interconnect express)互聯(lián)標(biāo)準(zhǔn)的誕生,為Chiplet互聯(lián)的兼容性和互操作性問(wèn)題帶來(lái)了很大的幫助,該標(biāo)準(zhǔn)由AMD、Arm、英特爾、高通、三星、臺(tái)積電、日月光、谷歌、Meta和微軟等十家行業(yè)巨頭聯(lián)合推出。隨著UCIe標(biāo)準(zhǔn)的不斷完善和推廣,Chiplet技術(shù)將得到更加廣泛的應(yīng)用,并對(duì)芯片產(chǎn)業(yè)產(chǎn)生深遠(yuǎn)的影響,是德科技作為UCIe聯(lián)盟的一員,也積極的參與到了標(biāo)準(zhǔn)的制定中來(lái)。

是德科技在Chiplet方面的儲(chǔ)備

Chiplet技術(shù)需要對(duì)Chiplet之間的互聯(lián)進(jìn)行設(shè)計(jì)和測(cè)試。這對(duì)于芯片設(shè)計(jì)人員和測(cè)試工程師來(lái)說(shuō)都是一個(gè)新的挑戰(zhàn)。是德科技作為專業(yè)的測(cè)試方案提供商,也提供了從仿真到測(cè)試的完整方案。

1.仿真平臺(tái)

ADS2024是業(yè)界支持Chiplet D2D的建模仿真工具,ADS2024 Update 1.0版本已經(jīng)支持UCIe規(guī)范,能夠仿真測(cè)試的指標(biāo)包括:眼高,眼寬,BER,VTF等。

2.物理層測(cè)試平臺(tái)

在高速接口的物理層測(cè)試方面,是德科技也提供了從發(fā)送,信道到接收端的測(cè)試方案。

3.On-wafer測(cè)試

對(duì)On-wafer測(cè)試,是德科技也與合作伙伴一起推出針對(duì)Chiplet晶圓和硅光的On-Wafer測(cè)試平臺(tái)。

Chiplet技術(shù)儼然已經(jīng)成為了一種重要的芯片設(shè)計(jì)趨勢(shì)。

想象一下,未來(lái)我們可以像搭積木一樣,輕松地構(gòu)建各種功能強(qiáng)大、性能卓越的芯片,滿足不同應(yīng)用的需求。Chiplet不僅是一種制造方式,更是一種思維方式,讓我們能夠以更加靈活、創(chuàng)新的方式來(lái)構(gòu)建未來(lái)的芯片世界。讓我們一起期待,Chiplet技術(shù)如何繼續(xù)推動(dòng)科技的進(jìn)步,引領(lǐng)我們進(jìn)入更加美好的未來(lái)!

關(guān)于是德科技

是德科技(NYSE:KEYS)啟迪并賦能創(chuàng)新者,助力他們將改變世界的技術(shù)帶入生活。作為一家標(biāo)準(zhǔn)普爾 500 指數(shù)公司,我們提供先進(jìn)的設(shè)計(jì)、仿真和測(cè)試解決方案,旨在幫助工程師在整個(gè)產(chǎn)品生命周期中更快地完成開(kāi)發(fā)和部署,同時(shí)控制好風(fēng)險(xiǎn)。我們的客戶遍及全球通信、工業(yè)自動(dòng)化、航空航天與國(guó)防、汽車、半導(dǎo)體和通用電子等市場(chǎng)。我們與客戶攜手,加速創(chuàng)新,創(chuàng)造一個(gè)安全互聯(lián)的世界。

-

芯片

+關(guān)注

關(guān)注

454文章

50444瀏覽量

421922 -

晶圓

+關(guān)注

關(guān)注

52文章

4850瀏覽量

127809 -

gpu

+關(guān)注

關(guān)注

28文章

4703瀏覽量

128714 -

chiplet

+關(guān)注

關(guān)注

6文章

418瀏覽量

12560

原文標(biāo)題:積木造芯片?Chiplet 技術(shù)詳解

文章出處:【微信號(hào):是德科技KEYSIGHT,微信公眾號(hào):是德科技KEYSIGHT】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

IMEC組建汽車Chiplet聯(lián)盟

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺(tái)

國(guó)產(chǎn)半導(dǎo)體新希望:Chiplet技術(shù)助力“彎道超車”!

射頻技術(shù)有哪些優(yōu)勢(shì)和劣勢(shì)

西門子EDA創(chuàng)新解決方案確保Chiplet設(shè)計(jì)的成功應(yīng)用

藍(lán)鵬測(cè)控的激光測(cè)徑儀有哪些技術(shù)優(yōu)勢(shì)

Chiplet是否也走上了集成競(jìng)賽的道路?

什么是Chiplet技術(shù)?

Chiplet技術(shù)對(duì)英特爾和臺(tái)積電有哪些影響呢?

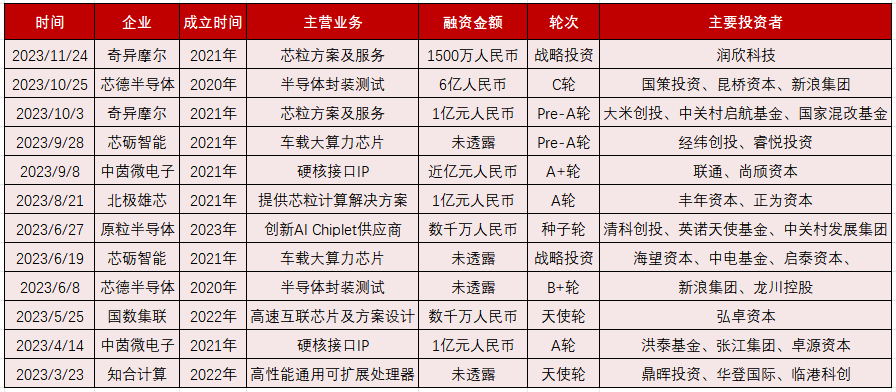

2023年Chiplet發(fā)展進(jìn)入新階段,半導(dǎo)體封測(cè)、IP企業(yè)多次融資

Chiplet成大芯片設(shè)計(jì)主流方式,開(kāi)啟IP復(fù)用新模式

什么是Chiplet技術(shù)?Chiplet技術(shù)有哪些優(yōu)缺點(diǎn)?

芯原股份募資18億,投向AIGC及智慧出行Chiplet領(lǐng)域

先進(jìn)封裝 Chiplet 技術(shù)與 AI 芯片發(fā)展

Chiplet技術(shù)有哪些優(yōu)勢(shì)

Chiplet技術(shù)有哪些優(yōu)勢(shì)

評(píng)論