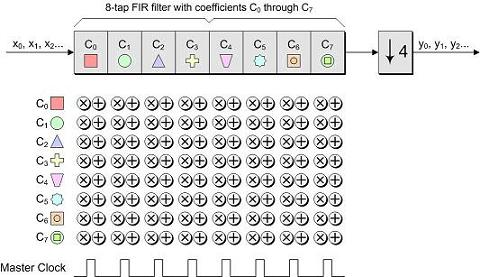

多相濾波器的基本概念是把FIR濾波器分割成若干較小的單元,然后組合這些單元的結果。首先,讓我們考慮一個基于常規(guī)8抽頭FIR濾波器的抽取子系統(tǒng)的符號表示,如圖11所示(為了使用這些例子,我們假設抽取因子為M = 4 )。

圖11 基于傳統(tǒng)的8抽頭FIR濾波器的抽取器的符號表示

現(xiàn)在讓我們假設主時鐘正在以某一頻率fHz運行。像往常一樣,在濾波操作之后任何不要的樣本將被丟棄,但這樣做是低效率的,因為這意味著是以完全的時鐘頻率在進行濾波。用另一種方式來看這種操作,即在每個時鐘時刻,每個抽頭級執(zhí)行乘法和加運算。

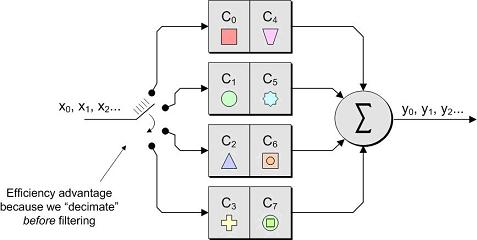

相比多相實現(xiàn)的情況,我們可以將原來的8抽頭FIR濾波器分為四個2抽頭子濾波器,如圖12所示。

圖12 基于4 × 2抽頭多相濾波器的抽取器的符號表示

假設同樣的主時鐘以f Hz的頻率運行,我們可以想象輸入數(shù)據(jù)流被送入一個旋轉開關(當然,這可用標準的邏輯技術來實現(xiàn))。第一個數(shù)據(jù)值送入第一個子濾波器;第二個數(shù)據(jù)值送入第二個子濾波器;第三個數(shù)據(jù)值送入第三個子濾波器;第四個數(shù)據(jù)值送入第四個子濾波器。然后,我們進行“循環(huán)”操作,以便第五個數(shù)據(jù)值送入第一個子濾波器;第六個數(shù)據(jù)值送入第二個子濾波器;等等。

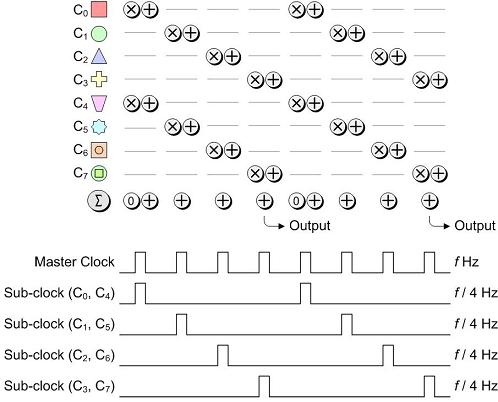

使用子濾波器減少了可能的飽和/溢出(發(fā)生任何飽和/溢出通常只需要在最后的函數(shù)求和時進行處理)。另外,使用子濾波器具有一個直接有效的優(yōu)點,因為在執(zhí)行濾波操作之前,我們有效地“抽取”了數(shù)據(jù)。這也意味著,我們的四個子濾波器中的每個都能有效地以F ÷ 4Hz的頻率運行,如圖13所示。

圖13 4 × 2抽頭多相濾波器的運行情況

除了任何寄存器和一般用途的邏輯,常規(guī)8抽頭FIR濾波器中的每個抽頭包含一個乘法器和一個加法器,當然為我們提供了總共8個乘法器和8個加法器。濾波器之后需要一些額外的邏輯,以便丟棄任何不想要的樣本。

同樣,在我們最初的4 × 2抽頭多相實現(xiàn)中的每一個抽頭含有一個乘法器和一個加法器,再次為我們提供了總共8個乘法器和8個加法器。在多相實現(xiàn)中,需要實現(xiàn)“旋轉開關”送入濾波器的邏輯數(shù)量大約相當于在常規(guī)8抽頭FIR濾波器中丟棄不要的樣本所需的邏輯。

當然,多相實現(xiàn)還需要一些額外的邏輯和一個加法器累加來自四個子濾波器的結果。因此,最終的結果是,最初的多相實現(xiàn)需要比傳統(tǒng)的8抽頭FIR濾波器更多一點的邏輯。

然而,對于傳統(tǒng)的8位FIR濾波器,在每個時鐘都要執(zhí)行8次乘和8次加。相比最初的多相實現(xiàn)的情況,在任何主時鐘時刻,只有一個子濾波器是工作的。由于在這個例子中每個子濾波器含有兩個抽頭,這意味著這個功能的濾波器部分在每個時鐘只進行兩次乘法和兩次加法。

當然,從四個子濾波器收集結果的求和功能還必須在每個主時鐘進行加(在每4時鐘周期開始時,這個累加器清零;它從四個子濾波器收集結果; 在每4時鐘周期結束時,它產(chǎn)生一個新的值)。

這意味著,最初的多相實現(xiàn)的每個子濾波器有效地以常規(guī)8抽頭FIR濾波器1/ 4的頻率運行。反過來,這意味著最初多相實現(xiàn)只在每個主時鐘進行兩次乘法和三次加法(包括加法器的加操作),從而大大節(jié)省了功耗。

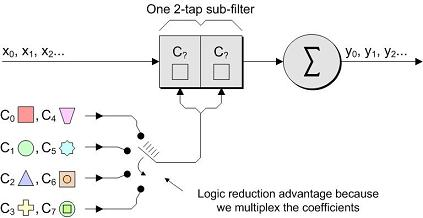

此外,在最初的多相實現(xiàn)中,由于四個子濾波器的每個只用了1/4的時間,這意味著在任何特定時間,我們實際上只需要其中的一個,這使我們更加完善了實現(xiàn)方法,如圖14所示。

圖14 更完善的基于多相濾波器的抽取器實現(xiàn)方案

在這種情況下,我們采用了單一的2抽頭子濾波器,每個抽頭含有乘法器和加法器。在每個主時鐘,我們選擇合適的系數(shù)對。每一個抽頭需要額外的寄存器和用于維護的邏輯,但與減少的乘法器和加法器相比,與我們的最初多相實現(xiàn)相比,這是微不足道的。

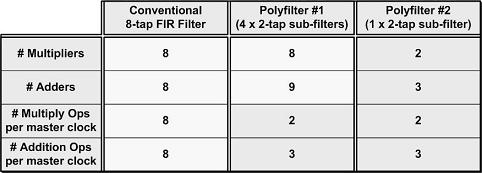

當然,在我們原來的多相實現(xiàn)中,我們?nèi)匀灰诿總€主時鐘時刻執(zhí)行兩次乘法和三次加法,。這些抽取實現(xiàn)例子的總結如表1所示。

表1抽取實現(xiàn)實例的總結

利用多相FIR濾波器進行內(nèi)插

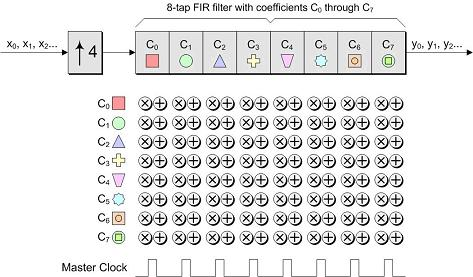

現(xiàn)在讓我們來考慮內(nèi)插的情況。首先讓我們先考慮一個基于常規(guī)8抽頭FIR濾波器的內(nèi)插子系統(tǒng)的符號表示,如圖15所示。

圖15傳統(tǒng)的基于8抽頭FIR濾波器的內(nèi)插器的符號表示

針對這些例子的用途,我們假設內(nèi)插因子為L = 4,主時鐘頻率為FHz。正如先前所討論的,向上采樣(插入零值樣本的過程)發(fā)生在濾波操作之前。

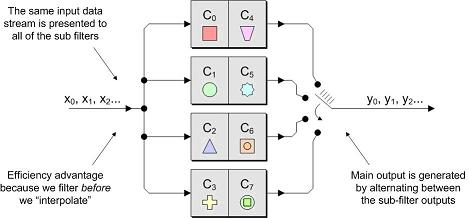

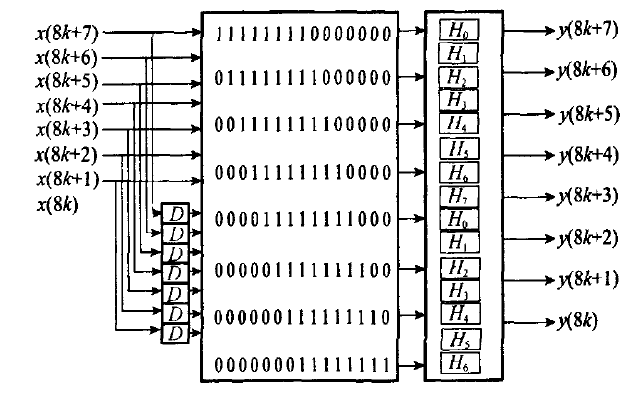

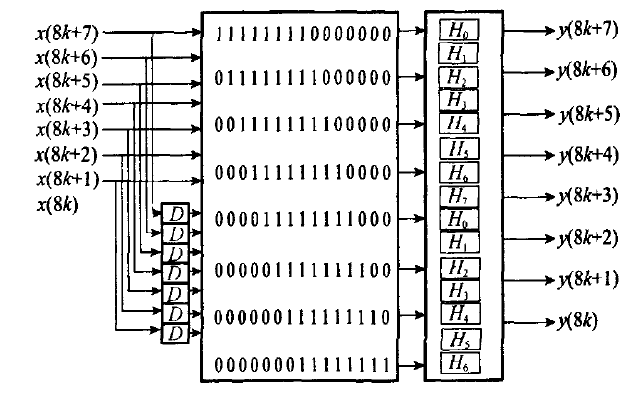

現(xiàn)在讓我們來考慮一個最初的多相實現(xiàn),我們原來的8抽頭FIR濾波器被分成四個2 抽頭子濾波器,如圖16所示。

圖16 基于4 × 2抽頭多相濾波器的內(nèi)插器的符號表示

在這種情況下,相同的輸入數(shù)據(jù)流面向所有的四個子濾波器,在子濾波器輸出之間輪流產(chǎn)生主輸出數(shù)據(jù)流。最終的結果是,多相實現(xiàn)含有如同我們的常規(guī)8抽頭FIR濾波器相同數(shù)量的乘法器和加法器。然而,因為在內(nèi)插之前進行了濾波,子濾波器只需要以1 / 4的主時鐘頻率運行,從而大大節(jié)省了功耗(這里主時鐘用于子濾波器輸出之間的采樣)。

此外,多相實現(xiàn)不需要向上采樣(零值插入)的邏輯。當然,我們可以用完全運行于主時鐘頻率和復用系數(shù)的單個2抽頭子濾波器取代原來的多相濾波器實現(xiàn)。

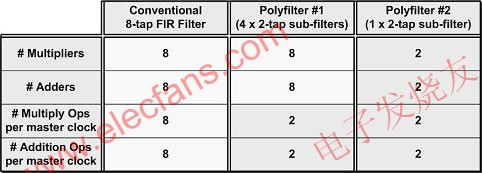

內(nèi)插實現(xiàn)的這些例子的總結見表2 。

表2內(nèi)插實現(xiàn)實例的總結

總結

所有這一切都意味著,多相基于濾波器的抽取器、內(nèi)插器和重采樣功能是非常適合用更小的中檔FPGA來實現(xiàn),如Lattice半導體公司的擁有SERDES功能的LatticeECP3系列,它具有高性能的sysDSP模塊。它的特點是有dual-slice結構,具有級聯(lián)/鏈接DSP slice和模塊的功能,增強的DSP指令集使LatticeECP3系列能夠引人注目地用于范圍廣泛的數(shù)字信號處理的應用,包括那些需要傳統(tǒng)的FIR和基于多相的濾波功能。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

601999 -

濾波器

+關注

關注

160文章

7749瀏覽量

177729 -

多相濾波

+關注

關注

0文章

10瀏覽量

10309

原文標題:FPGA進行多路并行插值濾波(多相濾波)的實現(xiàn)原理

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

如何用中檔FPGA實現(xiàn)多相濾波器?

如何實現(xiàn)基于多相濾波的數(shù)字接收機的FPGA?

基于DSP Builder的CIC梳狀濾波器該怎么設計?

如何設計基于中檔FPGA多相濾波器?

基于FPGA的多相濾波實現(xiàn)

基于多相濾波的數(shù)字接收機的FPGA實現(xiàn)

高速并行成型濾波器的FPGA實現(xiàn)方法

如何使用FPGA實現(xiàn)實現(xiàn)高速并行FIR濾波器

如何使用FPGA實現(xiàn)實現(xiàn)高速并行FIR濾波器

如何使用FPGA實現(xiàn)圖像的中值濾波算法

FPGA進行多路并行插值濾波(多相濾波)的實現(xiàn)原理

FPGA進行多路并行插值濾波(多相濾波)的實現(xiàn)原理

評論