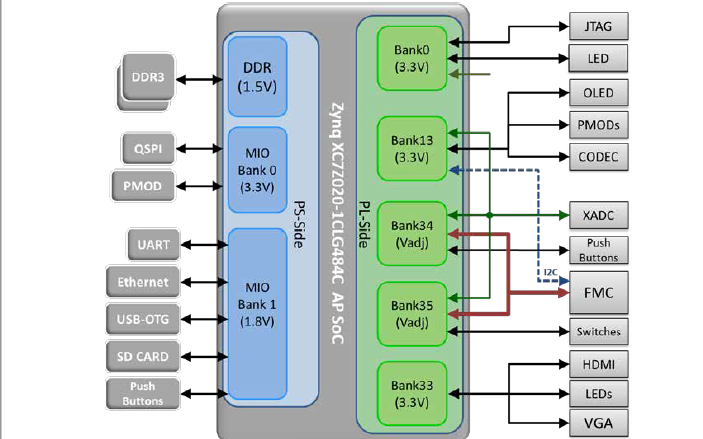

zedboard可以將邏輯資源和軟件分別映射到PS和PL中,這樣可以實現獨一無二和差異換的系統功能,主要分為兩大部分,處理系統和可編程邏輯。以及二者之間的互聯特性。這篇筆記主要記錄zedboard的大體架構。

1. 處理系統(PS)

應用處理單元(APU)

存儲器接口

I/O外設,包括靜態存儲器和Flash存儲器接口,可以通過共享一個54引腳的多路復用io(MIO)

互聯,也可以擴展訪問PL中的IO

2. 可編程邏輯(PL)

PS和PL使用了大量的借口和信號可以滿足幾乎所有的連接。

系統的啟動

zynq的啟動過程包含多個階段,啟動過程至少包含啟動rom和第一級的啟動引導代碼( first-stage boot loader FSBL ),t同時包含可啟動的rom,這個rom用戶不可修改,完成了啟動rom之后,然后執行FSLB 。復位之后,zynq可以自動的從外部的引導設備中啟動設備,根據需要,用戶可以配置zynq的PS和PL,可以使用jtag借口,用于啟動時的調試。

在使用過程中,可以選擇性的關閉PL一側的電源,以降低功耗,當然也可以降低PS內的時鐘。

處理系統的PS特性

1. 應用處理單元(APU)

arm 雙核Cortex-A9多核處理器( ARM V7 )

系統特性:從PL和PS的加速器一致性端口(ACP),帶有校驗的256K的OCM,

2. 存儲器接口

DDR控制權,四-SPI控制器,并且應當注意的是,下面的存儲器可以作為基本的啟動設備:

NAMD控制器,并行SRAM/NOR控制器

3. IO特性

提供了標準的io、工業標準接口。

GPIO,

3模式的以太網控制器,

USB控制器,可以作為主設備或者OTG

SD/SDIO控制器,兩個,可以作為基本的啟動設備,支持sd 2.0規范,

SPI控制器:四線總線,MOSI,MISO,SCLK,SS,支持全雙工操作,

CAN控制器(兩個)

UART控制器兩個

i2c控制器(兩個)

可編程邏輯PL特性

可配置邏輯塊(CLB)

36KB的Bram,雙端口,最多72位寬度,可編程fifo邏輯,

時鐘管理

可配置的io

模數轉換特性(XADC)

互聯特性

1. 基于AXI高性能數據通路開關的PS互聯

OCM互聯,提供來自中央互聯和PL的,用于對256KB存儲器的訪問,

CPU和ACP的接口,

中央互聯,

中央互聯是64位的,將IOP和DMA控制連接到DDR存儲器控制器,片上系統RAM的接口開關。將以太網、usb、和sd/sdio控制器內的本地DMA單元連接到中央互聯,將PS內的主設備連接到IOP。

2. PS-PL接口,包含所有PL設計者的可用信號,可以基于PL的功能和PS集結在 一起。

功能接口,包含AXI互聯,用于大多數的IO外設、中斷,DMA控制流、時鐘和調試接口的擴展MIO接口,

-

Zedboard

+關注

關注

45文章

70瀏覽量

49190

發布評論請先 登錄

相關推薦

玩轉賽靈思Zedboard開發板(3):基于Zynq PL的流水燈

PYNQ案例(一):ZYNQ的PL與PS開發

Linux下如何通過UIO監控PL給到PS的中斷

玩轉賽靈思Zedboard開發板(2):最簡單的測試工程

如何在使用PS和PL時使用SDK生成啟動映像和程序閃存?

怎么在zedboard上測試DDR讀寫?

zynq 7020 PS和zynq PL是如何通話的?

一步一步學ZedBoard:使用PL做流水燈(完整工程文件下載)

Vivado+Zedboard之入門實例精選

一步一步學ZedBoard Zynq(二):使用PL做流水燈

基于ZedBoard的SCA架構的設計原理

Zedboard開發板硬件用戶手冊的資料免費下載

zedboard的大體架構介紹(PS、PL、硬件互聯)

zedboard的大體架構介紹(PS、PL、硬件互聯)

評論