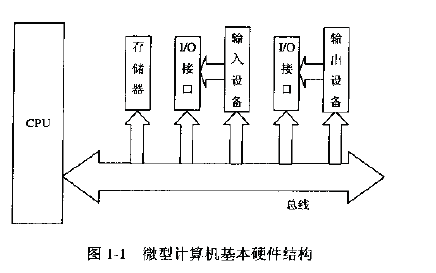

嵌入式設計是個龐大的工程,今天就說說硬件電路設計方面的幾個注意事項,首先,咱們了解下嵌入式的硬件構架。

我們知道,CPU是這個系統的靈魂,所有的外圍配置都與其相關聯,這也突出了嵌入式設計的一個特點硬件可剪裁。在做嵌入式硬件設計中,以下幾點需要關注。

第一、電源確定

電源對于嵌入式系統中的作用可以看做是空氣對人體的作用,甚至更重要:人呼吸的空氣中有氧氣、二氧化碳和氮氣等但是含量穩定,這就相當于電源系統中各種雜波,我們希望得到純凈和穩定符合要求的電源,但由于各種因素制約,只是我們的夢想。這個要關注兩個方面:

a、電壓

嵌入式系統需要各種量級的電源比如常見的5v、3.3v、1.8v等,為盡量減小電源的紋波,在嵌入式系統中使用LDO器件。如果采用DCDC不僅個頭大,其紋波也是一個很頭疼的問題。

b、電流

嵌入式系統的正常運行不但需要穩定足夠的電源,還要有足夠的電流,因此在選擇電源器件的時候需要考慮其負載,我設計時一般留有30%的余量。

如果是多層板,電源部分在layout的時候需電源分割,這時需要注意分割路徑,盡量將一定量的電源放置在一起。如果是雙面板,則走線寬度需要注意,在板子允許的情況下盡量加寬。合適的退耦電容盡量靠近電源管腳。第二、 晶振確定

晶振相當于嵌入式系統的心臟,其穩定與否直接關系其運行狀態和通訊性能。常見的振有無源晶振,有源晶振,首先要確定其振蕩頻率,其次要確定晶振類型。

a、無源晶振

其匹配電容和匹配電阻的選擇,這部分一般依據參考手冊。在單片機設計中,經常使用插件晶振配合瓷片電容。在ARM中,為了減少空間和便于布線,經常使用四角無源晶振配合貼片電容。雖然我們對于固定晶振的匹配電路比較熟悉,但是為了達到萬無一失,還是要看參考手冊確定電容大小,是否需要匹配電阻等細節。

b、有源晶振

具有更好的更準確的時鐘信號,但是相比之下,比無緣晶振價格高,因此這也是在硬件電路設計中需要關注的成本。

在做電路板設計時需要注意晶振走線盡量靠近芯片,關鍵信號遠離時鐘走線。在條件允許的情況下增加接地保護環。如果是多層板,也要講關鍵信號遠離晶振的走線。第三、 預留測試IO口在嵌入式調試階段,在管腳資源豐富的情況下,我通常預留一個IO口連接led或者喇叭,為下一步軟件的編寫做鋪墊。在嵌入式系統運行過程中適當控制該IO接口,從而判斷系統是否正常運行。第四、外擴存儲設備

一個嵌入式系統如果有電源、晶振和CPU,那么這就是我們熟悉的最小系統。如果該嵌入式系統需要運行大點的操作系統,那么不但需要CPU具有 MMU,CPU還需要外接SDRAM和NANDFLASH。如果該cpu具有SDRAM和NANDFLASH控制器,那么在硬件設計上不用過多的考慮地址線的使用。如果沒有相關的控制器,那么需要注意地址線的使用。

這部分在LAYOUT的時候是一個重點,究其原因就是要使相關信號線等長以確保信號的延時相等,時鐘和DQS的差分信號線走線。在布線的時候各種布線技巧需要綜合使用,例如與cpu對稱分布,菊花鏈布線、T型布線,這都需要依據內存的個數多少來進行選擇,一般來說個數越多,布線越復雜,但是知道其關鍵點,一切迎刃而解。第五、功能接口第六、屏幕

這個功能之所以單獨列出來,是由于其可有可無。如果一個嵌入式系統只是作為一個連接器連接外圍設備模塊,通過相關接口連接到電腦主機或者直接掛在網絡上,那么屏幕就不需要了。但是如果做出來的是一個消費類產品,與用戶交互頻繁,這就不得不嘮叨幾句。

電容屏幕是嵌入式屏幕的首選,在電路設計中需要注意觸屏連接線和顯示屏連接線的布局。在走線的過程中盡量短的靠近主控cpu,同時注意配對信號走差分線,RGB控制信號走等長。各種信號走線間距遵循3W規則,避免相互干擾。 在屏幕的設計中,一定要確保功率和防止干擾,以防屏幕閃屏和花屏現象的出現。

-

嵌入式

+關注

關注

5068文章

19014瀏覽量

303229

原文標題:嵌入式硬件電路設計六大基本功

文章出處:【微信號:weixin21ic,微信公眾號:21ic電子網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

嵌入式硬件電路設計的六個基礎知識

嵌入式系統軟硬件基礎知識大全

6個嵌入式硬件電路設計的基礎知識

嵌入式的基礎知識主要包含什么內容

嵌入式系統教程之嵌入式硬件系統設計與應用實例資料免費下載

嵌入式系統基礎知識總結

嵌入式系統基礎知識題庫

嵌入式硬件電路設計基礎知識梳理

嵌入式硬件電路設計基礎知識梳理

評論