格雷碼屬于可靠性編碼,是一種錯(cuò)誤最小化的編碼方式。因?yàn)椋m然自然二進(jìn)制碼可以直接由數(shù)/模轉(zhuǎn)換器轉(zhuǎn)換成模擬信號(hào),但在某些情況,例如從十進(jìn)制的3轉(zhuǎn)換為4時(shí)二進(jìn)制碼的每一位都要變,能使數(shù)字電路產(chǎn)生很大的尖峰電流脈沖。而格雷碼則沒(méi)有這一缺點(diǎn),它在相鄰位間轉(zhuǎn)換時(shí),只有一位產(chǎn)生變化。它大大地減少了由一個(gè)狀態(tài)到下一個(gè)狀態(tài)時(shí)邏輯的混淆。由于這種編碼相鄰的兩個(gè)碼組之間只有一位不同,因而在用于方向的轉(zhuǎn)角位移量-數(shù)字量的轉(zhuǎn)換中,當(dāng)方向的轉(zhuǎn)角位移量發(fā)生微小變化(而可能引起數(shù)字量發(fā)生變化時(shí),格雷碼僅改變一位,這樣與其它編碼同時(shí)改變兩位或多位的情況相比更為可靠,即可減少出錯(cuò)的可能性。

格雷碼是一種絕對(duì)編碼方式,典型格雷碼是一種具有反射特性和循環(huán)特性的單步自補(bǔ)碼,它的循環(huán)、單步特性消除了隨機(jī)取數(shù)時(shí)出現(xiàn)重大誤差的可能,它的反射、自補(bǔ)特性使得求反非常方便。

由于格雷碼是一種變權(quán)碼,每一位碼沒(méi)有固定的大小,很難直接進(jìn)行比較大小和算術(shù)運(yùn)算,也不能直接轉(zhuǎn)換成液位信號(hào),要經(jīng)過(guò)一次碼變換,變成自然二進(jìn)制碼,再由上位機(jī)讀取。

典型格雷碼是一種采用絕對(duì)編碼方式的準(zhǔn)權(quán)碼,其權(quán)的絕對(duì)值為2^i-1(設(shè)最低位i=1)。

格雷碼的十進(jìn)制數(shù)奇偶性與其碼字中1的個(gè)數(shù)的奇偶性相同。

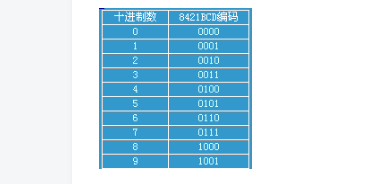

8421碼轉(zhuǎn)格雷碼

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY B2G IS

GENERIC(n:INTEGER :=4);

PORT(

norm : IN STD_LOGIC_VECTOR(n-1 DOWNTO 0);

grey : OUT STD_LOGIC_VECTOR(n-1 DOWNTO 0)

);

END B2G;

ARCHITECTURE behave OF B2G IS

SIGNAL temp_normal : STD_LOGIC_VECTOR(n-1 DOWNTO 0);

SIGNAL temp_grey : STD_LOGIC_VECTOR(n-1 DOWNTO 0);

BEGIN

PROCESS(norm)

BEGIN

temp_normal 《= norm;

temp_grey(n-1) 《= temp_normal(n-1)

FOR i IN n-2 DOWNTO 0 LOOP

temp_grey(i) 《= temp_normal(i+1) xor temp_normal(i);

END LOOP;

grey 《= temp_grey;

END PROCESS;

END behave;

數(shù)碼管顯示器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY seg7_1 IS

PORT(

A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

B:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END seg7_1

ARCHITECTURE seg7_1 _arch OF seg7_1 IS

BEGIN

PROCESS(A)

BEGIN

CASE A IS

WHEN“0000”=》B《=“1111110”; --0

WHEN“0001”=》B《=“0110000”; --1

WHEN“0010”=》B《=“1101101”; --2

WHEN“0011”=》B《=“1111001”;--3

WHEN“0100”=》B《=“0110011”;--4

WHEN“0101”=》B《=“1011011”;--5

WHEN“0110”=》B《=“1011111”; --6

WHEN“0111”=》B《=“1110000”; --7

WHEN“1000”=》B《=“1111111”; --8

WHEN“1001”=》B《=“1111011”; --9

WHEN OTHERS =》B《=“0000000”;

END CASE;

END PROCESS;

END;

四人多數(shù)表決器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY biaojueqi IS

PORT(

A3,A2,A1,A0:IN STD_LOGIC;

Y :OUT STD_LOGIC);

END biaojueqi;

ARCHITECTURE behave OF biaojueqi IS

SIGNAL comb :STD_LOGIC_VECTOR(3 DOWNTO 0);

signal d: STD_LOGIC_VECTOR(15 DOWNTO 0);

BEGIN

comb《=A3&A2&A1&A0;

PROCESS(comb)

BEGIN

CASE comb IS

WHEN“0111”=》Y《=’1’;

WHEN“1011”=》Y《=’1’;

WHEN“1101”=》Y《=’1’;

WHEN“1110”=》Y《=’1’;

WHEN“1111”=》Y《=’1’;

WHEN OTHERS =》Y《=‘0’;

END CASE;

END PROCESS;

END behave;

格雷碼轉(zhuǎn)和8421碼的相互轉(zhuǎn)換

用與非門(mén)74LS00和異或門(mén)74LS86設(shè)計(jì)一可逆的4位碼變換器 設(shè)計(jì)要求:在控制信號(hào)C=1時(shí),將8421碼轉(zhuǎn)換為格雷碼;C=0時(shí),將格雷碼轉(zhuǎn)換為8421碼;寫(xiě)出設(shè)計(jì)步驟,列出碼變換關(guān)系真值表并畫(huà)出邏輯圖,并用multisim進(jìn)行仿真

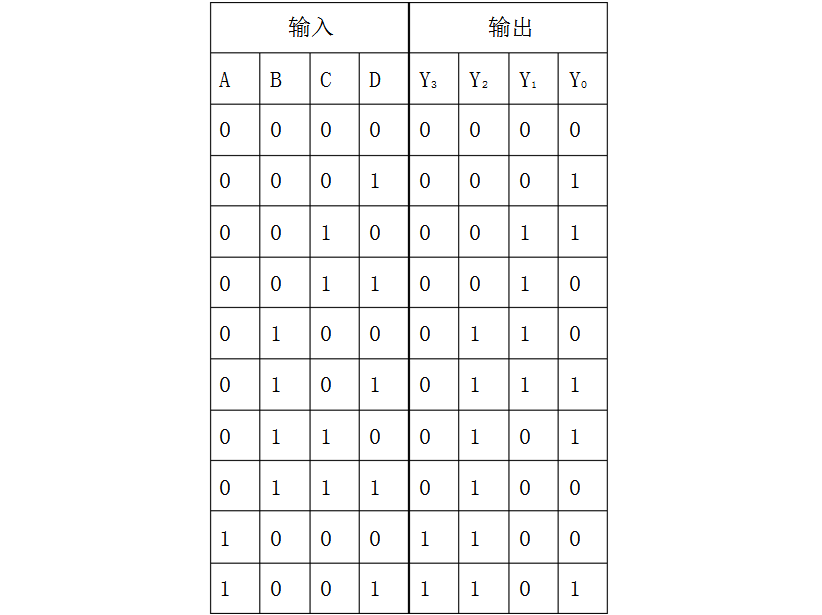

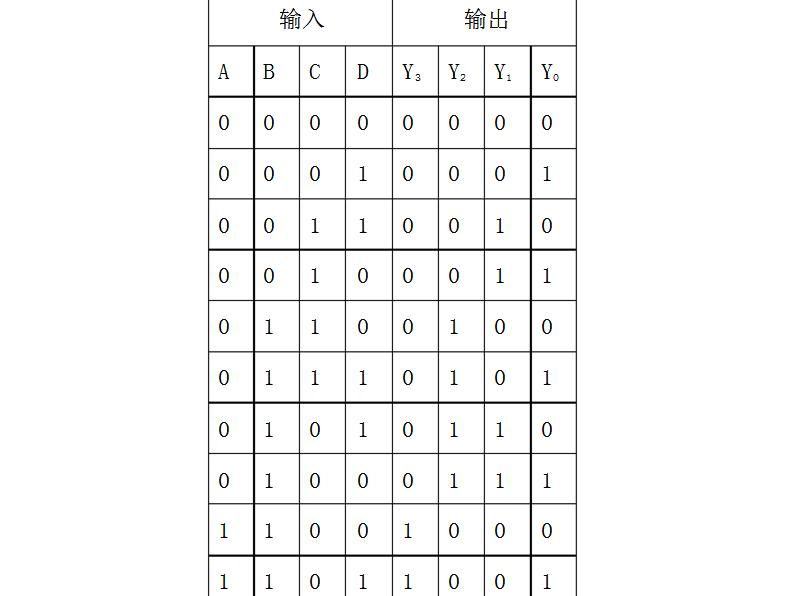

解:根據(jù)組合邏輯電路的設(shè)計(jì)方法設(shè)輸入變量分別為A,B,C,D輸出變量分別為Y3,Y2,Y1,Y0;高電平用“1”表示,低電平用“0”表示。 (1)列出真值表

當(dāng)C=1時(shí)將8421碼轉(zhuǎn)換為格雷碼

當(dāng)C=0時(shí)將格雷碼轉(zhuǎn)換為8421碼

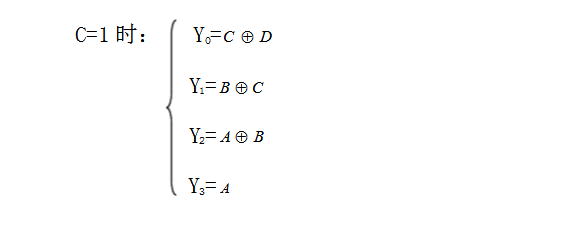

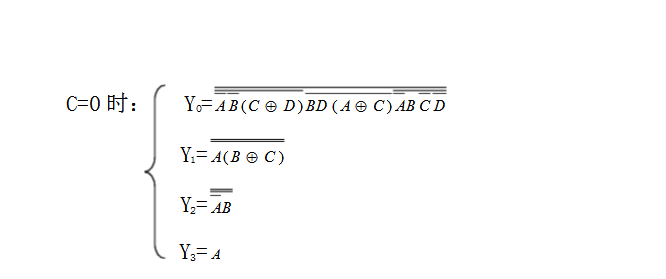

(2)根據(jù)真值表寫(xiě)出邏輯函數(shù)表達(dá)式并化簡(jiǎn)

(3)根據(jù)化簡(jiǎn)后的邏輯函數(shù)表達(dá)式設(shè)計(jì)出實(shí)現(xiàn)該邏輯功能的數(shù)字邏輯電路

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8639瀏覽量

146894 -

格雷碼

+關(guān)注

關(guān)注

2文章

34瀏覽量

13178 -

8421碼

+關(guān)注

關(guān)注

1文章

8瀏覽量

4032

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

什么是格雷碼

常用編碼(BCD編碼、余3碼、格雷反射碼、奇偶校驗(yàn)碼)

格雷碼的規(guī)則和應(yīng)用問(wèn)題?

8421BCD碼與二進(jìn)制原碼的相互轉(zhuǎn)換

二進(jìn)制代碼與格雷碼相互轉(zhuǎn)換

格雷碼簡(jiǎn)介及格雷碼與二進(jìn)制的轉(zhuǎn)換程序

格雷碼運(yùn)算研究

循環(huán)格雷碼VHDL源程序

格雷碼辨析

余3碼至8421BCD碼的轉(zhuǎn)換_8421BCD碼轉(zhuǎn)換成余3碼

如何把二進(jìn)制轉(zhuǎn)換為格雷碼?格雷碼是如何判斷讀空寫(xiě)滿(mǎn)呢?

格雷碼轉(zhuǎn)和8421碼的相互轉(zhuǎn)換

格雷碼轉(zhuǎn)和8421碼的相互轉(zhuǎn)換

評(píng)論