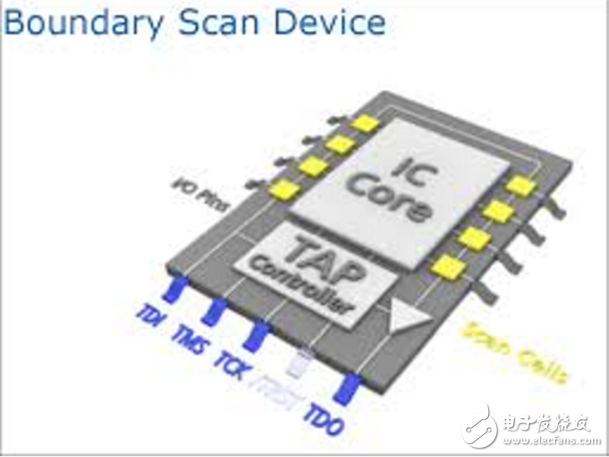

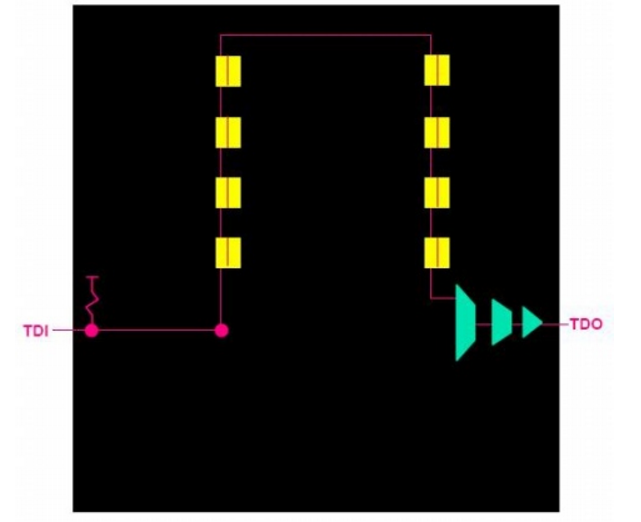

在現代電子應用系統中 ,印刷電路板越來越復雜多層板的設計越來越普遍,大量使用各種表貼元件和B GA (ball grid array) 封裝元件,元器件的管腳數和管腳密度不斷提高,使用萬用表、示波器測試芯片的傳統“探針”方法已不能滿足要求。在這種背景下,早在 20 世紀 80 年代,聯合測試行動組(joint testaction group,簡稱 J TA G) 起草了邊界掃描測試( boundary2scan testing ,簡 寫 BST) 規 范,后 來 在1990 年被批準為 IEEE 標準 1149. 121990 規定,簡稱JTAG標準。該標準規定了進行邊界掃描測試所需要的硬件和軟件。自從1990 年批準后,IEEE 分別于1993 年和1995 年對該標準作了補充,形成了現在使用的IEEE1149.1a-1993 和IEEE1149.1b-1994。JTAG 主要應用于:電路的邊界掃描測試和可編程芯片的在線系統編程。

邊界掃描測試有兩大優點 :一個是方便芯片的故障定位,迅速準確地測試兩個芯片管腳的連接是否可靠,提高測試檢驗效率;另一個是,具有 JTAG接口的芯片,內置一些預先定義好的功能模式,通過邊界掃描通道來使芯片處于某個特定的功能模式,以提高系統控制的靈活性和方便系統設計。

現在,所有復雜的 IC 芯片幾乎都具有JTAG控制接口,JTAG控制邏輯簡單方便,易于實現。

邊界掃描技術的應用

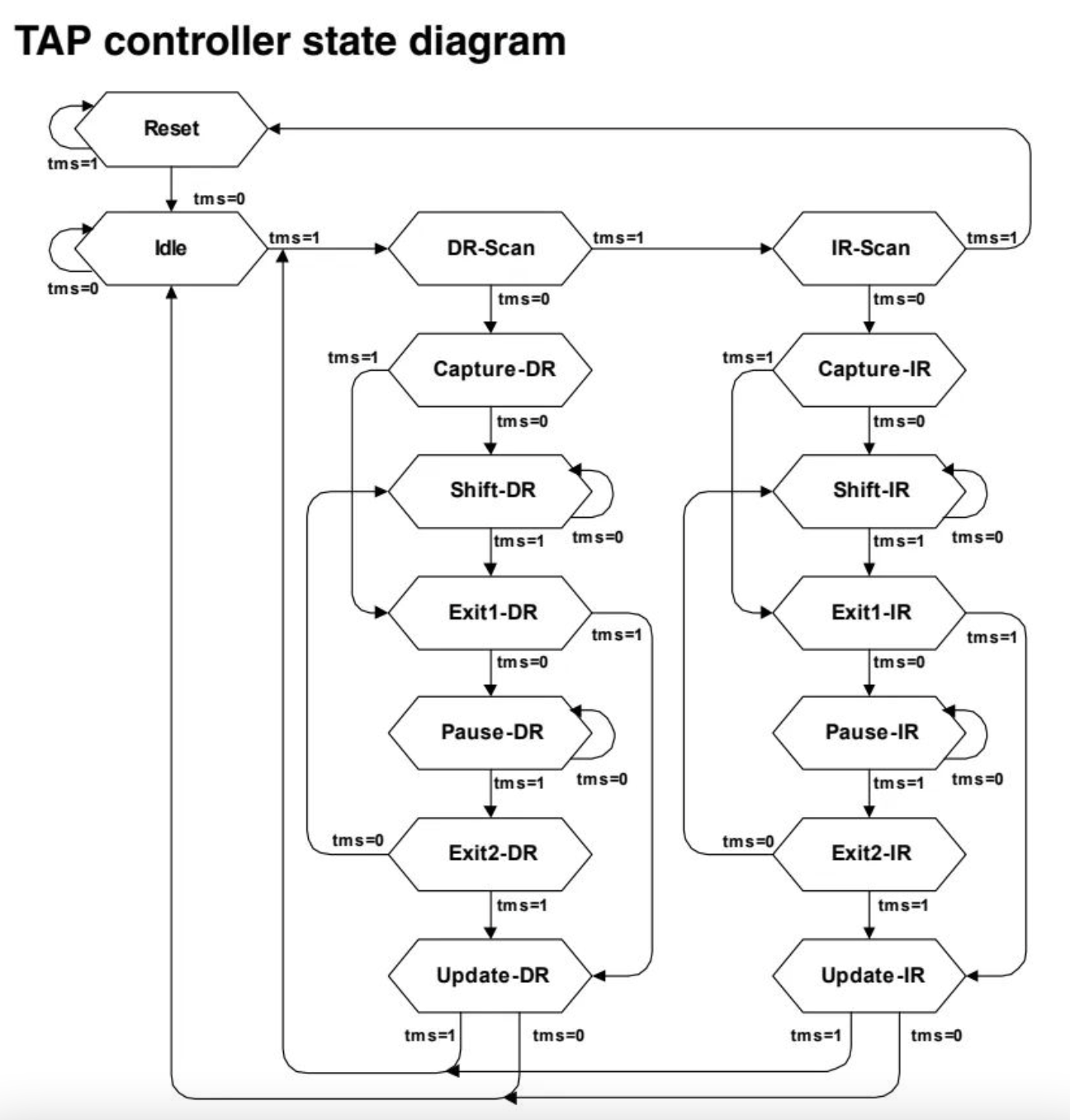

對于需要進行IC元件測試的設計人員來說,只要根據TA P控制器的狀態機,設計特定的控制邏輯,就可以進行IC元件的邊界掃描測試或利用JTA G接口使IC元件處于某個特定的功能模式。

Inter的PC I to PC I橋片21154,BGA封裝,共304個管腳,具有符合IEEE 114911標準的JTA G控制引腳。在設計的一個CompactPC I系統中,需要利用JTA G控制使其進入一種高阻模式(H IGHZ模式,這是IEEE 114911推薦的任選模式之一)。在這種模式下。芯片的所有輸出管腳都處于無效態即高阻態。要使21154進入H IGHZ,必須將位碼00101寫入指令寄存器,這時,邊界測試數據寄存器選擇的是旁通寄存器。

21154 的 JTA G 控制步驟

21154正常工作時,TM S持續為高電平或TRST=0。

控制21154進入JTA G H IGHZ狀態需要經過以下6個步驟:

(1)TRST=1。

(2)進入SH IFT IR狀態:在連續5個TCK(上升沿),使TM 3=01100,則進入SH IFT_IR狀態。

(3)將指令碼寫入指令寄存器:在SH IFT_IR狀態,通過TD I將00101寫入指令寄存器,需要5個時鐘周期。

(4)進入EX IT l IR狀態:在SH IFT_IR狀態的第5個TCK的上升沿(最后一個指令碼),使TM S=1,則進入EX IT l IR狀態。

(5)進入U pdate IR狀態:進入EX IT l IR狀態后,再使TM S=1,則進入U pdate IR狀態。

(6)進入Run Test?Idle狀態:進入U pdate IR狀態后,再使TM S=0,則進入Run Test?Idle狀態,此時,21154進入H IGHZ狀態。

21154的JTA G控制V erilog HDL代碼

說明:BeginJTA G_1是控制21154進入H IGHZ的觸發信號。低電平有效。

A lw ays

@ (BeginJTA G_ 1, Clk)

Begin

T rst 《 = ′0′

Jtag_ stste《 = s0;

Case (Jtag_ stste)

s0:

if (BeginJTA G_ 1= ′0′)

Begin

T rst《 = ′1′;

Tm s《 = ′0′;

Jtag_ stste《 = s1;

end

else begin

Jtag_ stste《 = s0;

end

s1:

Tm s《 = ′0′;

T id《 = ′0′;

Jtag_ stste《 = s2;

s2:

Tm s《 = ′1′;

T id《 = ′0′;

Jtag_ stste《 = s3;

s3:

Tm s《 = ′1′;

T id《 = ′0′;

Jtag_ stste《 = s4;

s4:

Tm s《 = ′0′;

T id《 = ′0′;

Jtag_ stste《 = s5;

s5:

Tm s《 = ′0′;

T id《 = ′0′;

Jtag_ stste《 = s6;

s6:

Tm s《 = ′0′;

T id《 = ′0′;

Jtag_ stste《 = s7;

s7:

Tm s《 = ′0′;

T id《 = ′0′;

Jtag_ stste《 = s8;

s8:

Tm s《 = ′0′;

T id《 = ′1′;

Jtag_ stste《 = s9;

s9:

Tm s《 = ′0′;

T id《 = ′0′;

Jtag_ stste《 = s10;

s10:

Tm s《 = ′1′;

T id《 = ′1′;

Jtag_ stste《 = s11;

s11:

Tm s《 = ′0′;

T id《 = ′0′;

Jtag_ stste《 = s12;

s12:

Tm s《 = ′0′;

T id《 = ′0′;

O thers:

end case

End

上述代碼,經過編譯、仿真,得到圖7所示JTA G控制時序波形。在設計的系統中,將上述V erilog HDL代碼經過編譯后生成目標文件,寫入A ltera公司的可編程邏輯芯片EPM 7128SLC84_7(在此芯片內還有其他邏輯),當BeginJTA G_1=0時,實現了控制21154進入JTA G高阻狀態。

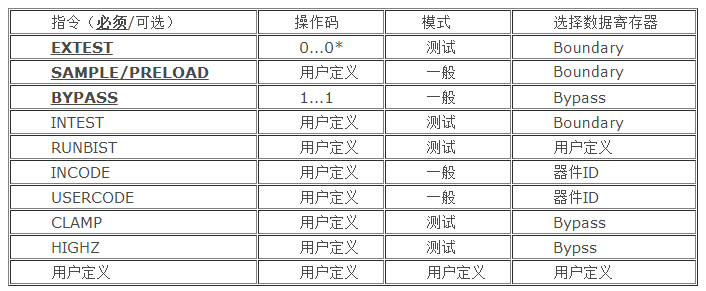

邊界掃描九大指令

Extest指令--強制指令

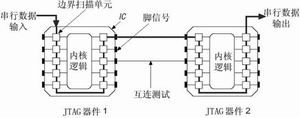

用于芯片外部測試,如互連測試

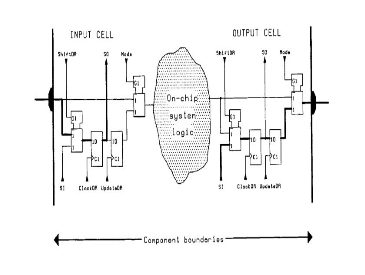

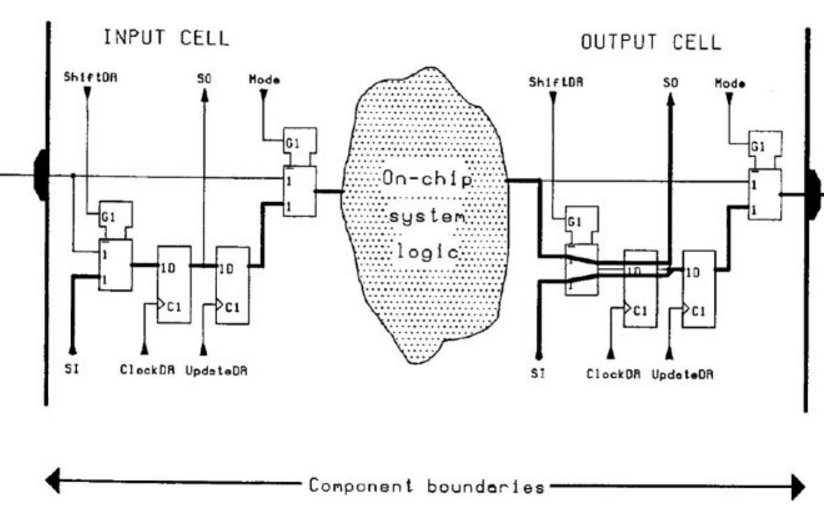

測試模式下的輸出管腳,由BSC update鎖存驅動(BSC注釋:寄存器的每一個單元分配給IC芯片的相應引腳,每一個獨立的單元稱為BSC(Boundary-Scan Cell)邊界掃描單元。)

BSC scan鎖存捕獲的輸入數據

移位操作,可以從TDI輸入測試激勵,并從TDO觀察測試響應。

在移位操作后,新的測試激勵存儲到BSC的update鎖存

原先EXTEST指令時強制為全“0”的,在IEEE 1149.1--2001中,這條強制取消了。選擇EXTEST指令時,IC工作在邊界掃描外部測試模式(external boundary-test mode),也就是說對IC的操作影響芯片的正常工作。選擇邊界掃描寄存器連通TDI和TDO。在這種指令下,可以通過邊界掃描輸出單元來驅動測試信號至其他邊界掃描芯片,以及通過邊界掃描輸入單元來從其他邊界掃描芯片接收測試信號。EXTEST指令是IEEE 1149.1標準的核心所在,在邊界掃描測試中的互連測試(interconnect test)就是基于這個指令的。

(該指令初始化外部電路測試,主要用于板級互連以及片外電路測試。EXTEST指令在Shift-DR狀態時將掃描寄存器BSR寄存器連接到TDI與TDO之間。在Capture-DR狀態時,EXTEST指令將輸入管腳的狀態在TCK的上升沿裝入BSR中。EXTEST指令從不使用移入BSR中的輸入鎖存器中的數據,而是直接從管腳上捕獲數據。在Update-DR狀態時,EXTEST指令將鎖存在并行輸出寄存器單元中的數據在TCK的下降沿驅動到對應的輸出管腳上去。)

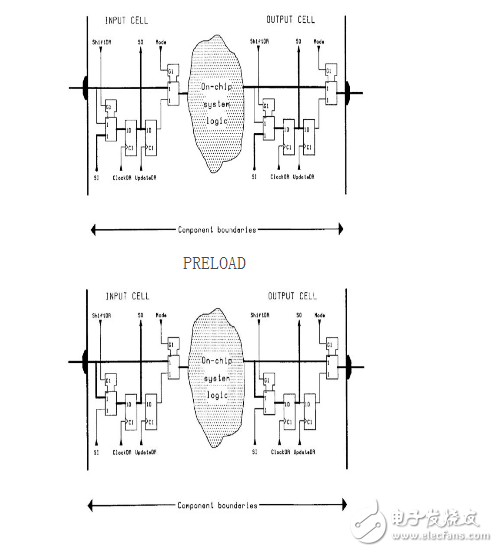

Sample/Preload指令--強制指令

在進入測試模式前對BSC進行預裝載

輸入輸出管腳可正常操作

輸入管腳數據和內核輸出數據裝載到BSC的scan鎖存中。

移位操作,可以從TDI輸入測試激勵,并從TDO觀察測試響應。

在移位操作后,新的測試激勵存儲到BSC的update鎖存。

原先這兩個指令是合在一起的,在IEEE 1149.1--2001中這兩個指令分開了,分成一個SAMPLE指令,一個PRELOAD指令。選擇SAMPLE/PRELOAD指令時,IC工作在正常工作模式,也就是說對IC的操作不影響IC的正常工作。選擇邊界掃描寄存器連通TDI和TDO。 SAMPLE指令---通過數據掃描操作(Data Scan)來訪問邊界掃描寄存器,以及對進入和離開IC的數據進行采樣。PRELOAD指令---在進入EXTEST指令之前對邊界掃描寄存器進行數據加載。

(在Capture-DR狀態下,SAMPLE/PRELOAD指令提供一個從管腳到片上系統邏輯的數據流快照,快照在TCK上升沿提取。在Update-DR狀態時,SAMPLE/PRELOAD指令將BSR寄存器單元中的數據鎖存到并行輸出寄存器單元中,然后由EXTEST指令將鎖存在并行輸出寄存器單元中的數據在TCK的下降沿驅動到對應的輸出管腳上去。)

Bypass指令--強制指令

提供穿透芯片的最短通路。

輸入輸出管腳可正常操作

選擇一位的旁路(Bypass)寄存器

強制全為1和未定義的指令為Bypass指令 BYPASS指令為全“1”。選擇BYPASS指令時,IC工作在正常工作模式,選擇一位的BYPASS寄存器連通TDI和TDO,數據的通過不影響IC的正常工作。

(BYPASS指令通過在TDI和TDO之間放置一個1位的旁通寄存器,這樣移位操作時只經過1位的旁通寄存器而不是很多位(與管腳數量相當)的邊界掃描寄存器BSR,從而使得對連接在同一JTAG鏈上主CPU之外的其他芯片進行測試時提高效率。)

INTEST指令 ---可選指令

選擇INTEST指令時,IC工作在邊界掃描內部測試模式(internal boundary-test mode),選擇邊界掃描寄存器連通TDI和TDO。在這種指令下,可以通過邊界掃描輸出單元來驅動測試信號至其內部邏輯,以及通過邊界掃描輸入單元來從 其內部邏輯接受測試信號。

RUNBIST指令 ---可選指令

選擇RUNBIST指令時,IC工作在自測試模式(self-test mode),對IC的內部邏輯進行全面的自測試,通過選擇用戶自定義的數據寄存器連通TDI和TDO。在這種指令下,邊界掃描單元的輸出被內部邏輯控制了,所以外部信號不能干擾其相鄰IC。

IDCODE指令 ---可選指令

選擇IDCODE指令時,IC工作在正常工作模式,選擇數據識別寄存器(data identification register)連通TDI和TDO。數據識別寄存器是一個32位的寄存器,內容包括IC的生產廠商,芯片類型,版本等。訪問數據識別寄存器不會影響 IC的正常工作。由于IDCODE指令是可選的,不是每個芯片都有的,所以當對一個邊界掃描鏈(scan chain)執行IDCODE指令來輸出所有IDCODE時,有IDCODE指令的芯片就選擇IDCODE寄存器,輸出輸出IDCODE,沒有 IDCODE指令的芯片會自動選擇BYPASS寄存器,輸出一個“0”。

(讀取CPU ID號指令。在設計中存在device identification register時,TAP強制定義。該指令將處理器的ID號寄存器連接到TDI和TDO之間。)

USERCODE指令 ---可選指令

選擇USERCODE指令時,IC工作在正常工作模式,選擇用戶自定義數據寄存器(user defined test data register)連通TDI和TDO。USERCODE指令一般是在進行芯片內部測試時用的。

CLAMP指令 ---可選指令

CLAMP指令使IC的輸出置于由邊界掃描寄存器的當前內容決定的邏輯電平上,選擇BYPASS寄存器連通 TDI和TDO。在加載這個指令之前,邊界掃描寄存器的內容可以由SAMPLE/PRELOAD指令來預置。在CLAMP指令下,數據通過BYPASS寄 存器從TDI傳遞至TDO,不會影響此IC的輸出。

HIGHZ指令 ---可選指令

HIGHZ指令使IC的所有輸出置于高阻狀態,選擇BYPASS寄存器連通TDI和TDO。在HIGHZ指令下,數據通過BYPASS寄存器從TDI傳遞至TDO,不會影響此IC的輸出。

-

邊界掃描

+關注

關注

1文章

32瀏覽量

14993

發布評論請先 登錄

相關推薦

基于邊界掃描的電路板快速測試系統設計

邊界掃描測試技術在硬件實驗中的應用

基于廣義特征分析與邊界掃描技術的混合信號測試系統

基于邊界掃描技術的板級測試分析

邊界掃描測試的基本原理及其測試系統的設計

邊界掃描測試應用與九大指令

邊界掃描測試應用與九大指令

評論