我知道,我對與電子有關(guān)的所有事情都很著迷,但不論從哪個(gè)角度看,今天的現(xiàn)場可編程門陣列(FPGA),都顯得“鶴立雞群”,真是非常棒的器件。如果在這個(gè)智能時(shí)代,在這個(gè)領(lǐng)域,想擁有一技之長的你還沒有關(guān)注FPGA,那么世界將拋棄你,時(shí)代將拋棄你。

和SERDES應(yīng)用相關(guān)的高速系統(tǒng)PCB設(shè)計(jì)注意事項(xiàng)如下:

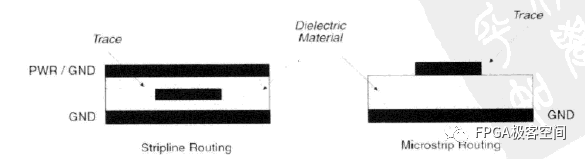

(1)微帶(Microstrip)和帶狀線(Stripline)布線。

微帶線是用電介質(zhì)分隔的參考平面(GND或Vcc)的外層信號層上的布線,這樣能使延遲最小;帶狀線則在兩個(gè)參考平面(GND或Vcc)之間的內(nèi)層信號層布線,這樣能獲得更大的容抗,更易于阻抗控制,使信號更干凈,如圖所示。

微帶線和帶狀線最佳布線

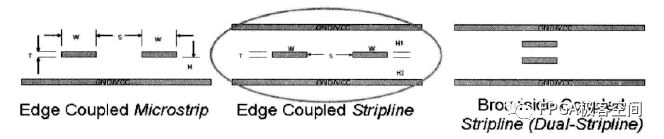

(2)高速差分信號對布線。

高速差分信號對布線常用方法有邊沿耦合(Edge Coupled)的微帶(頂層)、邊沿耦合的帶狀線(內(nèi)嵌信號層,適合布高速SERDES差分信號對)和Broadside耦合微帶等,如圖所示。

高速差分信號對布線

(3)旁路電容 (BypassCapacitor)。

旁路電容是一個(gè)串聯(lián)阻抗非常低的小電容,主要用于濾除高速變換信號中的高頻干擾。在FPGA系統(tǒng)中主要應(yīng)用的旁路電容有3種:高速系統(tǒng)(100MHz~1GHz)常用旁路電容范圍有0.01nF到10nF,一般布在距離Vcc 1cm以內(nèi);中速系統(tǒng)(十幾兆赫茲100MHz),常用旁路電容范圍為47nF到100nF鉭電容,一般布在Vcc 3cm以內(nèi);低速系統(tǒng)(十幾兆赫茲以下),常用旁路電容范圍為470nF到3300nF電容,在PCB上布局比較自由。

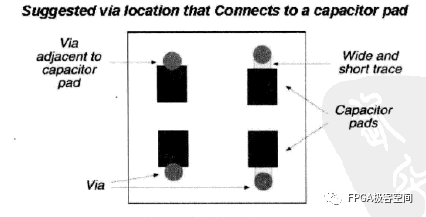

(4)電容最佳布線。

電容布線可遵循下列設(shè)計(jì)準(zhǔn)則,如圖所示。

電容最佳布線

使用大尺寸過孔(Via)連接電容引腳焊盤,以減少耦合容抗。

使用短而寬的線連接過孔和電容引腳的焊盤,或者直接將電容引腳的焊盤與過孔相連接。

使用LESR電容(Low Effective Series Resistance,低串聯(lián)阻抗電容)。

每個(gè)GND引腳或過孔應(yīng)該連接到地平面。

(5)高速系統(tǒng)時(shí)鐘布線要點(diǎn)。

避免使用鋸齒繞線,時(shí)鐘布線要盡可能筆直。

盡量在單一信號層布線。

盡可能不使用過孔,因?yàn)檫^孔將帶來強(qiáng)烈的反射和阻抗不匹配。

盡量在頂層用微帶布線,從而避免使用過孔且使信號時(shí)延最小。

將地平面盡量布在時(shí)鐘信號層旁,用以減少噪音和串?dāng)_。如果使用內(nèi)部信號層布時(shí)鐘線,可以使用兩個(gè)地平面將時(shí)鐘信號層夾在中間,以減少噪聲和干擾。縮短信號時(shí)延。

時(shí)鐘信號應(yīng)該正確阻抗匹配。

(6)高速系統(tǒng)耦合與布線注意事項(xiàng)。

注意差分信號的阻抗匹配。

注意差分信號線的寬度,使之可以容忍20%的信號上升或下降時(shí)間。

使用合適的連接器,連接器的額定頻率應(yīng)該能滿足設(shè)計(jì)的最高頻率。

差分信號對盡量使用edge-couple方式耦合,避免使用broadside-couple方式耦合,使用3S分式法則,避免過耦合或串?dāng)_。

(7)高速系統(tǒng)噪聲濾波注意事項(xiàng)。

減少電源噪聲帶來的低頻干擾(1KHz以下),在每個(gè)電源接入端加屏蔽或者濾波電路。

在每處電源進(jìn)入PCB的地方加100F的電解電容濾波。

為了減少高頻噪音,在每處Vcc和GND處盡可能多地布置去耦合電容。

將Vcc和GND平面平行布置,并用電介質(zhì)(如FR-4PCB)分隔,在其他層布置旁路電容。

(8)高速系統(tǒng)地彈(Ground Bounce)

盡量在每處Vcc/GND信號對上添加去耦合電容。

在計(jì)數(shù)器等高速翻轉(zhuǎn)信號的輸出端加外部Buffer,以減少驅(qū)動能力的要求。

將為使用的用戶I/O設(shè)置成輸出為低電平的輸出信號,這相當(dāng)于虛擬的GND,將這些低電平輸出連接到地平面。

對于速度要求不苛刻的輸出信號設(shè)置為Slow Slew (低上升斜率)的模式。

控制負(fù)載容抗。

減少時(shí)鐘不停翻轉(zhuǎn)的信號,或者將這種信號盡量均勻地分布在芯片的四周。

將翻轉(zhuǎn)頻繁的信號盡量靠近芯片的GND引腳布置。

設(shè)計(jì)同步時(shí)序電路時(shí)應(yīng)該盡量避免輸出瞬時(shí)全部翻轉(zhuǎn)。

將電源和地引岔開布置,這樣可以起到在整體上中和電感的作用。

-

pcb

+關(guān)注

關(guān)注

4318文章

23022瀏覽量

396423

原文標(biāo)題:高速PCB設(shè)計(jì)注意事項(xiàng)

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

資深工程師PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

資深工程師PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

資深電子工程師PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

高質(zhì)量PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

AD20使用技巧及PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

資深工程師PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

高速PCB設(shè)計(jì)的經(jīng)驗(yàn)總結(jié)

PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

PCB設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

評論