一、PCB走線中途容性負載反射很多時候,PCB走線中途會經過過孔、測試點焊盤、短的stub線等,都存在寄生電容,必然對信號造成影響。走線中途的電容對信號的影響要從發射端和接受端兩個方面分析,對起點和終點都有影響。 首先按看一下對信號發射端的影響。當一個快速上升的階躍信號到達電容時,電容快速充電,充電電流和信號電壓上升快慢有關,充電電流公式為:I=C*dV/dt。電容量越大,充電電流越大,信號上升時間越快,dt越小,同樣使充電電流越大。

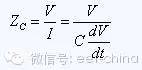

我們知道,信號的反射與信號感受到的阻抗變化有關,因此為了分析,我們看一下,電容引起的阻抗變化。在電容開始充電的初期,阻抗表示為:

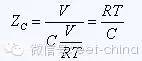

這里dV實際上是階躍信號電壓變化,dt為信號上升時間,電容阻抗公式變為:

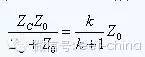

從這個公式中,我們可以得到一個很重要的信息,當階躍信號施加到電容兩端的初期,電容的阻抗與信號上升時間和本身的電容量有關。 通常在電容充電初期,阻抗很小,小于走線的特性阻抗。信號在電容處發生負反射,這個負電壓信號和原信號疊加,使得發射端的信號產生下沖,引起發射端信號的非單調性。 對于接收端,信號到達接收端后,發生正反射,反射回來的信號到達電容位置,那個樣發生負反射,反射回接收端的負反射電壓同樣使接收端信號產生下沖。 為了使反射噪聲小于電壓擺幅的5%(這種情況對信號影響可以容忍),阻抗變化必須小于10%。那么電容阻抗應該控制在多少?電容的阻抗表現為一個并聯阻抗,我們可以用并聯阻抗公式和反射系數公式來確定它的范圍。對于這種并聯阻抗,我們希望電容阻抗越大越好。假設電容阻抗是PCB走線特性阻抗的k倍,根據并聯阻抗公式得到電容處信號感受到的阻抗為:

阻抗變化率為:

,即

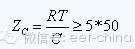

,即 ,也就是說,根據這種理想的計算,電容的阻抗至少要是PCB特性阻抗的9倍以上。實際上,隨著電容的充電,電容的阻抗不斷增加,并不是一直保持最低阻抗,另外,每一個器件還會有寄生電感,使阻抗增加。因此這個9倍限制可以放寬。在下邊的討論中假設這個限制是5倍。 有了阻抗的指標,我們就可以確定能容忍多大的電容量。電路板上50歐姆特性阻抗很常見,我就用50歐姆來計算。

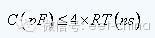

,也就是說,根據這種理想的計算,電容的阻抗至少要是PCB特性阻抗的9倍以上。實際上,隨著電容的充電,電容的阻抗不斷增加,并不是一直保持最低阻抗,另外,每一個器件還會有寄生電感,使阻抗增加。因此這個9倍限制可以放寬。在下邊的討論中假設這個限制是5倍。 有了阻抗的指標,我們就可以確定能容忍多大的電容量。電路板上50歐姆特性阻抗很常見,我就用50歐姆來計算。 得出:

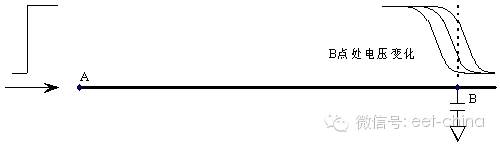

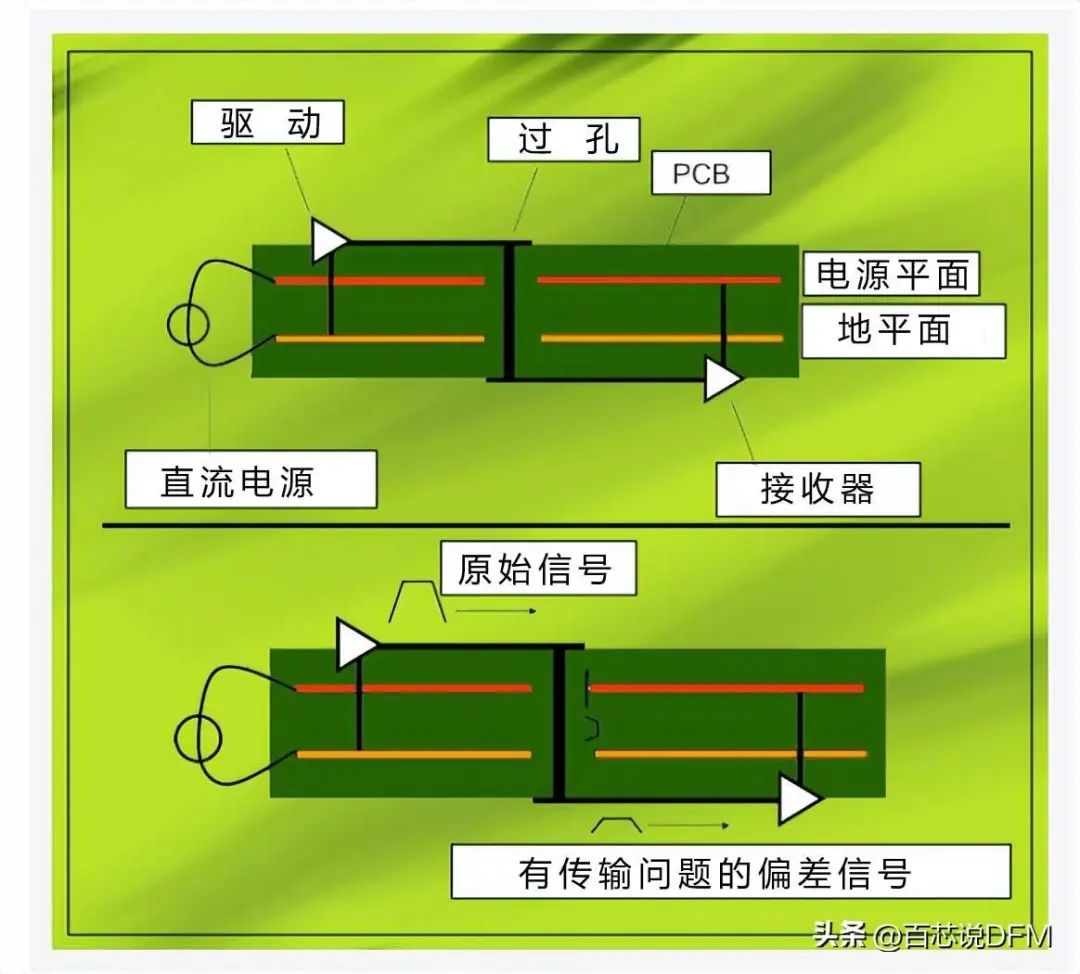

得出: 即在這種情況下,如果信號上升時間為1ns,那么電容量要小于4皮法。反之,如果電容量為4皮法,則信號上升時間最快為1ns,如果信號上升時間為0.5ns,這個4皮法的電容就會產生問題。這里的計算只不過是為了說明電容的影響,實際電路中情況十分復雜,需要考慮的因素更多,因此這里計算是否精確沒有實際意義。關鍵是要通過這種計算理解電容是如何影響信號的。我們對電路板上每一個因素的影響都有一個感性認識后,就能為設計提供必要的指導,出現問題就知道如何去分析。精確的評估需要用軟件來仿真。總結:1 PCB走線中途容性負載使發射端信號產生下沖,接收端信號也會產生下沖。2 能容忍的電容量和信號上升時間有關,信號上升時間越快,能容忍的電容量越小。二、接收端容性負載的反射信號的接收端可能是集成芯片的一個引腳,也可能是其他元器件。不論接收端是什么,實際的器件的輸入端必然存在寄生電容,接受信號的芯片引腳和相鄰引腳之間有一定的寄生電容,和引腳相連的芯片內部的布線也會存在寄生電容,另外引腳和信號返回路徑之間也會存在寄生電容。好復雜,這么多寄生電容!其實很簡單,想想電容是什么?兩個金屬板,中間是某種絕緣介質。這個定義中并沒有說兩個金屬板是什么形狀的,芯片兩個相鄰引腳也可以看做是電容的兩個金屬板,中間介質是空氣,不就是一個電容么。芯片引腳和PCB板內層的電源或地平面也是一對金屬板,中間介質是PCB板的板材,常見的是FR4材料,也是一個電容。呵呵,搞來搞去,還是回到了最基礎的部分。高手不要笑,太簡單了。不過確實很多人看到寄生電容就感到有點暈,理解不透,所以在這里啰嗦一下。回到正題,下面研究一下信號終端的電容有什么影響。將模型簡化,用一個分立電容元件代替所有寄生電容,如圖1所示。

即在這種情況下,如果信號上升時間為1ns,那么電容量要小于4皮法。反之,如果電容量為4皮法,則信號上升時間最快為1ns,如果信號上升時間為0.5ns,這個4皮法的電容就會產生問題。這里的計算只不過是為了說明電容的影響,實際電路中情況十分復雜,需要考慮的因素更多,因此這里計算是否精確沒有實際意義。關鍵是要通過這種計算理解電容是如何影響信號的。我們對電路板上每一個因素的影響都有一個感性認識后,就能為設計提供必要的指導,出現問題就知道如何去分析。精確的評估需要用軟件來仿真。總結:1 PCB走線中途容性負載使發射端信號產生下沖,接收端信號也會產生下沖。2 能容忍的電容量和信號上升時間有關,信號上升時間越快,能容忍的電容量越小。二、接收端容性負載的反射信號的接收端可能是集成芯片的一個引腳,也可能是其他元器件。不論接收端是什么,實際的器件的輸入端必然存在寄生電容,接受信號的芯片引腳和相鄰引腳之間有一定的寄生電容,和引腳相連的芯片內部的布線也會存在寄生電容,另外引腳和信號返回路徑之間也會存在寄生電容。好復雜,這么多寄生電容!其實很簡單,想想電容是什么?兩個金屬板,中間是某種絕緣介質。這個定義中并沒有說兩個金屬板是什么形狀的,芯片兩個相鄰引腳也可以看做是電容的兩個金屬板,中間介質是空氣,不就是一個電容么。芯片引腳和PCB板內層的電源或地平面也是一對金屬板,中間介質是PCB板的板材,常見的是FR4材料,也是一個電容。呵呵,搞來搞去,還是回到了最基礎的部分。高手不要笑,太簡單了。不過確實很多人看到寄生電容就感到有點暈,理解不透,所以在這里啰嗦一下。回到正題,下面研究一下信號終端的電容有什么影響。將模型簡化,用一個分立電容元件代替所有寄生電容,如圖1所示。

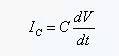

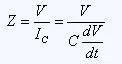

我們考察B點電容的阻抗情況。電容的電流為:

隨著電容的充電,電壓變化率逐漸減小(電路原理中的瞬態過程),電容的充電電流也不斷減小。即電容的充電電流是隨時間變化的。

電容的阻抗為:

因此電容所表現出來的阻抗隨時間變化,不是恒定的。正是這種阻抗的變化特性決定了電容對信號影響的特殊性。如果信號上升時間小于電容的充電時間,最初電容兩端的電壓迅速上升,這時阻抗很小。隨著電容充電,電壓變化率下降,充電電流減小,表現為阻抗明顯增大。充電時間無窮大時,電容相當于開路,阻抗無窮大。

阻抗的變化必然影響信號的反射。在充電的開始一段時間,阻抗很小,小于傳輸線的特性阻抗,將發生負反射,反射回源端A點的信號將產生下沖。隨著電容阻抗的增加,反射逐漸過渡到正反射,A點的信號經過一個下沖會逐漸升高,最終達到開路電壓。因此電容負載使源端信號產生局部電壓凹陷。精確波形和傳輸線的特性阻抗、電容量、信號上升時間有關。對于接收端,很明顯,就是一個RC充電電路,不是很嚴謹,但是和實際情況非常相似。電容兩端電壓,即B點電壓隨RC充電電路的時間常數呈指數增加(基本電路原理)。因此電容對接收端信號上升時間產生影響。RC充電電路的時間常數為 這是B點電壓上升到電壓終值的即37%所需的時間。B點電壓10%~90%上升時間為

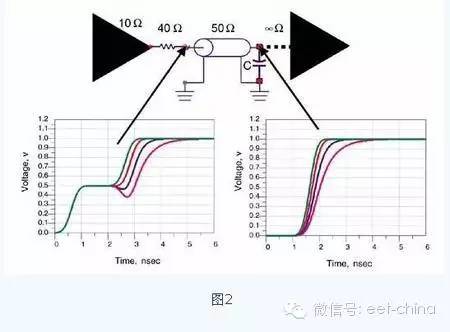

這是B點電壓上升到電壓終值的即37%所需的時間。B點電壓10%~90%上升時間為 如果傳輸線特性阻抗為50歐姆,電容量10pF,則10~90充電時間為1.1ns。如果信號上升時間小于1.1ns,那么B點電壓上升時間主要由電容充電時間決定。如果信號上升時間大于1.1ns,末端電容器作用是使上升時間進一步延長,增加約1.1ns(實際應比這個值小)。圖2顯示了終端電容負載對驅動端和接受端產生影響的示意圖,放在這里,讓大家能有個感性的認識。

如果傳輸線特性阻抗為50歐姆,電容量10pF,則10~90充電時間為1.1ns。如果信號上升時間小于1.1ns,那么B點電壓上升時間主要由電容充電時間決定。如果信號上升時間大于1.1ns,末端電容器作用是使上升時間進一步延長,增加約1.1ns(實際應比這個值小)。圖2顯示了終端電容負載對驅動端和接受端產生影響的示意圖,放在這里,讓大家能有個感性的認識。

至于信號上升時間增加的精確值是多少,對于電路設計來說沒必要,只要定性的分析,有個大致的估算就可以了。因為計算再精確也沒實際意義,電路板的參數也不精確!對于設計者來說,定性分析并了解影響,大致估算出影響在那個量級,能給電路設計提供指導就可以了,其他的事軟件來做吧。舉個例子,如果信號上升時間1ns,電容使信號上升時間增加遠小于1ns,比如0.2 ns,那么這么一點點增加可能不會有什么影響。如果電容造成的上升時間增加很多,那可能就會對電路時序產生影響。那么多少算很多?看看電路的時序余量吧,這涉及到電路的時序分析和時序設計。

總之接收端電容負載的影響有兩點:1、使源端(驅動端)信號產生局部電壓凹陷。2、接收端信號上升時間延長。 在電路設計中這兩點都要考慮。三、PCB走線寬度變化產生的反射

在進行PCB布線時,經常會發生這樣的情況:走線通過某一區域時,由于該區域布線空間有限,不得不使用更細的線條,通過這一區域后,線條再恢復原來的寬度。走線寬度變化會引起阻抗變化,因此發生反射,對信號產生影響。那么什么情況下可以忽略這一影響,又在什么情況下我們必須考慮它的影響?

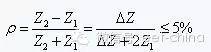

有三個因素和這一影響有關:阻抗變化的大小、信號上升時間、窄線條上信號的時延。首先討論阻抗變化的大小。很多電路的設計要求反射噪聲小于電壓擺幅的5%(這和信號上的噪聲預算有關),根據反射系數公式:

以計算出阻抗大致的變化率要求為: 你可能知道,電路板上阻抗的典型指標為+/-10%,根本原因就在這。如果阻抗變化只發生一次,例如線寬從8mil變到6mil后,一直保持6mil寬度這種情況,要達到突變處信號反射噪聲不超過電壓擺幅的5%這一噪聲預算要求,阻抗變化必須小于10%。這有時很難做到,以 FR4板材上微帶線的情況為例,我們計算一下。如果線寬8mil,線條和參考平面之間的厚度為4mil,特性阻抗為46.5歐姆。線寬變化到6mil后特性阻抗變成54.2歐姆,阻抗變化率達到了20%。反射信號的幅度必然超標。至于對信號造成多大影響,還和信號上升時間和驅動端到反射點處信號的時延有關。但至少這是一個潛在的問題點。幸運的是這時可以通過阻抗匹配端接解決問題。如果阻抗變化發生兩次,例如線寬從8mil變到6mil后,拉出2cm后又變回8mil。那么在2cm長6mil寬線條的兩個端點處都會發生反射,一次是阻抗變大,發生正反射,接著阻抗變小,發生負反射。如果兩次反射間隔時間足夠短,兩次反射就有可能相互抵消,從而減小影響。假設傳輸信號為1V,第一次正反射有0.2V被反射,1.2V繼續向前傳輸,第二次反射有 -0.2*1.2 = 0.24v被反射回。再假設6mil線長度極短,兩次反射幾乎同時發生,那么總的反射電壓只有0.04V,小于5%這一噪聲預算要求。因此,這種反射是否影響信號,有多大影響,和阻抗變化處的時延以及信號上升時間有關。研究及實驗表明,只要阻抗變化處的時延小于信號上升時間的20%,反射信號就不會造成問題。如果信號上升時間為1ns,那么阻抗變化處的時延小于0.2ns對應1.2英寸,反射就不會產生問題。也就是說,對于本例情況,6mil寬走線的長度只要小于3cm就不會有問題。當PCB走線線寬發生變化時,要根據實際情況仔細分析,是否造成影響。需要關注的參數由三個:阻抗變化有多大、信號上升時間是多少、線寬變化的頸狀部分有多長。根據上面的方法大致估算一下,適當留出一定的余量。如果可能的話,盡量讓減小頸狀部分長度。需要指出的是,實際的PCB加工中,參數不可能像理論中那樣精確,理論能對我們的設計提供指導,但不能照搬照抄,不能教條,畢竟這是一門實踐的科學。估算出的值要根據實際情況做適當的修訂,再應用到設計中。如果感覺經驗不足,那就先保守點,然后在根據制造成本適當調整.四、信號振鈴是怎么產生的信號的反射可能會引起振鈴現象,一個典型的信號振鈴如圖1所示。

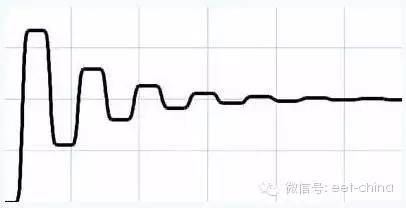

你可能知道,電路板上阻抗的典型指標為+/-10%,根本原因就在這。如果阻抗變化只發生一次,例如線寬從8mil變到6mil后,一直保持6mil寬度這種情況,要達到突變處信號反射噪聲不超過電壓擺幅的5%這一噪聲預算要求,阻抗變化必須小于10%。這有時很難做到,以 FR4板材上微帶線的情況為例,我們計算一下。如果線寬8mil,線條和參考平面之間的厚度為4mil,特性阻抗為46.5歐姆。線寬變化到6mil后特性阻抗變成54.2歐姆,阻抗變化率達到了20%。反射信號的幅度必然超標。至于對信號造成多大影響,還和信號上升時間和驅動端到反射點處信號的時延有關。但至少這是一個潛在的問題點。幸運的是這時可以通過阻抗匹配端接解決問題。如果阻抗變化發生兩次,例如線寬從8mil變到6mil后,拉出2cm后又變回8mil。那么在2cm長6mil寬線條的兩個端點處都會發生反射,一次是阻抗變大,發生正反射,接著阻抗變小,發生負反射。如果兩次反射間隔時間足夠短,兩次反射就有可能相互抵消,從而減小影響。假設傳輸信號為1V,第一次正反射有0.2V被反射,1.2V繼續向前傳輸,第二次反射有 -0.2*1.2 = 0.24v被反射回。再假設6mil線長度極短,兩次反射幾乎同時發生,那么總的反射電壓只有0.04V,小于5%這一噪聲預算要求。因此,這種反射是否影響信號,有多大影響,和阻抗變化處的時延以及信號上升時間有關。研究及實驗表明,只要阻抗變化處的時延小于信號上升時間的20%,反射信號就不會造成問題。如果信號上升時間為1ns,那么阻抗變化處的時延小于0.2ns對應1.2英寸,反射就不會產生問題。也就是說,對于本例情況,6mil寬走線的長度只要小于3cm就不會有問題。當PCB走線線寬發生變化時,要根據實際情況仔細分析,是否造成影響。需要關注的參數由三個:阻抗變化有多大、信號上升時間是多少、線寬變化的頸狀部分有多長。根據上面的方法大致估算一下,適當留出一定的余量。如果可能的話,盡量讓減小頸狀部分長度。需要指出的是,實際的PCB加工中,參數不可能像理論中那樣精確,理論能對我們的設計提供指導,但不能照搬照抄,不能教條,畢竟這是一門實踐的科學。估算出的值要根據實際情況做適當的修訂,再應用到設計中。如果感覺經驗不足,那就先保守點,然后在根據制造成本適當調整.四、信號振鈴是怎么產生的信號的反射可能會引起振鈴現象,一個典型的信號振鈴如圖1所示。

圖1

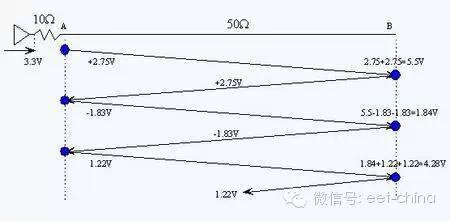

那么信號振鈴是怎么產生的呢?前面講過,如果信號傳輸過程中感受到阻抗的變化,就會發生信號的反射。這個信號可能是驅動端發出的信號,也可能是遠端反射回來的反射信號。根據反射系數的公式,當信號感受到阻抗變小,就會發生負反射,反射的負電壓會使信號產生下沖。信號在驅動端和遠端負載之間多次反射,其結果就是信號振鈴。大多數芯片的輸出阻抗都很低,如果輸出阻抗小于PCB走線的特性阻抗,那么在沒有源端端接的情況下,必然產生信號振鈴。信號振鈴的過程可以用反彈圖來直觀的解釋。假設驅動端的輸出阻抗是10歐姆,PCB走線的特性阻抗為50歐姆(可以通過改變PCB走線寬度,PCB走線和內層參考平面間介質厚度來調整),為了分析方便,假設遠端開路,即遠端阻抗無窮大。驅動端傳輸3.3V電壓信號。我們跟著信號在這條傳輸線中跑一次,看看到底發生了什么?為分析方便,忽略傳輸線寄生電容和寄生電感的影響,只考慮阻性負載。圖2為反射示意圖。第1次反射:信號從芯片內部發出,經過10歐姆輸出阻抗和50歐姆PCB特性阻抗的分壓,實際加到PCB走線上的信號為A點電壓3.3*50/(10+50)=2.75V。傳輸到遠端B點,由于B點開路,阻抗無窮大,反射系數為1,即信號全部反射,反射信號也是2.75V。此時B點測量電壓是2.75+2.75=5.5V。第2次反射:2.75V反射電壓回到A點,阻抗由50歐姆變為10歐姆,發生負反射,A點反射電壓為-1.83V,該電壓到達B點,再次發生反射,反射電壓-1.83V。此時B點測量電壓為5.5-1.83-1.83=1.84V。第3次反射:從B點反射回的-1.83V電壓到達A點,再次發生負反射,反射電壓為1.22V。該電壓到達B點再次發生正反射,反射電壓1.22V。此時B點測量電壓為1.84+1.22+1.22=4.28V。第4次反射:。。。 。。。 。。。第5次反射:。。。 。。。 。。。如此循環,反射電壓在A點和B點之間來回反彈,而引起B點電壓不穩定。觀察B點電壓:5.5V->1.84V->4.28V->……,可見B點電壓會有上下波動,這就是信號振鈴。

信號振鈴根本原因是負反射引起的,其罪魁禍首仍然是阻抗變化,又是阻抗!在研究信號完整性問題時,一定時時注意阻抗問題。

負載端信號振鈴會嚴重干擾信號的接受,產生邏輯錯誤,必須減小或消除,因此對于長的傳輸線必須進行阻抗匹配端接。五、信號反射信號沿傳輸線向前傳播時,每時每刻都會感受到一個瞬態阻抗,這個阻抗可能是傳輸線本身的,也可能是中途或末端其他元件的。對于信號來說,它不會區分到底是什么,信號所感受到的只有阻抗。如果信號感受到的阻抗是恒定的,那么他就會正常向前傳播,只要感受到的阻抗發生變化,不論是什么引起的(可能是中途遇到的電阻,電容,電感,過孔,PCB轉角,接插件),信號都會發生反射。那么有多少被反射回傳輸線的起點?衡量信號反射量的重要指標是反射系數,表示反射電壓和原傳輸信號電壓的比值。反射系數定義為:

其中:

其中: 為變化前的阻抗,

為變化前的阻抗, 為變化后的阻抗。假設PCB線條的特性阻抗為50歐姆,傳輸過程中遇到一個100歐姆的貼片電阻,暫時不考慮寄生電容電感的影響,把電阻看成理想的純電阻,那么反射系數為:

為變化后的阻抗。假設PCB線條的特性阻抗為50歐姆,傳輸過程中遇到一個100歐姆的貼片電阻,暫時不考慮寄生電容電感的影響,把電阻看成理想的純電阻,那么反射系數為: ,信號有1/3被反射回源端。如果傳輸信號的電

,信號有1/3被反射回源端。如果傳輸信號的電

壓是3.3V電壓,反射電壓就是1.1V。純電阻性負載的反射是研究反射現象的基礎,阻性負載的變化無非是以下四種情況:阻抗增加有限值、減小有限值、開路(阻抗變為無窮大)、短路(阻抗突然變為0)。阻抗增加有限值:反射電壓上面的例子已經計算過了。這時,信號反射點處就會有兩個電壓成分,一部分是從源端傳來的3.3V電壓,另一部分是在反射電壓1.1V,那么反射點處的電壓為二者之和,即4.4V。阻抗減小有限值:仍按上面的例子,PCB線條的特性阻抗為50歐姆,如果遇到的電阻是30歐姆,則反射系數為 ,反射系數為負值,說明反射電壓為負電壓,值為

,反射系數為負值,說明反射電壓為負電壓,值為 此時反射點電壓為3.3V+(-0.825V)=2.475V。 開路:開路相當于阻抗無窮大,反射系數按公式計算為1。即反射電壓3.3V。反射點處電壓為6.6V。可見,在這種極端情況下,反射點處電壓翻倍了。短路:短路時阻抗為0,電壓一定為0。按公式計算反射系數為-1,說明反射電壓為-3.3V,因此反射點電壓為0。計算非常簡單,重要的是必須知道,由于反射現象的存在,信號傳播路徑中阻抗發生變化的點,其電壓不再是原來傳輸的電壓。這種反射電壓會改變信號的波形,從而可能會引起信號完整性問題。這種感性的認識對研究信號完整性及設計電路板非常重要,必須在頭腦中建立起這個概念。

此時反射點電壓為3.3V+(-0.825V)=2.475V。 開路:開路相當于阻抗無窮大,反射系數按公式計算為1。即反射電壓3.3V。反射點處電壓為6.6V。可見,在這種極端情況下,反射點處電壓翻倍了。短路:短路時阻抗為0,電壓一定為0。按公式計算反射系數為-1,說明反射電壓為-3.3V,因此反射點電壓為0。計算非常簡單,重要的是必須知道,由于反射現象的存在,信號傳播路徑中阻抗發生變化的點,其電壓不再是原來傳輸的電壓。這種反射電壓會改變信號的波形,從而可能會引起信號完整性問題。這種感性的認識對研究信號完整性及設計電路板非常重要,必須在頭腦中建立起這個概念。

-

pcb

+關注

關注

4318文章

23022瀏覽量

396423 -

信號

+關注

關注

11文章

2781瀏覽量

76648 -

焊盤

+關注

關注

6文章

548瀏覽量

38094

原文標題:PCB信號完整性五部曲

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB信號完整性五部曲

PCB信號完整性五部曲

評論