在高速信號(hào)電路設(shè)計(jì)中,TI的信號(hào)調(diào)理產(chǎn)品被廣泛使用。其中retimer類(lèi)產(chǎn)品涉及到寄存器配置,因此相比較而言,它的使用最為復(fù)雜。本文將以DS125DF1610為例,具體講解retimer類(lèi)產(chǎn)品的電路設(shè)計(jì)與寄存器配置。

下圖是DS125DF1610產(chǎn)品資料中的典型應(yīng)用圖。

硬件電路設(shè)計(jì)可以概括為四個(gè)關(guān)鍵部分:

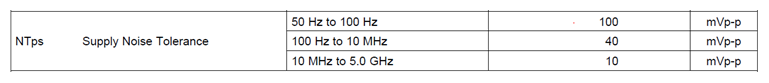

1. 電源:TI的retimer產(chǎn)品供電方式都非常簡(jiǎn)單,一般只需2.5V單電源,像DS125DF111還可以支持單3.3V供電。從下表可以看到,retimer對(duì)電源噪聲性能要求不高,通常情況下可以采用DC/DC電源方案,在供電管腳增加適當(dāng)?shù)臑V波電容即可。

另外,電源選型時(shí)還需要注意功耗問(wèn)題,在芯片資料中都會(huì)給出各種功能組合下的功耗,那么我們就可以根據(jù)實(shí)際應(yīng)用計(jì)算出最大的功耗,作為電源方案選擇的一個(gè)參考標(biāo)準(zhǔn)。

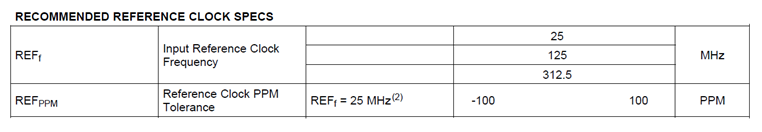

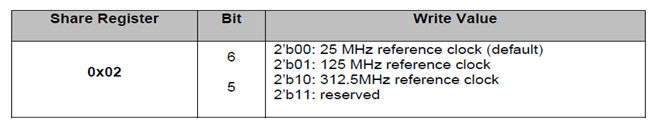

2. 時(shí)鐘:外部參考時(shí)鐘主要是給retimer內(nèi)部VCO提供一個(gè)校準(zhǔn)的參考,它只要求頻率的精度在+/-100ppm范圍之內(nèi)即可,而對(duì)phase noise沒(méi)有特別的要求。需要注意的是不同的retimer支持的時(shí)鐘頻率和電平有區(qū)別。像DS125DF1610可以支持25 MHz,125 MHz和312.5MHz的單端或差分輸入,而大部分10G retimer,比如DS125DF111只支持25MHz的單端輸入。設(shè)計(jì)時(shí)需要根據(jù)數(shù)據(jù)手冊(cè)來(lái)進(jìn)行選擇。

3. AC耦合電容:高速信號(hào)傳輸通常需要做AC耦合,考慮到布板的方便性以及信號(hào)的完整性,TI部分retimer產(chǎn)品在芯片內(nèi)部會(huì)集成該耦合電容,這個(gè)需要設(shè)計(jì)時(shí)從產(chǎn)品手冊(cè)上去確認(rèn),避免遺漏或者重復(fù)添加。

4. I/O口耐壓:如前面所講,TI retimer一般都是2.5V單電源供電,因此需要注意它的I/O口耐壓?jiǎn)栴}。為了方便與板上主控芯片的對(duì)接,retimer內(nèi)部對(duì)I2C,RESET和INTERRUPT口做了特殊處理,都允許直接上拉到3.3V,這個(gè)可以從典型應(yīng)用圖上看到。而其他I/O口就需要注意不能超過(guò)電源供電電壓。

高速信號(hào)電路設(shè)計(jì)還有一個(gè)非常重要的地方就是PCB layout,它直接影響信號(hào)傳輸中的性能。在layout時(shí),我們需要注意:

信號(hào)、電源和地層的合理分配,信號(hào)盡可能的遠(yuǎn)離噪聲源;

保持高速差分線的對(duì)稱(chēng),以及阻抗控制在100?±5%以內(nèi);

避免差分線的劇烈彎折,使用45°或者曲線彎折;

保證不同差分線對(duì)間的skew匹配。

沿信號(hào)路徑,避免參考平面的不連續(xù)而引起阻抗的變化,注意電流返回路徑;

AC耦合電容最大選擇0402封裝,盡可能的保證走線寬度一致,盡量減少過(guò)孔數(shù)量;

選擇的連接器要能滿足最高速率性能要求。

在做電路設(shè)計(jì)時(shí),只要注意到上面提到的這些地方,應(yīng)該就可以保證芯片正常上電工作和傳輸鏈路上信號(hào)的性能,接下來(lái)我們需要做的是寄存器配置。需要注意,上電后系統(tǒng)最佳的配置順序是先ASIC,后retimer。這是因?yàn)槿绻鹯etimer先于ASIC 配置,那么這時(shí)ASIC高速I(mǎi)/O口發(fā)送的數(shù)據(jù)不穩(wěn)定,而retimer只要檢測(cè)到有信號(hào)后,就會(huì)嘗試去鎖定,此時(shí)自適應(yīng)出來(lái)的參數(shù)就不是最優(yōu)的。

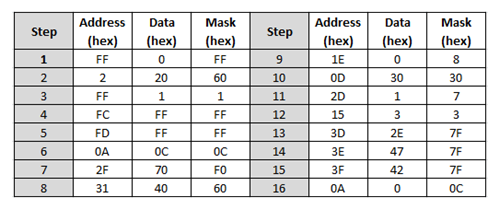

下面還是以DS125DF1610為例,假設(shè)外部采用125MHz的參考時(shí)鐘,系統(tǒng)需要兼容12.5Gbps和6.25Gbps速率,下表就是我們常用到的配置流程。

在講解retimer配置的具體步驟之前,需要了解什么是掩碼方式寫(xiě)入。因?yàn)樵谂渲眉拇嫫鲿r(shí),只能對(duì)需要配置的bit位進(jìn)行修改,而其他bit位要保持默認(rèn)值不變。

以step 2為例,需要對(duì)寄存器0x02進(jìn)行掩碼為0x60的寫(xiě)入操作,寫(xiě)入值為0x20。首先,掩碼0x60展開(kāi)后只有bit 5和6為1,也就是說(shuō)我們只能修改寄存器0x02的bit 5和6,寫(xiě)入的值為數(shù)據(jù)0x20相對(duì)應(yīng)的bit位值,而寄存器其他bit位要保持出廠默認(rèn)值不變。

下面將詳細(xì)說(shuō)明每步配置的作用。

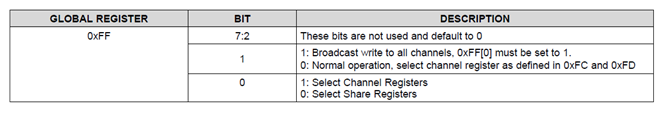

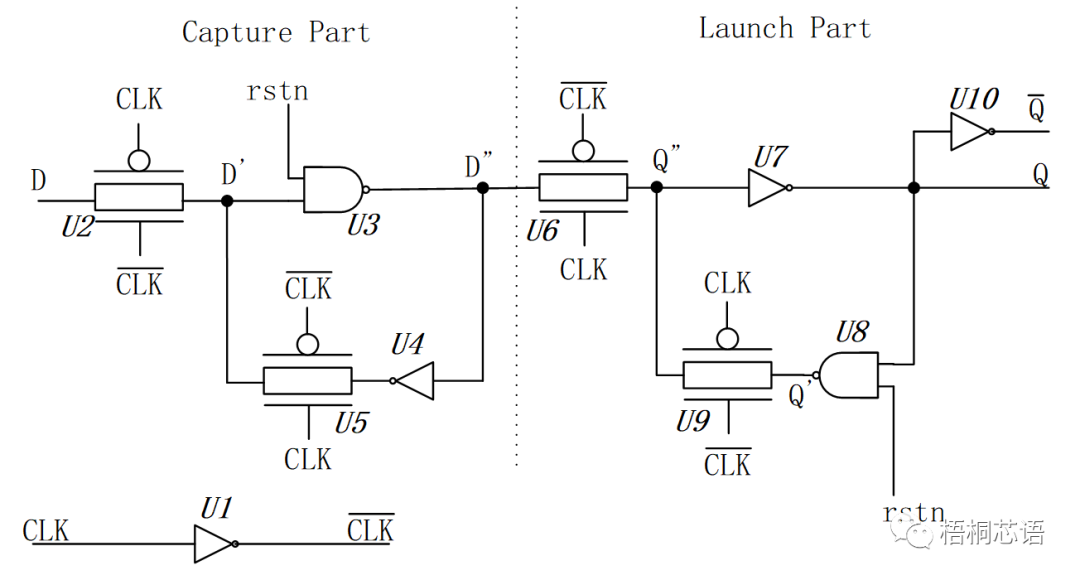

Step 1:retimer內(nèi)部寄存器一般分成兩類(lèi):shared寄存器和channel寄存器。像retimer的一些全局信息,比如chip ID,外部參考時(shí)鐘的選擇等等都在shared寄存器里。因此在配置之前,要清楚將要操作的是哪類(lèi)寄存器。寄存器0xFF的bit 0就是進(jìn)行選擇。

Step 2:在step 1中已經(jīng)選定操作的是shared寄存器,所以接下來(lái)對(duì)0x02寄存器的操作就是選擇外部參考時(shí)鐘,根據(jù)datasheet給出的值選中即可。

Step 3~5:一般shared寄存器需要操作的就是選擇參考時(shí)鐘,其它的配置都在channel寄存器中。首先Step 3選中channel寄存器,step 4和5選擇哪些channel將同時(shí)被修改。如果所有channel采用相同配置,最簡(jiǎn)便的方法就是將0xFF的bit 1置為1,那么將會(huì)以廣播的方式修改所有通道,而不用再去配置channel選擇寄存器。

Step 6:配置channel寄存器前,將CDR置于復(fù)位狀態(tài),以保證配置沒(méi)有完成之前,retimer不會(huì)嘗試去鎖定。

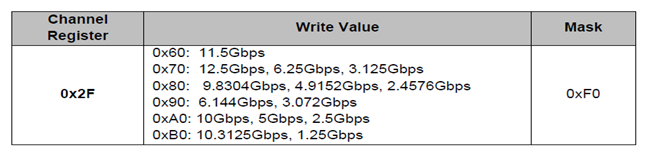

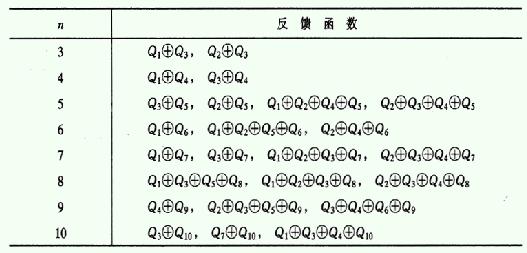

Step 7:CDR鎖定速率有兩種配置方式。如果系統(tǒng)速率是常見(jiàn)的標(biāo)準(zhǔn)速率,比如下表中列舉的值,那么我們直接選擇相應(yīng)的寄存器值即可。但如果不是標(biāo)準(zhǔn)速率,比如11.3Gbps,那么我們就需要采用手動(dòng)計(jì)算VCO工作頻率,具體步驟可以參考DS125DF1610產(chǎn)品資料的8.3.2章節(jié)。

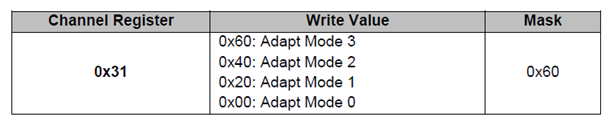

Step 8:根據(jù)CDR鎖定時(shí)CTLE和DFE自適應(yīng)算法的區(qū)別,通常有四種工作模式可選。如下表,可以根據(jù)調(diào)試情況,通過(guò)寄存器0x31選擇其中一種。

四種模式具體區(qū)別如下:

Mode 0:手動(dòng)模式,CTLE和DFE均需要手動(dòng)設(shè)置;

Mode 1:CTLE自適應(yīng),而DFE需要手動(dòng)設(shè)置;

Mode 2:CTLE首先自適應(yīng)到一個(gè)最優(yōu)的設(shè)置,然后DFE再自適應(yīng)調(diào)整;

Mode 3:CTLE首先自適應(yīng)到一個(gè)最低要求的水平,然后DFE自適應(yīng)到最佳設(shè)置,最后CTLE再重新自適應(yīng)到最佳的水平。

Step 9:根據(jù)上一步選擇的工作模式確定是否需要使能DFE。

Step 10~15:高速接口都是只有接收側(cè)參數(shù)可以自適應(yīng),發(fā)送側(cè)參數(shù)需要手動(dòng)設(shè)置。Step 10到15就是用于配置retimer發(fā)送信號(hào)幅度,加重和FIR濾波器。

Step 16:釋放CDR復(fù)位。

通常情況下,完成上面的配置后,retimer就可以正常鎖定工作。如果測(cè)試中鏈路上有誤碼的話,則需要根據(jù)實(shí)際情況去優(yōu)化各個(gè)參數(shù)。

-

寄存器

+關(guān)注

關(guān)注

31文章

5322瀏覽量

120021 -

DC/DC轉(zhuǎn)換器

+關(guān)注

關(guān)注

2文章

157瀏覽量

10140 -

DS1250

+關(guān)注

關(guān)注

0文章

2瀏覽量

7816

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何根據(jù)自己設(shè)計(jì)中的寄存器配置總線定義來(lái)生成一套寄存器配置模版

基于LMH6505的中頻信號(hào)調(diào)理電路設(shè)計(jì)

時(shí)序電路設(shè)計(jì)串入/并出移位寄存器

時(shí)序電路設(shè)計(jì)串入/并出移位寄存器

線性移位寄存器

數(shù)據(jù)寄存器,數(shù)據(jù)寄存器是什么意思

MAXQ3180入門(mén):寄存器配置

MPC860寄存器配置

IO口配置常用的8個(gè)寄存器 1.6

GPIO寄存器

配置STM32寄存器控制GPIO點(diǎn)亮LED

寄存器門(mén)電路原理分析

信號(hào)調(diào)理產(chǎn)品電路設(shè)計(jì)與寄存器配置

信號(hào)調(diào)理產(chǎn)品電路設(shè)計(jì)與寄存器配置

評(píng)論