由于我們當(dāng)時的題目除了測量頻率之外,更麻煩的是測量占空比。而這兩個的測量方法聯(lián)系比較緊密,所以也一并把測量占空比的方法寫出來。

使用平臺:官方STM32F429DISCOVERY開發(fā)板,180MHz的主頻,定時器頻率90MHz。

相關(guān)題目:

(1)測量脈沖信號頻率f_O,頻率范圍為10Hz~2MHz,測量誤差的絕對值不大于0.1%。(15分)

(2)測量脈沖信號占空比D,測量范圍為10%~90%,測量誤差的絕對值不大于2%。(15分)

思路一:外部中斷

思路:這種方法是很容易想到的,而且對幾乎所有MCU都適用(連51都可以)。方法也很簡單,聲明一個計數(shù)變量TIM_cnt,每次一個上升沿/下降沿就進入一次中斷,對TIM_cnt++,然后定時統(tǒng)計即可。如果需要占空比,那么就另外用一個定時器統(tǒng)計上升沿、下降沿之間的時間即可。

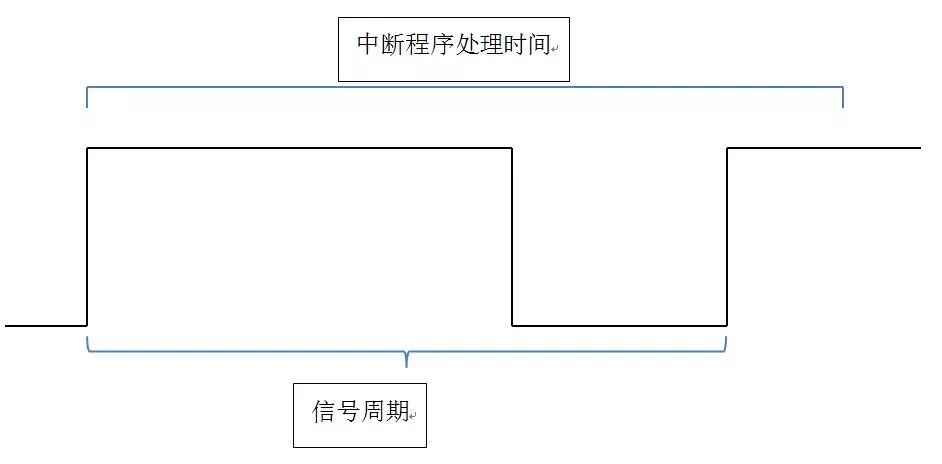

缺點:缺陷顯而易見,當(dāng)頻率提高,將會頻繁進入中斷,占用大量時間。而當(dāng)頻率超過100kHz時,中斷程序時間甚至將超過脈沖周期,產(chǎn)生巨大誤差。同時更重要的是,想要測量的占空比由于受到中斷程序影響,誤差將越來越大。

總結(jié):我們當(dāng)時第一時間就把這個方案PASS了,沒有相關(guān)代碼(這個代碼也很簡單)。不過,該方法在頻率較低(10K以下)時,可以拿來測量頻率。在頻率更低的情況下,可以拿來測占空比。

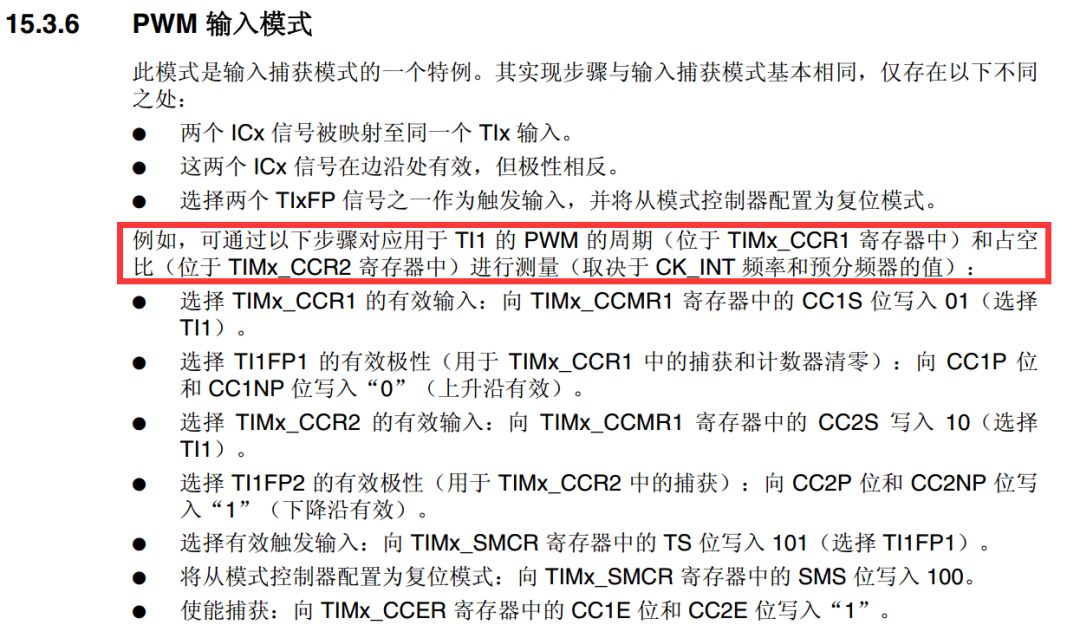

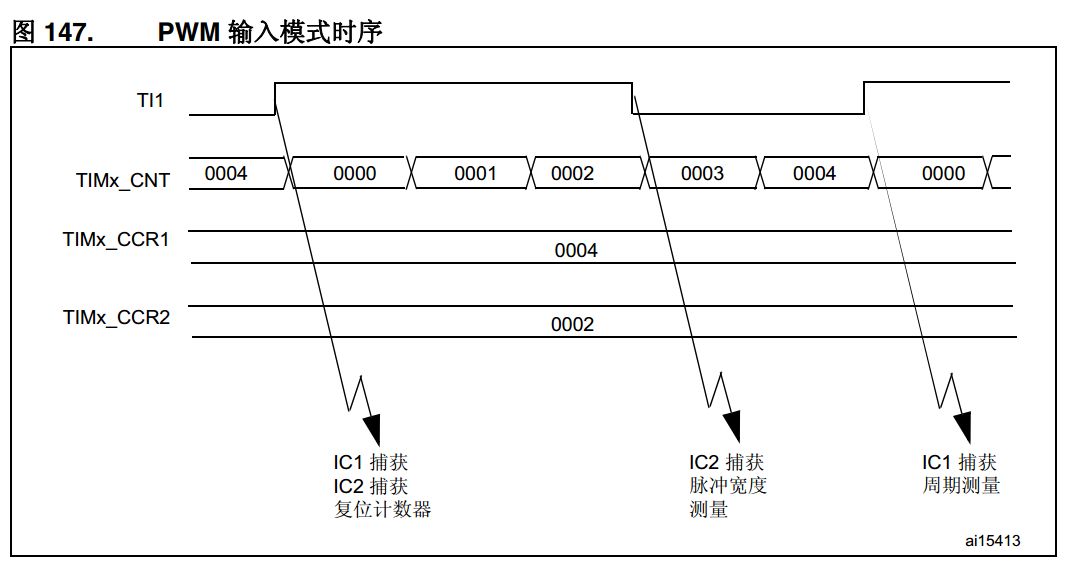

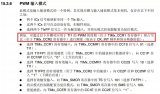

思路二:PWM輸入模式

思路:翻遍ST的參考手冊,在定時器當(dāng)中有這樣一種模式:

簡而言之,理論上,通過這種模式,可以用硬件直接測量出頻率和占空比。當(dāng)時我們發(fā)現(xiàn)這一模式時歡欣鼓舞,以為可以一步解決這一問題。

但是,經(jīng)過測量之后發(fā)現(xiàn)這種方法測試數(shù)據(jù)不穩(wěn)定也不精確,數(shù)據(jù)不停跳動,且和實際值相差很大。ST的這些功能經(jīng)常有這種問題,比如定時器的編碼器模式,在0點處頻繁正負跳變時有可能會卡死。這些方法雖然省事,穩(wěn)定性卻不是很好。

經(jīng)過線性補償可以一定程度上減少誤差(參數(shù)在不同情況下不同):

freq=Frequency*2.2118-47.05;

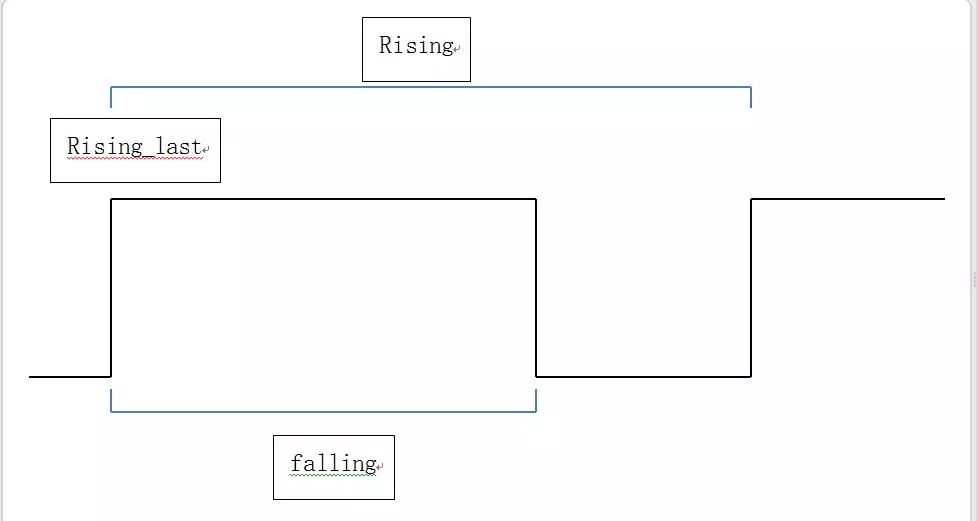

思路三:輸入捕獲

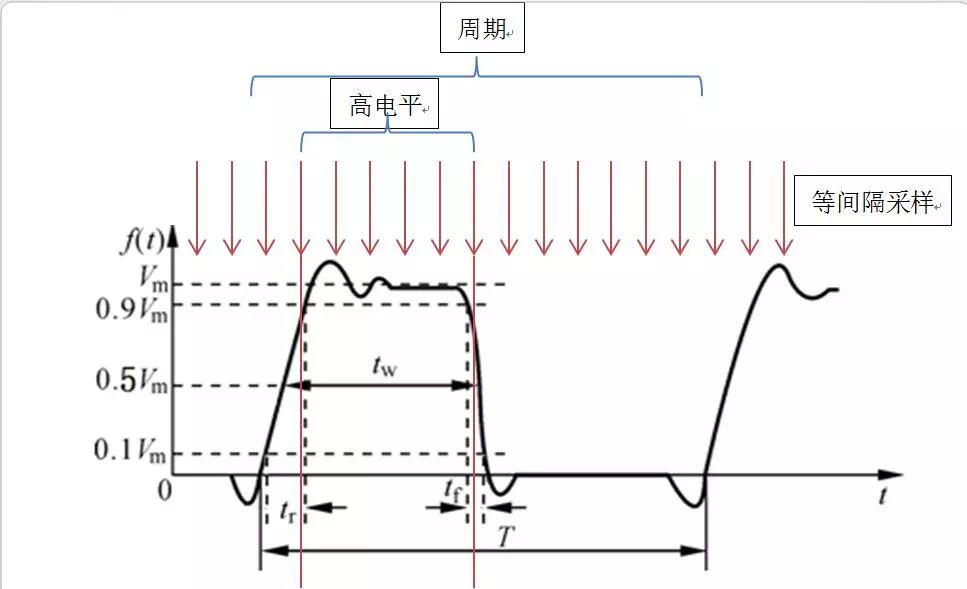

思路:一般來說,對STM32有一定了解的壇友們在測量頻率的問題上往往都會想到利用輸入捕獲。首先設(shè)定為上升沿觸發(fā),當(dāng)進入中斷之后(rising)記錄與上次中斷(rising_last)之間的間隔(周期,其倒數(shù)就是頻率)。再設(shè)定為下降沿,進入中斷之后與上升沿時刻之差即為高電平時間(falling-rising_last),高電平時間除周期即為占空比。

該方法尤其是在中低頻(<100kHz)之下精度不錯。

缺點:稍有經(jīng)驗的朋友們應(yīng)該都能看出來,該方法仍然會帶來極高的中斷頻率。在高頻之下,首先是CPU時間被完全占用,此外,更重要的是,中斷程序時間過長往往導(dǎo)致會錯過一次或多次中斷信號,表現(xiàn)就是測量值在實際值、實際值×2、實際值×3等之間跳動。實測中,最高頻率可以測到約400kHz。

總結(jié):該方法在低頻率(<100kHz)下有著很好的精度,在考慮到其它程序的情況下,建議在10kHz之下使用該方法。同時,可以參考以下的改進程序減少CPU負載。

改進:

前述問題,限制頻率提高的主要因素是過長的中斷時間(一般應(yīng)用情景之下,還有其它程序部分的限制)。所以進行以下改進:

1. 使用2個通道,一個只測量上升沿,另一個只測量下降沿。這樣可以減少切換觸發(fā)邊沿的延遲,缺點是多用了一個IO口。

2. 使用寄存器,簡化程序

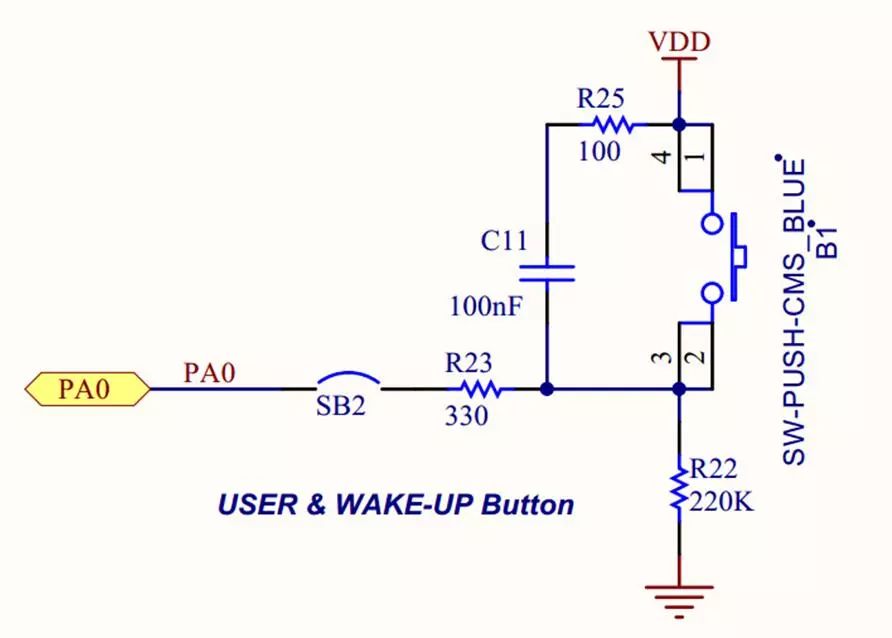

之所以改用TIM2是因為TIM5的CH1(PA0)還是按鍵輸入引腳。本來想來這應(yīng)當(dāng)也沒什么,按鍵不按下不就是開路嘛。但是后來發(fā)現(xiàn)官方開發(fā)板上還有一個RC濾波……

所以,當(dāng)使用別人的程序之前,請一定仔細查看電路圖。

這樣,最高頻率能夠達到約1.1MHz,是一個不小的進步。但是,其根本問題——中斷太頻繁——仍然存在。

解決思路也是存在的。本質(zhì)上,我們實際上只需要讀取CCR1和CCR2寄存器。而在內(nèi)存復(fù)制過程中,面對大數(shù)據(jù)量的轉(zhuǎn)移時,我們會想到什么?顯然,我們很容易想到——利用DMA。所以,我們使用輸入捕獲事件觸發(fā)DMA來搬運寄存器而非觸發(fā)中斷即可,然后將這些數(shù)據(jù)存放在一個數(shù)組當(dāng)中并循環(huán)刷新。這樣,我們可以隨時來查看數(shù)據(jù)并計算出頻率。

改進意見,列出如下:

1.可以設(shè)定僅有通道2進行下降沿捕獲并觸發(fā)中斷,而通道1捕獲上升沿不觸發(fā)中斷。在中斷函數(shù)當(dāng)中,一次讀取CCR1和CCR2。這樣可以節(jié)省大量時間。

2.可以先進行一次測量,根據(jù)測量值改變預(yù)分頻值PSC,從而提高精度

3.間隔采樣。例如每100ms采樣10ms.

這樣的改進應(yīng)當(dāng)能夠?qū)⒆罡卟蓸宇l率增加到2M.但是頻率的進一步提高仍然不可能。因為這時的主要矛盾是中斷函數(shù)時間過長,導(dǎo)致CPU還在處理中斷的時候這一次周期就結(jié)束了,使得最終測量到的頻率為真實頻率的整數(shù)倍左右。示意圖如下:

因此,高頻時仍然推薦以下方法。

思路四:使用外部時鐘計數(shù)器

這種方法是我這幾天回答問題時推薦的方法。思路是配置兩個定時器,定時器a設(shè)置為外部時鐘計數(shù)器模式,定時器b設(shè)置為定時器(比如50ms溢出一次,也可以用軟件定時器),然后定時器b中斷函數(shù)中統(tǒng)計定時器a在這段時間內(nèi)的增量,簡單計算即可。

缺點:

1.無法測量占空比,高頻的占空比測量方法見下文。

2.在頻率較低的情況下,測量精度不如思路3(因為測量周期為100ms,此時如果脈沖周期是200ms……)。

3.輸入幅值必須超過3V。如果不夠或者超出,需要加入前置放大器。

總結(jié):這種方法精度很高,實測在2MHz之下誤差為30Hz也就是0.0015%(由中斷服務(wù)程序引發(fā),可以使用線性補償修正),在25MHz之下也是誤差30Hz左右(沒法達到更高的原因是波形發(fā)生器的最大輸出頻率是25MHz^_^)。同時,從根本上解決了中斷頻率過高的問題。而由于低頻的問題,建議:在低頻時,或者加大采樣間隔(更改TIM7的周期),或者采用思路3的輸入捕獲。

此外,還有一個莫名其妙的問題就是,中斷當(dāng)中如果不加入sprintf(str,"%3.3f",TIM_ExtCntFreq/1000.0)這一句,TIM_ExtCntFreq就始終為0。我猜測是優(yōu)化的問題,但是加入volatile也沒有用,時間不夠就沒有理睬了。

思路五:ADC采樣測量(概率測量法)

一般的高端示波器,測量頻率即是這種方法。簡而言之,高速采樣一系列數(shù)據(jù),然后通過頻譜分析(例如快速傅里葉變換FFT),獲得頻率。F4有著FPU和DSP指令,計算速度上可以接受。但是ADC的采樣頻率遠遠達不到。官方手冊上聲明,在三通道交替采樣+DMA之下,最高可以達到8.4M的采樣率。然而,根據(jù)香農(nóng)采樣定理,采樣頻率至少要達到信號的2倍。2M信號和8.4M的采樣率,即使能夠計算,誤差也無法接受。所以,ADC采樣是無法測量頻率特別是高頻頻率的。

但是,無法測量頻率,卻可以測量占空比,乃至超調(diào)量和上升時間(信號從10%幅值上升到90%的時間)!原理也很簡單,大學(xué)概率課上都說過這個概率基本原理:

當(dāng)采樣數(shù)n趨于無窮時,事件A的概率即趨近于統(tǒng)計的頻率。所以,當(dāng)采樣數(shù)越大,則采樣到的高電平占樣本總數(shù)的頻率即趨近于概率——占空比!

因此,基本思路即是等間隔(速度無所謂,但必須是保證等概率采樣)采樣,并將這些數(shù)據(jù)存入一個數(shù)組,反復(fù)刷新。這樣,可以在任意時間對數(shù)組中數(shù)據(jù)進行統(tǒng)計,獲得占空比數(shù)據(jù)。

缺點:

1.精度低:實測2MHz下誤差約1.3%,低頻時無法統(tǒng)計(比如,頻率10Hz,而ADC采樣時間50ms。這時如果采樣時間中剛好全是高電平,占空比為1……)。

2.內(nèi)存占用大:數(shù)據(jù)池大小為65536,占用了64KB內(nèi)存。

3.有響應(yīng)延遲:測量出來的是“平均占空比”而非“瞬時占空比”。由于我測試時使用的是波形發(fā)生器,輸出波形相當(dāng)穩(wěn)定(1W+的價格畢竟是有它的道理的……),實際應(yīng)用當(dāng)中一般不能夠達到這樣的水平,勢必帶來響應(yīng)延遲(準確說應(yīng)該是采樣系統(tǒng)積分慣性越大)。

4.幅值過低(0.3V)無法測量,過高則超過ADC允許最大值。所以必須視情況使用不同的前置放大器。

實際上使用時如何取舍,就需要看實際情況了。畢竟,這只是低成本下的解決方案而已。

綜上,對這幾種方法做一個總結(jié):

外部中斷:編寫容易,通用性強。缺點是中斷進入頻繁,誤差大。

PWM輸入:全硬件完成,CPU負載小,編寫容易。缺點是不穩(wěn)定,誤差大。

輸入捕獲:可達到約400kHz。低頻精度高,10Hz可達到0.01%以下,400kHz也有3%。缺點是中斷頻繁,無法測量高頻,幅值必須在3.3~5V之間。

外部時鐘計數(shù)器(首選):可達到非常高的頻率(理論上應(yīng)當(dāng)是90MHz)和非常低的誤差(2MHz下為0.0015%且可線性補償)。缺點是低頻精度較低,同樣幅值必須在3.3~5V之間。

ADC采樣頻率測量法:難以測量頻率,高頻下對占空比、上升時間有可以接受的測量精度(2MHz下約1.3%),低頻下無法測量。幅值0.3~3.3V,加入前置放大則幅值隨意。

ADC采樣頻譜分析:高端示波器專用,STM32棄療。

我采用的方法是:首先ADC測量幅值并據(jù)此改變前置放大器放大倍數(shù),調(diào)整幅值為3.3V,同時測量得到參考占空比。而后使用外部時鐘計數(shù)器測量得到頻率,如果較高(>10000)則確認為頻率數(shù)據(jù),同時ADC測量占空比確認為占空比數(shù)據(jù)。否則再使用輸入捕獲方法測量得到頻率、占空比數(shù)據(jù)。

對于各個方法存在的線性誤差,使用了線性補償來提高精度。一般情況下,使用存儲在ROM中的數(shù)據(jù)作為參數(shù),當(dāng)需要校正時,采用如下校正思路:

波形發(fā)生器生成一些預(yù)設(shè)參數(shù)波形(例如10Hz,10%;100K,50%;2M,90%……),在不同區(qū)間內(nèi)多次測量得到數(shù)據(jù),隨后以原始數(shù)據(jù)為x,真實數(shù)據(jù)為y,去除異常數(shù)據(jù)之后,做y=f(x)的線性回歸,并取相關(guān)系數(shù)最高的作為新的參數(shù),同時存儲在ROM當(dāng)中。

-

寄存器

+關(guān)注

關(guān)注

31文章

5325瀏覽量

120052 -

cpu

+關(guān)注

關(guān)注

68文章

10829瀏覽量

211186 -

STM32

+關(guān)注

關(guān)注

2266文章

10876瀏覽量

354925

原文標題:用STM32測量頻率和占空比的幾種方法

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何使用STM32測量頻率和占空比?掌握這三個思路就夠了!

用STM32測量頻率和占空比的幾種方法

實例講解:幾種STM32測量頻率和占空比方式的利與弊

萬用表測量電阻的幾種方法

改變pwm占空比有哪幾種方法

單片機測量PWM占空比有哪幾種方法

STM32檢測信號頻率目標信號

抖動測量的幾種方法

使用STM32測量頻率和占空比的幾種方法

用STM32測量頻率和占空比的幾種方法

如何使用STM32測量頻率和占空比?

用STM32測量頻率和占空比的幾種方法

用STM32測量頻率和占空比的幾種方法

評論