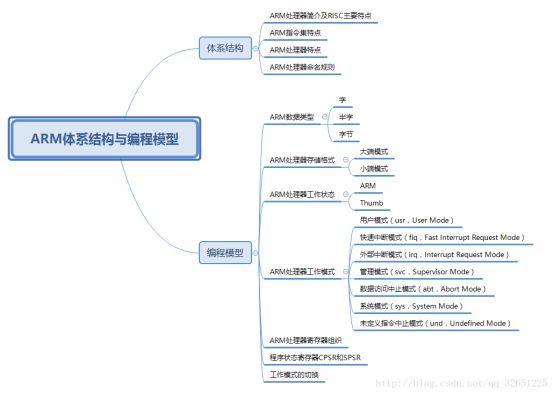

ARM處理器簡介

ARM(Advanced RISC Machines)是一個(gè)32位RISC(精簡指令集)處理器架構(gòu),ARM處理器則是ARM架構(gòu)下的微處理器。ARM處理器廣泛的使用在許多嵌入式系統(tǒng)。ARM處理器的特點(diǎn)有指令長度固定,執(zhí)行效率高,低成本等。

RISC設(shè)計(jì)主要特點(diǎn)

1、指令集——RISC減少了指令集的種類,通常一個(gè)周期一條指令,采用固定長度的指令格式,編譯器或程序員通過幾條指令完成一個(gè)復(fù)雜的操作。而CISC指令集的指令長度通常不固定。

2、流水線——RISC采用單周期指令,且指令長度固定,便于流水線操作執(zhí)行。

3、寄存器——RISC的處理器擁有更多的通用寄存器,寄存器操作較多。例如ARM處理器具有37個(gè)寄存器。

4、Load/Store結(jié)構(gòu)——使用加載/存儲(chǔ)指令批量從內(nèi)存中讀寫數(shù)據(jù),提高數(shù)據(jù)的傳輸效率。

5、尋址方式簡化,指令長度固定,指令格式和尋址方式種類減少。

二、ARM指令集特點(diǎn)

ARM處理器是基于RISC的,但不是純粹的RISC體系結(jié)構(gòu)。為了使ARM處理器能夠更好的滿足嵌入式系統(tǒng)的需要,ARM指令集和單純的RISC指令集有以下幾點(diǎn)不同:

1、一些特定的指令周期數(shù)可變。例如多寄存器裝載或存儲(chǔ)的Load/Store指令執(zhí)行周期就是不確定的,這個(gè)會(huì)根據(jù)相關(guān)的寄存器個(gè)數(shù)而定。如果是訪問連續(xù)的內(nèi)存地址,就可以改善性能,因?yàn)檫B續(xù)的內(nèi)存訪問比隨機(jī)訪問要快。根據(jù)這個(gè)特點(diǎn),由于在函數(shù)的起始和結(jié)尾通常會(huì)有多個(gè)寄存器與內(nèi)存進(jìn)行數(shù)據(jù)交換的操作,因此相應(yīng)操作的指令條數(shù)會(huì)減少,提高了代碼的密度。

2、內(nèi)嵌的桶形移位寄存器產(chǎn)生了更復(fù)雜的指令。桶形移位寄存器是一個(gè)硬件部件,在一個(gè)寄存器被一條指令使用之前,桶形移位寄存器可以處理這個(gè)寄存器中的數(shù)據(jù)。桶形移位寄存器擴(kuò)展了許多指令的功能,以此改善內(nèi)核的性能,提高代碼密度。

3、Thumb16位指令集。ARM處理器有兩種工作狀態(tài),一種是ARM狀態(tài),一種是Thumb狀態(tài)。ARM狀態(tài)下指令長度為32位,Thumb狀態(tài)下指令長度為16位。這種特點(diǎn)使得ARM既能執(zhí)行16位指令,又能執(zhí)行32位指令,從而增強(qiáng)了ARM內(nèi)核的功能。

4、條件執(zhí)行。只有當(dāng)某個(gè)特定條件滿足時(shí)指令才會(huì)被執(zhí)行。這個(gè)特性可以減少分支指令的數(shù)目,從而改善性能,提高代碼密度。

5、增強(qiáng)指令。一些功能強(qiáng)大的數(shù)字信號(hào)處理器(DSP)指令被加入到標(biāo)準(zhǔn)的ARM指令中,以支持快速的16*16乘法操作及飽和運(yùn)算。ARM的這些增強(qiáng)指令,使得ARM處理器不需要加上DSP即可實(shí)現(xiàn)。

三、ARM處理器特點(diǎn)

1、ARM指令都是32位定長的

2、寄存器數(shù)量豐富(37個(gè)寄存器)

3、普通的Load/Store指令

4、多寄存器的Load/Store指令

5、指令的條件執(zhí)行

6、單時(shí)鐘周期中的單條指令完成數(shù)據(jù)移位操作和ALU操作

7、通過變種和協(xié)處理器來擴(kuò)展ARM處理器的功能

8、擴(kuò)展了16位的Thumb指令來提高代碼密度

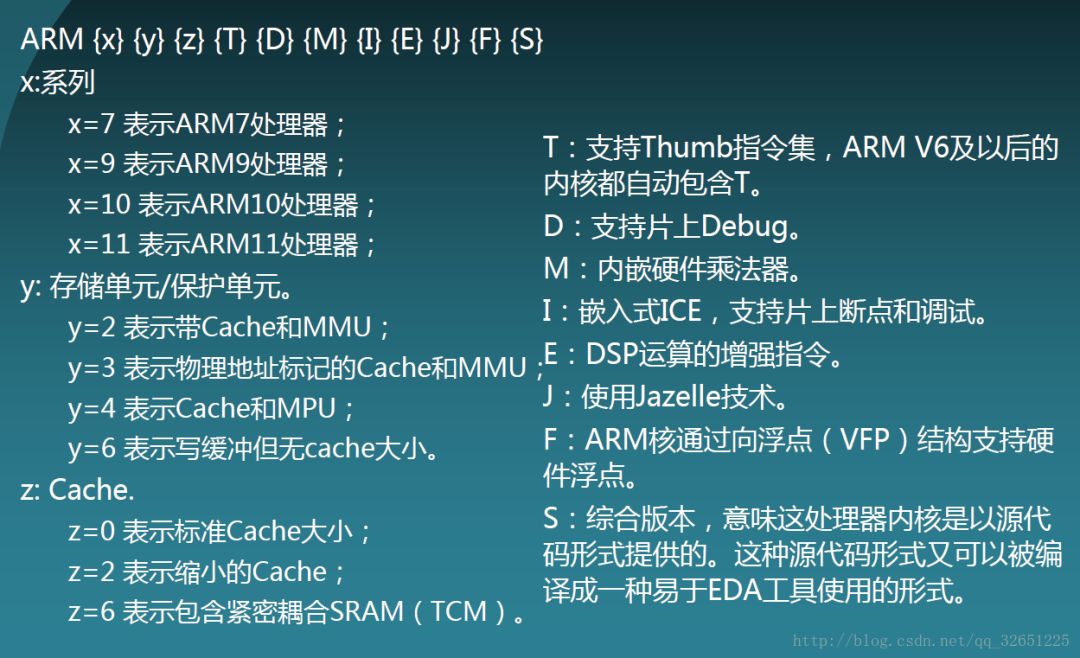

四、ARM處理器命名規(guī)則

ARM編程模型

一、ARM數(shù)據(jù)類型

1、字(Word):在ARM體系結(jié)構(gòu)中,字的長度為32位。

2、半字(Half-Word):在ARM體系結(jié)構(gòu)中,半字的長度為16位。

3、字節(jié)(Byte):在ARM體系結(jié)構(gòu)中,字節(jié)的長度為8位。

二、ARM處理器存儲(chǔ)格式

ARM體系結(jié)構(gòu)將存儲(chǔ)器看作是從0地址開始的字節(jié)的線性組合。作為32位的微處理器,ARM體系結(jié)構(gòu)所支持的最大尋址空間為4GB。

ARM體系結(jié)構(gòu)可以用兩種方法存儲(chǔ)字?jǐn)?shù)據(jù),分別為大端模式和小端模式。

大端模式(高地高低):字的高字節(jié)存儲(chǔ)在低地址字節(jié)單元中,字的低字節(jié)存儲(chǔ)在高地址字節(jié)單元中。

小端模式(高高低低):字的高字節(jié)存儲(chǔ)在高地址字節(jié)單元中,字的低字節(jié)存儲(chǔ)在低地址字節(jié)單元中。

三、ARM處理器工作狀態(tài)

從編程的角度來看,ARM微處理器的工作狀態(tài)一般ARM和Thumb有兩種,并可在兩種狀態(tài)之間切換。

1、ARM狀態(tài):此時(shí)處理器執(zhí)行32位的字對(duì)齊ARM指令,絕大部分工作在此狀態(tài)。

2、Thumb狀態(tài):此時(shí)處理器執(zhí)行16位的半字對(duì)齊的Thumb指令。

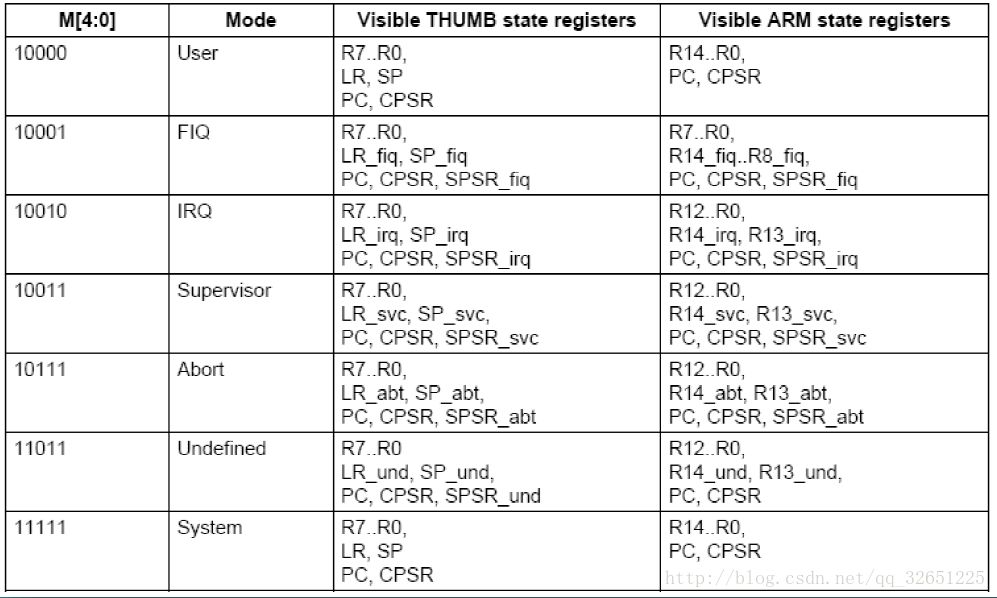

四、ARM處理器工作模式

1、用戶模式(usr,User Mode):ARM處理器正常的程序執(zhí)行狀態(tài)。

2、快速中斷模式(fiq,F(xiàn)ast Interrupt Request Mode):用于高速數(shù)據(jù)傳輸或通道處理。當(dāng)觸發(fā)快速中斷時(shí)進(jìn)入此模式。

3、外部中斷模式(irq,Interrupt Request Mode):用于通用的中斷處理。當(dāng)觸發(fā)外部中斷時(shí)進(jìn)入此模式。

4、管理模式(svc,Supervisor Mode):操作系統(tǒng)使用的保護(hù)模式。在系統(tǒng)復(fù)位或執(zhí)行軟件中斷指令SWI時(shí)進(jìn)入。

5、數(shù)據(jù)訪問中止模式(abt,Abort Mode):當(dāng)數(shù)據(jù)或指令預(yù)取中止時(shí)進(jìn)入該模式,可用于虛擬存儲(chǔ)及存儲(chǔ)保護(hù)。

6、系統(tǒng)模式(sys,System Mode):運(yùn)行具有特權(quán)的操作系統(tǒng)任務(wù)。

7、未定義指令中止模式(und,Undefined Mode):當(dāng)未定義的指令執(zhí)行時(shí)進(jìn)入該模式,可用于支持硬件協(xié)處理器的軟件仿真。

除了用戶模式之外,其余六種模式都是特權(quán)模式。除了用戶模式和系統(tǒng)模式之外,其余五種模式都是異常模式。

在特權(quán)模式下程序可以訪問所有的系統(tǒng)資源。非特權(quán)模式和特權(quán)模式之間的區(qū)別在于有些操作只能在特權(quán)模式下才被允許,例如直接改變模式和中斷使能等。而且為了保證數(shù)據(jù)安全,一般MMU會(huì)對(duì)地址空間進(jìn)行劃分,只有特權(quán)模式才能訪問所有的地址空間。而用戶模式如果需要訪問硬件,必須切換到特權(quán)模式下,才允許訪問硬件。

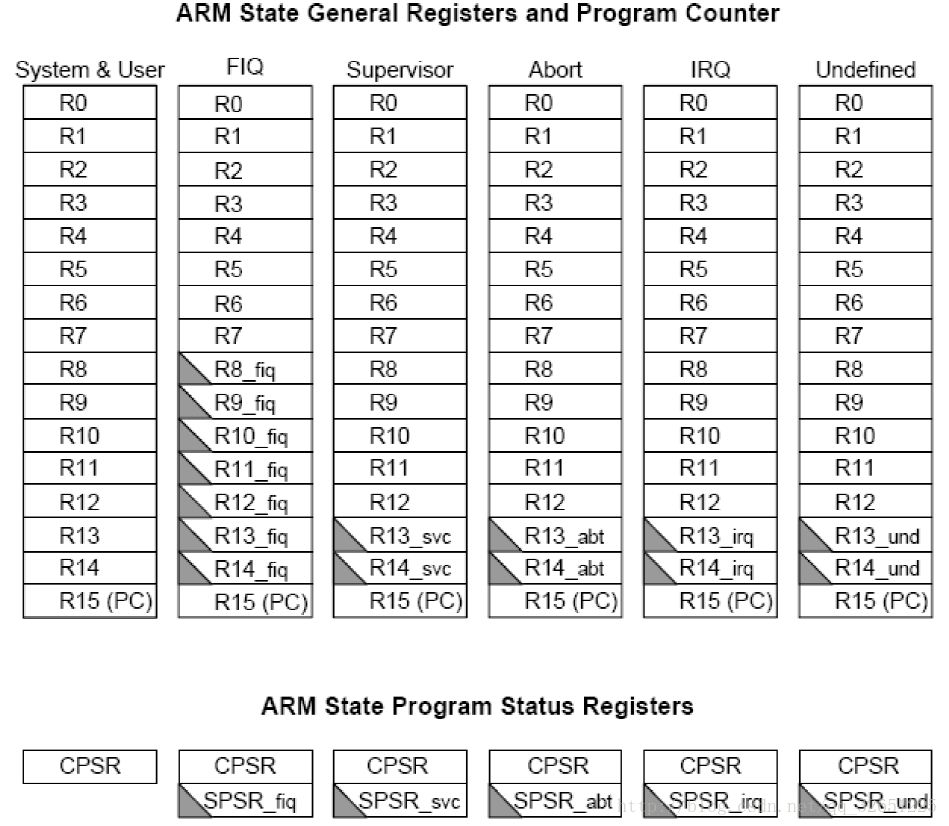

五、ARM處理器寄存器組織

ARM共有37個(gè)32位寄存器,其中31個(gè)為通用寄存器,6個(gè)為狀態(tài)寄存器,包括R0-R15,R8_fiq-R14_fiq,R13_svc,R14_svc,R13_abt,R14_abt,R13_irq,R14_irq,R13_und,R14_und,CPSR,SPSR_fiq,SPSR_svc,SPSR_abt,SPSR_irq,SPSR_und。如圖。

通用寄存器包括R0-R15,可以分為3類:

1、未分組寄存器R0-R7

在所有運(yùn)行模式下,未分組寄存器都指向同一個(gè)物理寄存器,他們未被系統(tǒng)用作特殊的用途。因此在中斷或異常處理進(jìn)行異常模式轉(zhuǎn)換時(shí),由于不同的處理器運(yùn)行模式均使用相同的物理寄存器,所以可能造成寄存器中數(shù)據(jù)的破壞。

2、分組寄存器R8-R14

對(duì)于分組寄存器,他們每次所訪問的物理寄存器都與當(dāng)前的處理器運(yùn)行模式相關(guān)。具體如上圖。

R13常用作存放堆棧指針,用戶也可以使用其他寄存器存放堆棧指針,但在Thumb指令集下,某些指令強(qiáng)制要求使用R13存放堆棧指針。

R14稱為鏈接寄存器(LR,Link Register),當(dāng)執(zhí)行子程序時(shí),R14可得到R15(PC)的備份,執(zhí)行完子程序后,又將R14的值復(fù)制回PC,即使用R14保存返回地址。

3、程序計(jì)數(shù)器PC(R15)

寄存器R15用作程序計(jì)數(shù)器(PC),在ARM狀態(tài)下,位[1:0]為0,位[31:2]用于保存PC;在Thumb狀態(tài)下,位[0]為0,位[31:1]用于保存PC。

由于ARM體系結(jié)構(gòu)采用了多級(jí)流水線技術(shù),對(duì)于ARM指令集而言,PC總是指向當(dāng)前指令的下兩條指令的地址,即PC的值為當(dāng)前指令的地址值加8個(gè)字節(jié)。

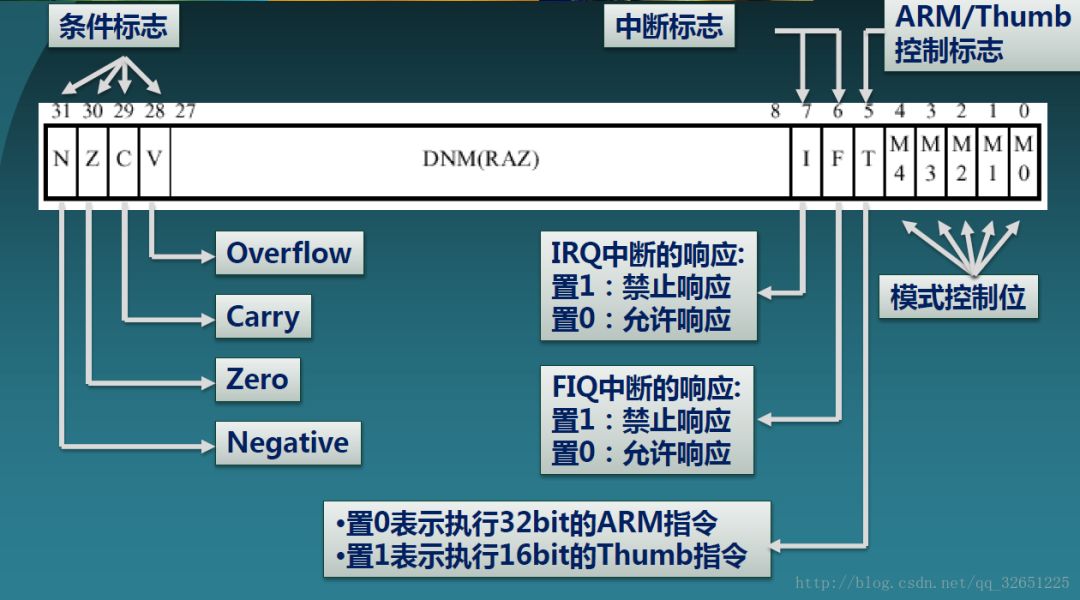

六、程序狀態(tài)寄存器CPSR和SPSR

CPSR(Current Program Status Register,當(dāng)前程序狀態(tài)寄存器),CPSR可在任何運(yùn)行模式下被訪問,它包括條件標(biāo)志位、中斷禁止位、當(dāng)前處理器模式標(biāo)志位以及其他一些相關(guān)的控制和狀態(tài)位。

每一種運(yùn)行模式下都有一個(gè)專用的物理狀態(tài)寄存器,稱為SPSR(Saved Program Status Register,備份的程序狀態(tài)寄存器),當(dāng)異常發(fā)生時(shí),SPSR用于保存當(dāng)前CPSR的值,從異常退出時(shí)則可由SPSR來恢復(fù)CPSR。

由于用戶模式和系統(tǒng)模式不屬于異常模式,這兩種狀態(tài)下沒有SPSR,因此在這兩種狀態(tài)下訪問SPSR,結(jié)果是未知的。

CPSR保存數(shù)據(jù)的結(jié)構(gòu):

1、N(Negative):當(dāng)用兩個(gè)補(bǔ)碼表示的帶符號(hào)數(shù)進(jìn)行運(yùn)算時(shí),N=1表示結(jié)果為負(fù),N=0表示結(jié)果為正數(shù)或零

2、Z(Zero):Z=1表示運(yùn)算結(jié)果為0,Z=0表示運(yùn)算結(jié)果非零

3、C(Carry):有4種方法可以設(shè)置C的值:

(1)加法指令(包括比較指令CMP)

(2)當(dāng)運(yùn)算產(chǎn)生進(jìn)位時(shí)(無符號(hào)數(shù)溢出),C=1,否則C=0

(3)減法運(yùn)算(包括比較指令CMP)

(4)當(dāng)運(yùn)算產(chǎn)生了借位(無符號(hào)數(shù)溢出),C=0,否則C=1

對(duì)于包含移位操作的非加/減運(yùn)算指令,C為移出值的最后一位。對(duì)于其他的非加/減運(yùn)算指令,C的值通常不變。

4、V(Overflow):有2種方法設(shè)置V的值:

(1)對(duì)于加/減法運(yùn)算指令,當(dāng)操作數(shù)和運(yùn)算結(jié)果為二進(jìn)制的補(bǔ)碼表示的帶符號(hào)數(shù)時(shí),V=1表示符號(hào)位溢出。

(2)對(duì)于其他的非加減法運(yùn)算指令,V的值通常不變。

5、I(Interrupt Request):I=1表示禁止響應(yīng)irq,I=0表示允許響應(yīng)

6、F(Fast Interrupt Request):F=1表示禁止響應(yīng)fiq,F(xiàn)=0表示允許響應(yīng)

7、T(Thumb):T=0表示當(dāng)前狀態(tài)位ARM狀態(tài),T=1表示為Thumb狀態(tài)

8、M4-M0:表示當(dāng)前處理器的工作模式,如圖:

七、工作模式的切換

(1)執(zhí)行軟中斷(SWI)或復(fù)位命令(Reset)指令。如果在用戶模式下執(zhí)行SWI指令,CPU就進(jìn)入管理(Supervisor)模式。當(dāng)然,在其他模式下執(zhí)行SWI,也會(huì)進(jìn)入該模式,不過一般操作系統(tǒng)不會(huì)這么做,因?yàn)槌擞脩裟J綄儆诜翘貦?quán)模式,其他模式都屬于特權(quán)模式。執(zhí)行SWI指令一般是為了訪問系統(tǒng)資源,而在特權(quán)模式下可以訪問所有的系統(tǒng)資源。SWI指令一般用來為操作系統(tǒng)提供API接口。

(2)有外部中斷發(fā)生。如果發(fā)生了外部中斷,CPU就會(huì)進(jìn)入IRQ或FIQ模式。

(3)CPU執(zhí)行過程中產(chǎn)生異常。最典型的異常是由于MMU保護(hù)所引起的內(nèi)存訪問異常,此時(shí)CPU會(huì)切換到Abort模式。如果是無效指令,則會(huì)進(jìn)入U(xiǎn)ndefined模式。

(4)有一種模式是CPU無法自動(dòng)進(jìn)入的,這種模式就是System模式,要進(jìn)入System模式必須由程序員編寫指令來實(shí)現(xiàn)。要進(jìn)入System模式只需改變CPSR的模式位為System模式對(duì)應(yīng)的模式位即可。進(jìn)入System模式一般是為了利用System模式和用戶模式下的寄存器相同的特點(diǎn),因此一般情況下,操作系統(tǒng)在通過SWI進(jìn)入Supervisor模式后,做一些操作后,就進(jìn)入System模式。

(5)在任何特權(quán)模式下,都可以通過修改CPSR的MODE域來進(jìn)入其他模式。不過需要注意的是由于修改的CPSR是該模式下的影子CPSR,即SPSR,因此并不是實(shí)際的CPSR,所以一般的做法是修改影子CPSR,然后執(zhí)行一個(gè)MOVS指令來恢復(fù)執(zhí)行某個(gè)斷點(diǎn)并切換到新模式。

推薦閱讀:

1.從一個(gè)不起眼的小公司逐漸成為半導(dǎo)體行業(yè)巨頭,Microchip CEO史蒂夫桑吉不一般的“擴(kuò)張”之路

2.這是一篇非常不錯(cuò)的介紹U-boot工作機(jī)制的好文

3.我們吃蛋糕,手中的盤子小,卻可以吃掉大蛋糕,RAM就是這樣運(yùn)行比自身更大的程序

4.超實(shí)用!一位嵌入式高手摸索出的Linux內(nèi)核編譯步驟和經(jīng)驗(yàn)

-

處理器

+關(guān)注

關(guān)注

68文章

19165瀏覽量

229135 -

ARM

+關(guān)注

關(guān)注

134文章

9046瀏覽量

366820 -

編程

+關(guān)注

關(guān)注

88文章

3592瀏覽量

93596

原文標(biāo)題:圖文并茂?一圖了解?其實(shí)這是一個(gè)ARM體系結(jié)構(gòu)與編程模型的總結(jié)

文章出處:【微信號(hào):gh_c472c2199c88,微信公眾號(hào):嵌入式微處理器】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Microarchitecture指令集體系結(jié)構(gòu)

了解體系結(jié)構(gòu) - 介紹 Arm 體系結(jié)構(gòu)

Arm的DRTM體系結(jié)構(gòu)規(guī)范

ARM SoC體系結(jié)構(gòu)(中文版)

ARM體系結(jié)構(gòu)與編程_杜春雷

ARM體系結(jié)構(gòu)與程序設(shè)計(jì)

ARM體系結(jié)構(gòu)和應(yīng)用系統(tǒng)設(shè)計(jì)示例

米爾科技ARM體系結(jié)構(gòu)與編程介紹

ARM體系結(jié)構(gòu)與編程模型的總結(jié)

ARM體系結(jié)構(gòu)與編程模型的總結(jié)

評(píng)論