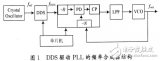

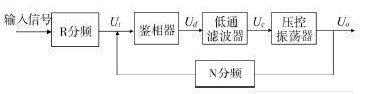

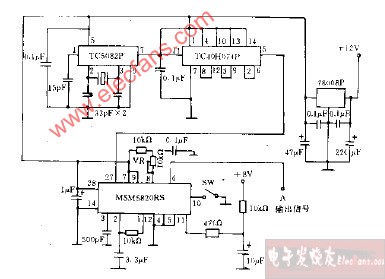

下圖所示的是用Q2230激勵鎖相倍頻系統(tǒng)實(shí)現(xiàn)的一個實(shí)際的頻率合成器。系統(tǒng)時鐘采用40 MHz,這樣能輸出DC~15 MHz、分辨率為0.01 Hz、電壓峰一峰值為10 V的正弦波。譜純度優(yōu)于一70 dB,能輸出DC~60 MHz的TTL信號,具有AM、FM、FSK、DPSK調(diào)制功能。

1. 40 MHz高穩(wěn)定基準(zhǔn)時鐘

為了合成器輸出信號的高質(zhì)量,40 MHz時鐘是用一個高穩(wěn)定度5 MHz(優(yōu)于l0-9/s)的恒溫晶體振蕩器,通過8倍頻PLL系統(tǒng)獲得的。其中PLL的VCO采用40 MHz晶體振蕩器,以保證系統(tǒng)時鐘有足夠高的頻譜純度和頻率穩(wěn)定度。

2.微處理器控制系統(tǒng)

以8031為核心構(gòu)成的微處理器控制系統(tǒng)包含鍵盤顯示單元、串行通信口和CPU單元,實(shí)現(xiàn)調(diào)制控制電路(FM、FSK、DPSK)、幅度控制DAC、直流偏置、電平比較、輸出切換諸電路以及面板功能和顯示控制功能。

3.TTL比較器

TTL比較器A完成DC~15 MHz TTL電平輸出。TTL比較器B獲得的TTL電平反饋到CPU單元與電平比較DAC,得到正弦輸出幅度的標(biāo)準(zhǔn)功能。

4. 15~60 MHz PLL系統(tǒng)

15~60 MHz是一個4倍頻鎖相系統(tǒng),通過切換控制,在TTL輸出口可獲得DC~60 MHz的TTL信號。

-

頻率合成器

+關(guān)注

關(guān)注

5文章

218瀏覽量

32331 -

Q2230

+關(guān)注

關(guān)注

0文章

2瀏覽量

2278

發(fā)布評論請先 登錄

相關(guān)推薦

關(guān)于相位鎖定環(huán)(PLL)頻率合成器的設(shè)計和分析

詳解頻率合成器高性能架構(gòu)的實(shí)現(xiàn)

基于DDS的頻率合成器設(shè)計介紹

如何利用FPGA設(shè)計PLL頻率合成器?

DDS PLL短波頻率合成器設(shè)計

ADI發(fā)布新款PLL合成器,用于實(shí)現(xiàn)高性價比FMCW雷達(dá)系統(tǒng)

頻率合成器,頻率合成器原理及作用是什么?

基于DDS驅(qū)動PLL結(jié)構(gòu)的寬帶頻率合成器的設(shè)計與實(shí)現(xiàn)

基于FPGA與PLL頻率合成技術(shù)設(shè)計的整數(shù)/半整數(shù)頻率合成器

Q2230+PLL實(shí)現(xiàn)的頻率合成器

Q2230+PLL實(shí)現(xiàn)的頻率合成器

評論