MY-I.MX6系列核心板,只需要一個5V電源(持續供電電流不低于2A,峰值2.5A-3A)輸入即可。詳見下圖。

MY-I.MX6seriesofcoreboardonlyneeds5Vpowersource(constantcurrentisnotsmallthan2A,peakvalue2.5A-3A)asaninput。detailsasbelow。

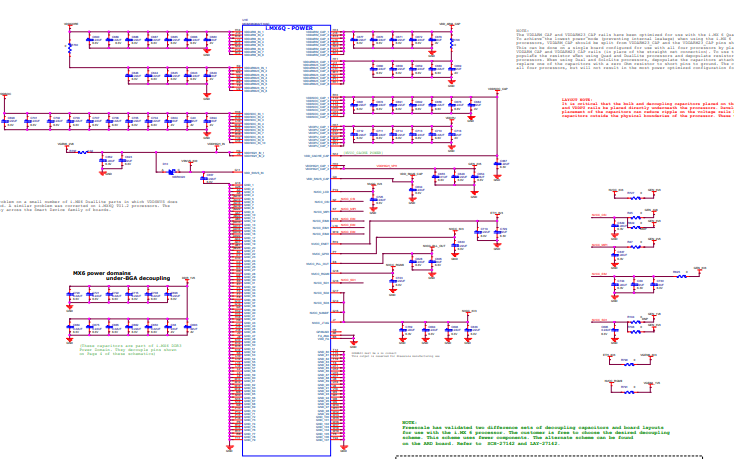

如果是直接的5V輸入,5V的電源一定要做過壓保護,過壓保護電路參考如下。

ifitisadirect5Vinput,5Vpowersourceneedaovervoltageprotection,theprotectioncircuitcanbedesignedwithfollowingreference。

如果是高電壓輸入通過DCDC轉換成5V,核心板會輸出一個3P3V的電源,此電源的電流不超過500mA。如果底板上面3.3V的電流非常小,可以直接采用此3P3V作為底板的供電電源,如果用3P3V作為底板供電電源,請在3P3V電源上串上500mA的保險絲。

ifitishighvoltageinputtobeconvertedto5VthroughDCDCprinciple,thecoreboardwilloutput3P3Vpowersourcewithamaximumcurrent500mAofwhichcanbeusedaspowersupplyforbaseboardifcurrentwith3.3Vonthebaseboardistoosmall,inthiscase,pleaseputinserialafuseforthis3P3Vpowersource。

由于底板上面的3.3V電壓通常會超過500mA,一般用戶會單獨通過DCDC或者LDO產生3.3V。

sincecurrentwith3.3Vonthebaseboardisusuallyover500mA,normallyuserswillgenerateaanother3.3VthroughDCDCorLDO。

注意:底板的3.3V的電源,一定要通過核心板的3P3V來做使能控制,而不能夠直接由底板上面的其他電源產生。如果底板上面還有其他電源,也必須有3P3V來做使能控制。此點是由于I.MX6芯片決定的。

note:enablecontrolmustbedonefor3.3Vonbaseboardby3P3Voncoreboardinsteadofbeingconductedbyotherpowersourcesonthebaseboard.ifthereareotherpowersourcesonbaseboard,theirenablecontrolsmustbeconductedby3P3Vaswell,thisisuptothenatureofI.MX6chip。

參考電路如下:

referencecircuitasbelow:

核心板5V電源輸入處要放置大的儲能電容,確保CPU在瞬間增加負載的時候不至于斷電。如果有過孔,確保過孔的電流至少能夠通過3A的峰值電流,可以多打一些過孔增加電流。

capacitorwithbigcapacityshouldbeplacednear5Vinputoncoreboard,toensurecontituouspowersupplyevenwhensuddenextraloadisaddedforCPU。ifthereisviahole,needtomakesureviaholecangothrough3Apeakcurrent,moreviaholescanbebuilttoincreasecurrent。

串口設計(serialportdesign)原理(principle)

串口設計上面,經常會碰到的問題是RXD跟TXD的方向接反。參考原理圖中的網標表示如下

forserialportdesign,commonquestionsarisingareinversionbetweenRXDandTXD。networkstandardintheschematicasbelow

TXD——CPU輸出

TXD——CPUoutput

RXD——CPU輸入

RXD——CPUinput

PCB

注意:在設計底板的時候,我司提供了底板的原理圖和PCB圖,串口我司采用的是母頭的接口。務必確保用戶在設計的時候也使用的是母頭,如果要更換成公頭。RS232信號要更換。公頭母頭的詳細信息請上網查詢

note:wecanprovideschematicandPCBdiagramfordesignofbaseboard,ourserialportisfemaleheadasconnector.pleaseassureyourdesigntobeconsistentwithouroffer,ifchangeserialporttobemaleheadconnector,thenRS232siganlconnectorheadneedtobechangedaccordingly.Forthedetailsofmaleandfemaleheadconnector,pleasegetoninternetforconsuls.

SD卡設計(SDcarddesign)原理(principle)

用戶在設計SD卡的時候,針對IO的上下拉,請嚴格參考原理圖,過多的上下拉可能會導致SD卡不能夠正常的工作。參考圖見下面

forusers‘designofSDcard,pleasefollowstrictlyschematictoarrangeIOdropdown,excessivedropdownwillenableSDcardnottoworknormally。referencediagramasbelow

注意:如果用戶不需要SD卡,要換成TF卡,由于TF卡是沒有寫保護這個功能的。寫保護信號(SD3_RST/SD3_WP)要下拉,而不能夠直接懸空。如果TF卡選用的是熱插拔卡座,一定要清楚TF卡的檢測管腳是哪個。一般情況是插卡之后,檢測管腳接地,此時插入檢測管腳(KEY_COL/SD3_CD_B)要上拉。如果TF卡選擇的是翻蓋式非可插拔卡座。寫保護信號上拉,同時插入檢測信號要接地(相當于始終插入了卡)

note:ifusersdon’tneedSDcard,butneedTFcard,sinceTFcarddoesn‘thavefunctionofwrite-protect.Write-protectsignal(SD3_RST/SD3_WP)needtopulldown,whichcan’tbehangeddirecltyintheair.IfTFcardboothisdesignedwithhotswap,mustmakeclearwhichpinofTFcardisfordectetion。normallywheninsertthecard,detectionpinwillbegrounded,theinserteddetectionpinKEY_COL/SD3_CD_B)needtopullup.IfTFcardboothisdesignedwithfliptype,write-protectneedtopullup,atthesametimetheinserteddetectionsignalneedtobegrounded(justasacardiskeptinthebooth)

如果要增加ESD保護。確保接在SD_CLK信號上的ESD的電容值很小。

ifneedadditionalESDprotect,pleaseensureasmallcapacityvalueonSD_CLKsignal。

PCB

SD0,SD1,SD2,SD3,CMD,CLK信號要做等長處理。ESD原件要跟SD卡座非常接近。

SD0,SD1,SD2,SD3,CMD,CLKsignalneedanequaltreatment。ESDoriginalsneedtobeveryclosetoSDcardbooth。

SATA設計(SATAdesign)原理(principle)

SATA的原理相對簡單,確保方向正確。由于一般SATA盤的電流比較大,5V輸入電流要不低于3A為好。

SATAprincipleissimplebycontrast,onlyneedtoensureacorrectdirection.sincecurrentonSATAisnormallyalittlebig,5Vcurrentinputedisbetternottobeaslowas3A。

PCB

SATA信號上面串聯的4個電容要緊挨SATA座。

thefourcapacitorswhichareserialedtoSATAsignalshouldbeclosetoSATAbooth。

100歐姆的差分阻抗匹配

100ohmdifferenceresistancematchingup

每組差分對之間的長度誤差控制在±5mil

lengthtoleranceforeachgroupofdifferencespairsiscontrolledwithin±5mil

要求完整參考地平面

requireafullreferencetogroundlevel

HDMI原理(principle)

HDMI座子不能夠接錯定義

HDMIstandcan‘tbelinkedwithwrongdefinition

PCB

100歐姆差分阻抗匹配。

100ohmdifferenceresistancematchingup。

每組差分對之間的長度誤差控制在±5mil

lengthtoleranceforeachgroupofdifferencespairsiscontrolledwithin±5mil

要求完整參考地平面

requireafullreferencetogroundlevel

保護器件CM2020一定不要省略。

protectcomponentCM2020can’tbeignored。

LVDS原理(principle)

LVDS信號如果傳輸距離比較遠,接的屏幕比較大,LVDS信號上面可以串聯耦合磁珠,能夠保證傳輸的質量更好。

iftransmittingdistanceforLVDSsignalislong,andscreenlinkedwithisbig接的屏幕比較大,amagneticcouplingcanbeputinserialonLVDSsignalforabettertransmitingquality。

PCB

100歐姆的差分阻抗匹配。

100ohmdifferenceresistancematchingup。

每組差分對之間的長度誤差控制在±5mil

lengthtoleranceforeachgroupofdifferencespairsiscontrolledwithin±5mil

如果用雙路LVDS信號做1080p的顯示。LVDS0跟LVDS1的信號要做等長處理。

iftwowayLVDSsinglaisusedfor1080pdispla,。LVDS0andLVDS1signalneedanequaltreatment。

要求完整參考地平面

requireafullreferencetogroundlevel

RGB接口LCD(RGBportLCD)原理(principle)

RGB接口的LCD滿足24bit,18bit的接口模式

LCDasRGBportneedtobematchedupwithinterfacemodelwith24bit,18bit

CPU信號(注1)

(CPUsignal(note1))24bit(注2)

(24bit(note2))18bit(注3)

(18bit(note3))18bit(注4)

(18bit(note4))

D0B0B0

D1B1B1

D2B2B0B2

D3B3B1B3

D4B4B2B4

D5B5B3B5

D6B6B4G0

D7B7B5G1

D8G0G2

D9G1G3

D10G2G0G4

D11G3G1G5

D12G4G2R0

D13G5G3R1

D14G6G4R2

D15G7G5R3

D16R0R4

D17R1R5

D18R2R0

D19R3R1

D20R4R2

D21R5R3

D22R6R4

D23R7R5

注1(note1)。

D0表示CPU的液晶接口最低位,

D0indicateaminimallevelforCPUliquidcrystalport,

D23表示CPU的液晶接口最高位

D23indicateamaximallevelforCPUliquidcrystalport

注2(note2)

B0-24位液晶藍色位最低位,

B0-24bitbluebitofliquidcrystalatminimallevel,

B7-24位液晶藍色位最高位

B7-24bitbluebitofliquidcrystalatmaximallevel,

G0-24位液晶綠色位最低位,

G0-24bitgreenbitofliquidcrystalatminimallevel,

G7-24位液晶綠色位最高位

G7-24bitgreenbitofliquidcrystalatmaximallevel

R0-24位液晶紅色位最低位,

R0-24bitredbitofliquidcrystalatminimallevel,

R7-24位液晶紅色位最高位

R7-24bitredbitofliquidcrystalatmaximallevel

注3(note3)。

采用此接法,LCD軟件還是選用24bit模式

inuseofthiskindoflink,LCDsoftwarestillchoose24bitmodel

B0-18位液晶藍色位最低位,

B0-18bitbluebitofliquidcrystalatminimallevel,

B5-18位液晶藍色位最高位

B5-18bitbluebitofliquidcrystalatmaximallevel

G0-18位液晶綠色位最低位,

G0-18bitgreenbitofliquidcrystalatminimallevel,

G5-18位液晶綠色位最高位

G5-18bitgreenbitofliquidcrystalatmaximallevel

R0-18位液晶紅色位最低位,

R0-18bitredbitofliquidcrystalatminimallevel,

R5-18位液晶紅色位最高位

R5-18bitredbitofliquidcrystalatmaximallevel

注4(note4)。

采用此接法,LCD軟件要改成選用18bit模式

ifinuseofthislinkmethod,LCDsoftwareneedtochoose18bitmodel

B0-18位液晶藍色位最低位,

B0-18bitbluebitofliquidcrystalatminimallevel,

B5-18位液晶藍色位最高位

B5-18bitbluebitofliquidcrystalatmaximallevel

G0-18位液晶綠色位最低位,

G0-18bitgreenbitofliquidcrystalatminimallevel,

G5-18位液晶綠色位最高位

G5-18bitgreenbitofliquidcrystalatmaximallevel

R0-18位液晶紅色位最低位,

R0-18bitredbitofliquidcrystalatminimallevel,

R5-18位液晶紅色位最高位

R5-18bitredbitofliquidcrystalatmaximallevel

如果靜電要求非常嚴格,LCD信號上面要做ESD防護。

ifthereisastrictrequestwithstatic,needESDprotectforLCDsignal。

PCB

所有的數據線,CLK信號要做等長處理

foralldatalines,needanequaltreatmentforCLKsignal

要求完整參考地平面

requestafullreferencetogroundlevel

CMOS原理(principle)

PCB

MCLK和PIXCLK信號頻率非常高,Layout時要做地隔離處理

sincefrequencyofMCLKandPIXCLKsignalisveryhigh,needisolationtreatmentwhenLayout

數據,clk信號要做等長處理。

data,needanequaltreatmentforclksignal。

要求完整參考地平面

requestafullreferencetogroundlevel

USB原理(principle)

USBHOST通過LAN9514擴展了4和USBHOST,同時擴展了1路10M/100M的以太網接口。

USBHOSTexpandedwith4andUSBHOSTviaLAN9514,andexpandedwithoneway10M/100Methernetinterface。

USB線上串耦合電感。

acouplinginductanceisputinserialonUSBline。

核心板的USB_H1_VBUS信號要通過磁珠接5V電源。

核心板的USB_H1_VBUSsignalofcoureboardneedtobeconnectedwith5Vpowersupplythroughmagneticbead。

對外做HOST供電時,要采用USB過流保護器件。

ifpowersupplyHostoutoftheboard,pleaseincludeover-currentprotectcomponentforUSD。

目前的MINIUSB口硬件設計上只能夠做device口,如果要做HOST功能,請參考FSL官方的OTG設計即可。

sofaronlydeviceportcanbedoneinlayoutofhardwareforMINIUSBport,ifneedfunctionofHOST,pleaserefertoOTGlayoutfromFSLofficial。

PCB

90歐姆的差分阻抗匹配

90ohmdifferenceresistancematchingup

要求完整參考地平面

requestafullreferencetogroundlevel

對外供電的電流足夠大。

currenttosupplyoutsideneedtobebigenough。

CAN原理(principle)

由于CAN的TX,RX信號是3.3V電平,注意電平轉換。

sinceCAN的TX,RXsignalis3.3Velectricallevel,attentiontoconversionofelectricallevel。

PCB

CANH,CANL查分信號。

CANH,CANLchecksignal。

PCIE原理(principle)

TX,RX信號要串聯0.1uF電容(外接模塊上面如果RX信號已經串聯了電容,不需要再次串聯)

TX,RXsignalneedtoconnectinserialwith0.1uFcapacitor(ifanexternalmoduleisalreadywithacapacitorinserial,thennoneedtoconnectacapacitoragain)

CLK信號上串聯0.1uF電容,同時在電容后端并聯一個49.9歐姆的對地電阻。

CLKsignalconnectinserialwith0.1uFcapacitor,atthesametimeputa49.8resistortogroundinparallelwithanotherendofthecapacitor。

PCB

85歐姆的差分阻抗匹配

85ohmdifferenceresistancematchingup

要求完整參考地平面

requestafullreferencetogroundlevel

-

iMX6

+關注

關注

1文章

33瀏覽量

13648

發布評論請先 登錄

相關推薦

iTOP-iMX6PLUS開發板-v_2.3底板擴展串口

NXP iMX8和iMX6 ARM處理器網絡性能對比分析

iMX6板子gpio引腳的讀寫配置

iMX6開發板設備樹文件分析

iMX6常見 Android系統問題

基于imx6處理器的核心板及底板的6層PCB設計原理圖與全3D封裝圖紙

IMX6 MfgTool燒錄指導手冊

iMX6系列-iMX6Q 開發板 Python 移植

IMX6底板設計指南

IMX6底板設計指南

評論