Question:

Come up with logic that counts number of ‘1’s in a 7 bit wide vector.You can only use combinational logic.

Answer:

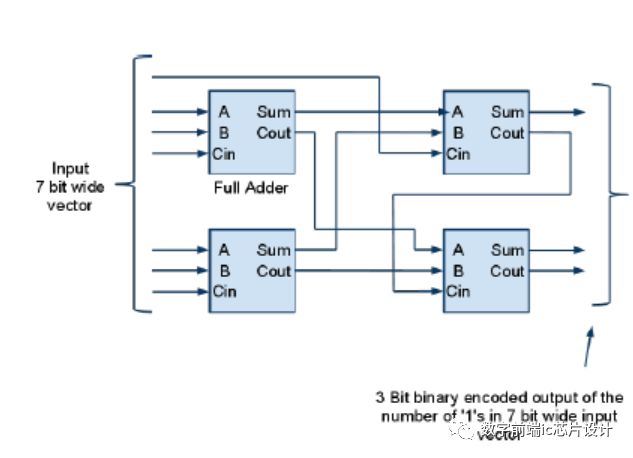

Following is one of the ways to come up with such logic.

Input vector is 7 bit wide. To sum up 7 bits we need 3 bits of binary encoded output.We’ve full adders available. A single full adder can add 3 input bits and generate 2 bitsof binary encoded output.E.g. a full adder can add 3 bit wide input vector ‘111’ and generate ‘11’ output.We can pick two full adders and add up 6 bits of the input vector and will end up withtwo sets of two bit wide binary encoded data.E.g. if input vector is ‘1100111’, we can assume two full adders adding up first 6bits ‘110011’ where first three bits ‘110’ are input to first adder and ‘011’ are inputto second adder. First adder will output ‘10’ (decimal 2) and second adder will alsooutput ‘10’ (decimal 2), and we need to add up two two bit binary vectors. We canagain employ full adders to do this as we still have to account for the 7th input bit ofthe input vector. That can go into the least significant full adder carry-input.

For the above example :

Input vector ‘1100111’

input ‘110’ => full adder => ‘10’ output

input ‘011’ => full adder => ‘10’ output

10

+10

------

100 => output (4)

Now accounting for the seventh input bit ‘1’ as carry into the least significant adder.

1 <= Carry in.

10

+10

-----

101 => Binary encoded decimal 5 which is the input of 1s in inputvector ‘1100111’.

Full adders can be used to add-up 3 input bits at a time. Outputs of first level of fulladders represent the two bit encoded version of the total ‘1’s count, which we need toadd up get the final two digit encoded version of total ‘1’s. Since we need to add up7 bit inputvector, 7th input vector can be used as ‘Carry In’ in the second level of fulladders.

-

asic

+關注

關注

34文章

1194瀏覽量

120340

原文標題:北美ASIC經典面試試題(2)

文章出處:【微信號:ic_frontend,微信公眾號:數字前端ic芯片設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

北美認證指南:一文解讀PTCRB與北美三大運營商

ASIC集成電路如何提高系統效率

程序員去面試只需一個技能征服所有面試官!

北美UL認證屬于什么性質?申請流程分享

北美FCC認證是強制性的嗎?哪些產品需要做?

申請北美運營商有什么條件?哪些產品需要申請北美PTCRB認證?

產品申請北美運營商AT T認證的優勢有哪些

走進北美運營商認證:解讀PTCRB與北美三大運營商的關系

北美FCC認證中包含哪些測試項目?

產品如何進軍北美市場?北美FCC認證指南

平板電腦申請北美FCC認證的流程有哪些?

北美ASIC經典面試試題

北美ASIC經典面試試題

評論