隨著SoC基帶芯片設計規模高度集成化,驗證周期將不斷增加,占整個研發階段的70%[1]。為了使基帶芯片驗證更具高效性,采用了當前主流的UVM驗證方法學。UVM驗證方法學[2]是由Accellera在2011年正式推出的,創建的驗證平臺不僅提供很多可用接口,而且多樣化的Cadence VIP還為UVM環境搭建提供了必要的組件。因此可以實現高覆蓋率的功能驗證,使仿真驗證時間大幅減小。

基帶射頻接口電路,是一種將基帶芯片和射頻芯片連接起來的數字串行接口。這種數字串行接口不僅節省硬件資源,而且可以通過載波聚合的方式使基帶達到較高的上下行空口峰值傳輸速率。由于復雜的私有化協議接口,必須搭建一種合適的驗證平臺,快速全面地驗證射頻接口電路的功能。本文將使用UVM驗證方法學對基帶射頻接口電路模塊進行驗證,驗證方式將全面覆蓋射頻收發通路的所有功能點。

1UVM驗證平臺

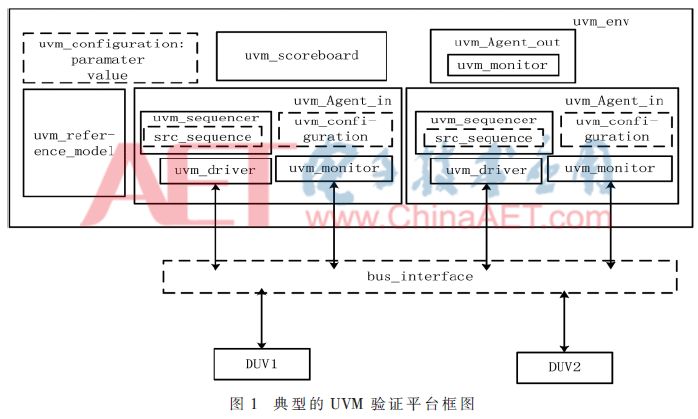

基于UVM特性的驗證設計(Design Under Verification),以System Verilog[3]硬件驗證語言為基礎,通過UVM庫[4]調用各類驗證組件,使驗證工作分工明確。這個UVM庫主要包含以下幾部分:第一,層次化的驗證結構。代理器(Agent)主要集合驅動器等模塊;驅動器(Driver)負責將生成的激勵按照規則加入到DUT的管腳或者內部;監測器(Monitor)檢測DUV 的內部信號以及輸出,實現多種監視操作;計分板(Scoreboard)對DUV值和Model預期的值作比較;參考模型(Reference model)使用SystemVerilog建立的和DUT相關的模型,輸出期望值。第二,UVM序列器(Sequencer)[5]提供仲裁序列(Sequence)模塊,使驅動器得到transaction類型數據包。第三,提供知識產權核(VIP),保證UVM環境中的各個組件快速集成。

典型的UVM驗證平臺如圖1所示。在驗證環境中,uvm_env包含了全部的驗證組件,兩個驗證設計通過總線接口跟平臺相連。驗證平臺按照自上而下的結構規范,從env頂層例化了五個模塊,兩個輸入代理器模塊,一個輸出代理器模塊,一個參考模型模塊和一個計分板模塊。輸入代理器模塊先對驗證環境進行配置,然后通過序列器模塊將激勵源傳送至驅動器模塊,驅動器模塊將數據通過interface傳送至從端接收者,而監測器可以采集驅動器給驗證設計的數據信號。輸出代理監測器模塊實時采樣驗證設計的輸出信號,將采集到的結果放在計分板模塊,并跟參考模型模塊的輸出信息進行比對,減小驗證的錯誤率,降低驗證風險。

2基帶射頻接口電路模塊

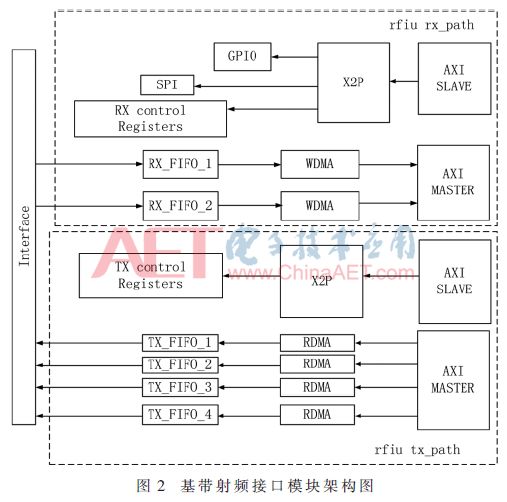

基帶射頻接口模塊包含射頻接口的接收通路模塊和發送通路模塊。基帶射頻接口模塊架構圖如圖2所示。此射頻接口模塊采用AXI標準總線協議,通過X2P轉接橋將從機地址、數據信號傳輸至配置模塊。其中接收通路的定時使能配置通過GPIO輸出,SPI通過配置讀寫寄存器控制外部射頻芯片,接收通路狀態是由接收控制寄存器模塊配置,在可配置的TBU時間點上打開和關閉射頻接收。基帶射頻接口接收的數據流通過兩個FIFO進行緩存,再使用兩組DMA將數據流通過AXI主機搬到基帶芯片中的存儲器。發送通路過程跟接收通路過程互逆,發送狀態通過發送控制寄存器進行配置,在可配置的TBU時間點上打開和關閉射頻發送,基帶芯片主機存儲器的數據流通過AXI總線并使用4組DMA緩存至4個FIFO中,最終發送到射頻芯片。在射頻接口收發過程中,DMA搬數任務完成后發出中斷,中斷傳入ARM處理器,使ARM處理器循環響應,配置多次任務。如果要對FIFO的數據重新緩存,就必須清空FIFO,在可配置的TBU時間點上對寄存器復位,將輸出的數據從現在的采樣點寫到FIFO的起始地址上。

基帶射頻接口采用多模式多帶寬的數據接口支持相應的接口速率,其中CMOS TDD(互補金屬氧化物半導體時分雙工)模式使用兩組12 bit數據線,數據傳輸采用半雙工方式,一個時鐘周期可以發送雙天線符號數據。在CMOS FDD(互補金屬氧化物半導體頻分雙工)模式下,數據傳輸速率是CMOS TDD模式數據吞吐率的2倍。而LVDS(低電壓差分信號)模式數據傳輸速率是CMOS TDD模式數據吞吐率的4倍。

1搭建基于UVM的基帶射頻接口電路驗證平臺

3.1 基帶射頻接口電路驗證流程

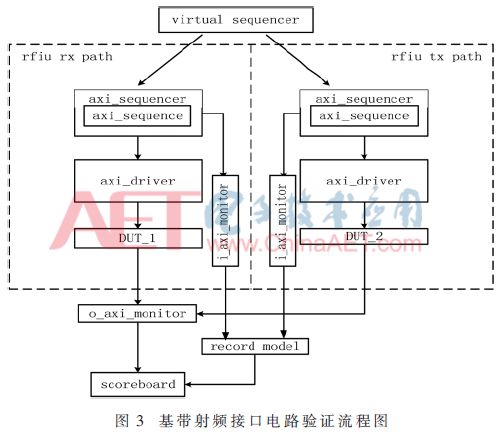

基帶射頻接口采用AXI總線機制分別對基帶射頻的接收通路模塊和發送通路模塊進行驗證,驗證流程如圖3所示。在驗證環境中將軟件接口數據包放置于virtual sequener,通過AXI接口傳送給axi _sequencer,驅動器會得到axi_sequence產生的激勵信號,這些激勵信號分別作用于接收通路的驗證設計和發送通路的驗證設計。同時例化的兩個axi_monitor不僅監視驅動器給射頻接收和發送驗證設計的數據流,而且可以監測record model,這個record model模型通過MATLAB實現跟射頻接口同樣的數據傳輸功能,并把數據信息放入計分板。另一個axi_monitor監測射頻接收和發送通路數據信息傳送至計分板的情況,一旦record model和監控產生的數據信息都傳輸到計分板,計分板將會比對兩者數據,從而判斷仿真是否異常。

3.2 基于UVM的基帶射頻接口電路驗證平臺

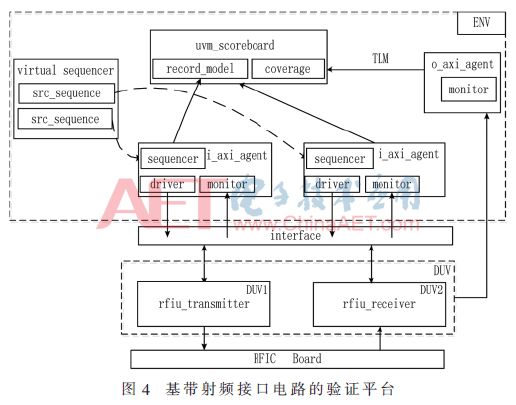

基帶射頻接口電路的驗證平臺如圖4所示。這個待測的驗證設計主要是發送模塊和接收模塊,通過接口將驗證對象與驗證向量連接起來,而驗證向量是為了實現跟待測對象相同的功能。其中驗證環境中的Agent是由VIP提供,剩余組件需自行設計。驗證環境通過頂層env例化兩個i_axi_agent,這兩個i_axi_agent包含其他驗證組件,并將內部的sequencer、driver以及monitor通過build_phase進行創建,使得各個驗證組件能夠緊密連接起來。這兩種i_axi_agent組件包分別作用于射頻接口的發送模塊和接收模塊,目的是為了使配置的active和passive模式能夠對interface上的數據信息進行驅動和監測。o_axi_agnet例化模塊中的monitor可以監視到測試對象發出的激勵數據流,通過TLM接口機制傳送到uvm_scoreboard。與此同時,由Matlab封裝的record_model模型,通過passive模式占用的moitor去監測收發模型數據流,監測抽取的模型數據流要與DUV產生的激勵數據信息進行對比。最終對比的數據流信息通過uvm_scoreboard計分板得出結論,以此判斷基帶射頻接口在收發過程中的數據信息是否完備,統計覆蓋率的要求是否達標。

基帶射頻接口內部的各個寄存器模塊是通過APB總線傳輸地址和數據,而主機轉接橋X2P作為通用IP給寄存器分配可用的地址空間。這些寄存器模型可以在內部通過多次例化,主要為射頻的收發通路提供使能信息。而DMA模塊是為了讓射頻收發模塊的激勵信息搬至正確的memory中,一旦搬完有限幀數據流,就會產生中斷信息,中斷信息會進入ARM處理器,內核發出指令阻止射頻收發。SPI模塊的引入能夠使射頻收發正常讀寫FIFO,同時為外部的射頻子板提供模式切換功能。但是基帶射頻接口內部的模式切換卻要采用mode寄存器模塊。而這些寄存器模塊都是為了給射頻收發通路提供隨機約束,得到滿足要求的激勵。

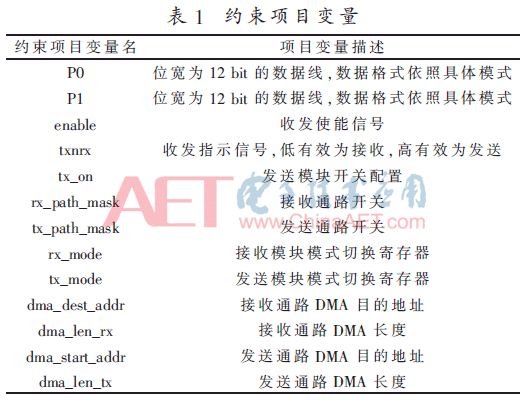

射頻收發通路的隨機約束信息需要通過ARM處理器的軟件環境進行配置,將約束項目存放在transation數據包中,使數據激勵能夠成為驅動射頻收發通路的條件,便于射頻收發模塊正常工作。同時這些約束項目申明了約束變量,變量列表如表1所示。

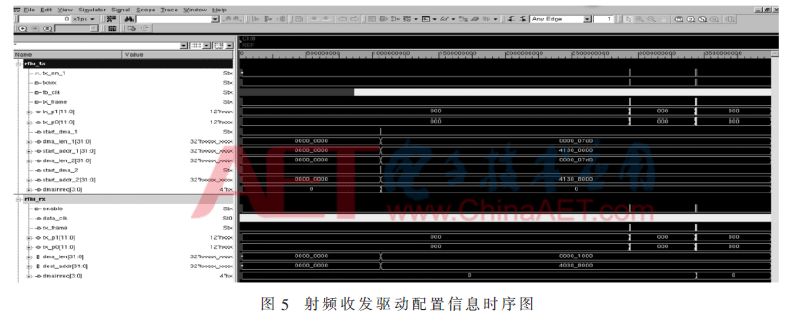

axi_sequencer將激勵源傳輸給驅動器axi_driver,axi_driver需要進行軟件配置才能夠驅動待測模塊。生成射頻收發驅動配置信息的時序圖如圖5所示。軟件配置環境如下:(1)對射頻通路進行初始化,將接收和發送通路都打開,rx_path_mask設置為3 bit,tx_path_mask設置為15 bit。在此還應進行模式切換,分別對rx_mode和tx_mode進行軟件配置選擇接口是工作在CMOS TDD模式、CMOS FDD模式還是LVDS模式下。(2)時鐘頻率配置為了控制外面LPCU模塊來滿足符合要求的相應帶寬的接口頻率。(3)配置接收和發送通路使能信息,enable提供接收通路數據源的起始信息,tx_on提供發送通路數據源的位置信息,txnrx則為RFIC仿真模型提供發送通路使能信號。(4)輸入DMA地址和DMA長度,使基帶芯片的memory能夠發送或接收數據,一旦數據流信息獲取完畢發出中斷dmareq,通知微處理器(arm)等待下次幀數據處理,只有當使能信息enable、tx_on、txnrx變成低電平,數據傳輸才能結束。(5)配置SPI讀寫寄存器,控制外部射頻子板的模式切換,跟基帶射頻接口模式保持一致。

record model作為MATLAB封裝下的模型,這個模型包含了收發數據源模塊、數據格式轉換模塊、定時寄存器模塊、時鐘源模塊以及收發數據寄存器模塊,收發數據寄存器模塊的數據流會通過scoreboard調用的寫函數存入FIFO中,然后調用比較函數將存入FIFO的數據流與DUV中的數據流進行比對,若比對一致,則驗證通過;否則,驗證失敗。之所以采用這樣的比較方式,是因為在復雜的數據比對中更加提高驗證的準確性,并使參考模型合理化分析射頻接口電路功能的完備性與可靠性。

3.3 驗證結果

本次驗證主要以RFIU TDD 20 M測試例為例,對射頻收發的功能點進行測試,對各個功能點對應的功能覆蓋率進行統計,得到射頻收發模塊功能覆蓋率為100%,并分別對射頻收發通路的RTL進行代碼覆蓋率統計,得到代碼覆蓋率為100%。通過UVM驗證,對比計分板上的數據和record_model參考模型的數據,發揮monitor自動監測的作用,監測到數據比對的一致性為100%。其余幾種測試例的功能覆蓋率能達到100%,并在計分板上得出的數據比對度為100%,從而可以說明射頻接口收發模塊的功能需求都已達到。

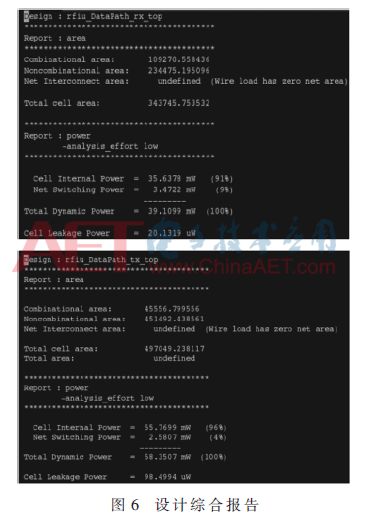

根據Synopsys的Design Compile工具對射頻接口電路的RTL代碼進行綜合,得到射頻接收通路的約束面積為0.3 mm2,功耗為39 mW;射頻接口電路發送通路的約束面積為0.5 mm2,功耗為58 mW。設計綜合報告如圖6所示。

4結束語

UVM作為數字IC驗證最前沿的方法學,盡管前端仿真搭建平臺的周期較長,但是執行效率很高,明顯縮短整個研發的驗證時間。本文利用AXI總線驗證組件搭建基于UVM的基帶射頻接口電路驗證平臺,實現了射頻接口收發模塊功能,在一定范圍內,控制了約束面積和功耗,有利于整個基帶芯片順利量產。同時將這種驗證架構用在基帶芯片其他模塊上,能夠提高驗證效率,并使基帶射頻接口電路的UVM驗證平臺發揮著重要的指導作用。在數字接口設計中具有重要的應用價值。

-

電路

+關注

關注

172文章

5852瀏覽量

171941 -

射頻

+關注

關注

104文章

5551瀏覽量

167579 -

UVM

+關注

關注

0文章

181瀏覽量

19144

原文標題:【學術論文】基于UVM的基帶射頻接口電路的驗證

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IC驗證"為什么要學習UVM呢"

IC驗證"UVM驗證平臺"組成(三)

IC驗證"一個簡單的UVM驗證平臺"是如何搭建的(六)

IC驗證"UVM驗證平臺加入factory機制"(六)

IC驗證“UVM驗證平臺加入objection機制和virtual interface機制“(七)

數字IC驗證之“什么是UVM”“UVM的特點”“UVM提供哪些資源”(2)連載中...

什么是uvm?uvm的特點有哪些呢

UVM驗證平臺執行硬件加速

基于DPI-C接口的UVM驗證平臺設計與實現介紹

基于UVM的基帶射頻接口電路的驗證

基于UVM的基帶射頻接口電路的驗證

評論