在Coarse Placement和Legalization之間,其實還有很重要的一個步驟, 就是對Scan Chain(掃描鏈)的處理。英文名Scan Reorder,直譯為掃描鏈重組。

那講Scan Reorder之前,有必要對Scan Chain的基本知識做一定普及。Scan chain其實是可測試性設(shè)計(DFT)中的內(nèi)容。DFT,Design for test,其實是探測錯誤序列的一種設(shè)計方法學,由于芯片內(nèi)部是一個黑盒子,在外部難以控制。測試人員通過DFT技術(shù),可以從外部控制和觀測電路內(nèi)部觸發(fā)器的信號值。DFT通常需要單獨的一個部門來完成,很復雜,有專門的書籍可以參考。基本概念可以參考:

【時序分析基本概念介紹——花一樣的“模式”】

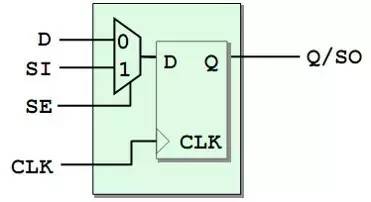

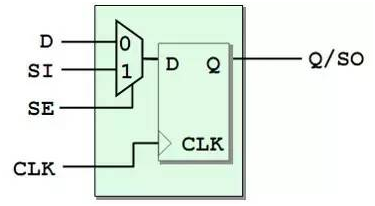

而在后端PR中,我們更關(guān)注的是DFT中的Scan Chain,有了它,我們的芯片就更加具有測試性。Scan Chain將芯片中的所應(yīng)用的普通寄存器替換成帶有掃描功能的掃描寄存器,首尾相連成串,從而可以實現(xiàn)附加的測試功能。那掃描寄存器特殊在什么地方呢?我們從它的結(jié)構(gòu)圖來看一下:

從上圖中可以看出,它比普通存儲器多了SI,SE,SO這3個端口。

1. 其中SI,SO也就是scan_in與scan_out端,定義了一條scan chain的input和output端。通常情況下,每一個input會驅(qū)動一條scan chain,一個ouput也是用來觀察一條scan chain的。

2. SE是scan enable信號,它控制著scan cell的工作模式。從圖中可以看出,SE,SI,D端通過一個Mux實現(xiàn)工作模式的切換。當SE輸入為0時,scan cell工作在普通模式下,相當于是普通的flop;當SE輸入為1時,scan cell就進入scan模式,相當于一個移位寄存器。

scan cell通常定義在lib庫中直接導入,可以通過get_cells_of_scan_chain來做一些檢查。

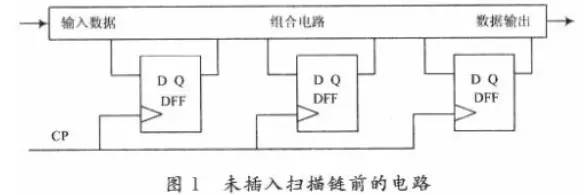

用圖片說明可能會更加形象,對整個邏輯電路來說,未插入scan chain時,電路圖如下:

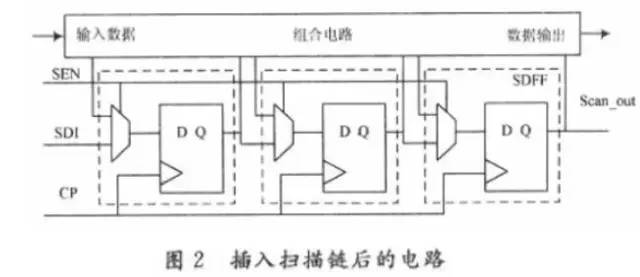

插入scan chain以后,軟件會自動地用scan flip flop(SFF)替換掉普通的flip flop,并且連接SFF到scan chain上,這樣就實現(xiàn)了移位掃描的功能,如下圖所示:

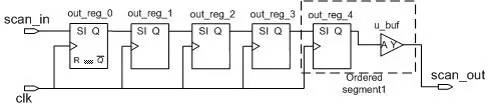

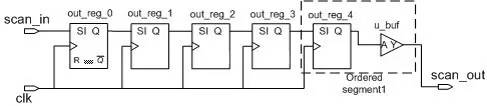

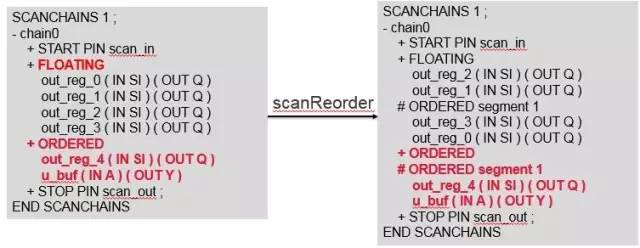

而后端對于掃描鏈的定義,通常使用DEF文件來定義,我們一般稱它為scan def,配合下圖,我們寫出scan DEF語句來說明:

SCANCHAINS 1 ; scan chain數(shù)量

- chain0 scan chain名字+ START PIN scan_in scan chain起點+ FLOATING 代表著單獨的寄存器單元,上圖中out_reg_0,_1,_2,_3都是floating單元out_reg_0 ( IN SI ) ( OUT Q ) out_reg_1 ( IN SI ) ( OUT Q )

out_reg_2 ( IN SI ) ( OUT Q )out_reg_3 ( IN SI ) ( OUT Q )

+ ORDERED 需要放在一起的單元,上圖中out_reg_4與u_buf就是ORDERED單元,用方框圈出out_reg_4 ( IN SI ) ( OUT Q )u_buf ( IN A ) ( OUT Y )+ STOP PIN scan_out ; scan chain終點END SCANCHAINS

概念都了解完以后,那我們后端到底需要對scan chain做些什么呢?

其實,在做完coarse placement后,Scan Cell大部分是按照連接的順序隨機的亂放的。這樣其實會極大地占用繞線資源。因此,在后續(xù)步驟開始之前,我們希望對掃描鏈的連線進行處理,在不影響邏輯功能的前提下,重新進行連接,從而減少走線長度。那這個重組的過程,我們就稱之為掃描鏈重組(Scan Reorder)。整個過程,可以用下面兩張圖來形象地說明:

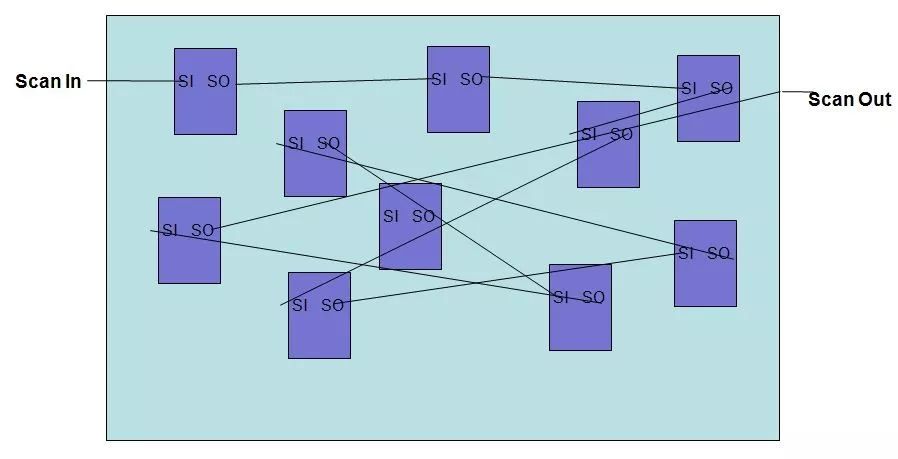

Scan Reorder之前:可以看到,每個scan cell的連接得亂七八糟,專業(yè)術(shù)語叫做detour

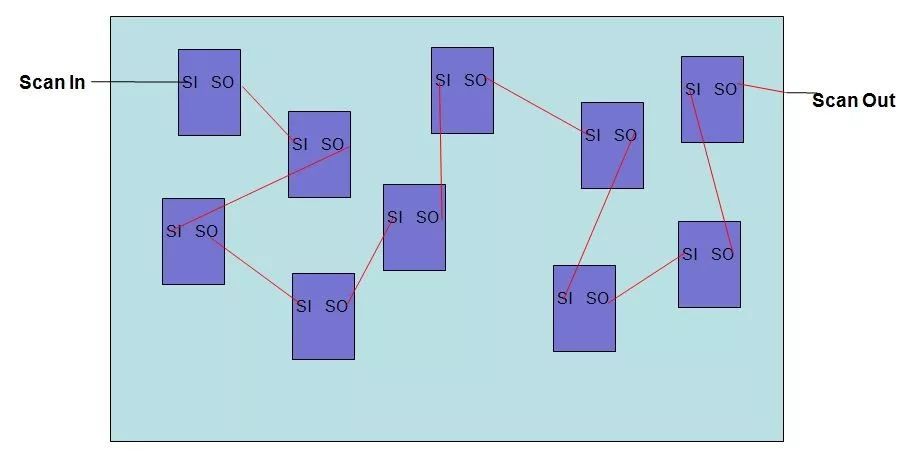

Scan Reorder之后:仔細看,走線少了很多,也規(guī)整了不少吧!那這就是我們希望得到的結(jié)果~~(當然前提是不能影響邏輯功能)

如果用前文DEF的例子解釋:

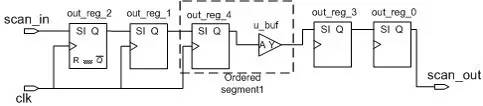

經(jīng)過Scan Reorder之后,變成如下的電路連接:

可以看到,被方框圈住的out_reg_4和u_buf就類似一個整體一樣,位置重新進行了排列。

那對應(yīng)的Scan DEF信息變化就是:

左邊的DEF格式前文已經(jīng)說明,那右邊reorder之后的大家能看懂嘛?

右邊就多了一個#符號,這里可以理解為標志位,與著下面的#ORDERED segment 1相關(guān)聯(lián),就是為了說明它在FLOATING信息里的排列位置。

最后,我們可以使用report_scan_chains來報出scan chain的組成,使用check_scan_chain來檢查其合理性

Checking Scan Chain scan_segment_88

STOP: u__noram/u_etm/u_fifo/ts_0_lockLD_865264

....

thru: u_noram/uersistent_cell_0_buf_intsi54506_i/Z

STATUS: VALIDATED, Sequential Length = 524, Instance Count = 524, Partition = partition_1

-

DFT

+關(guān)注

關(guān)注

2文章

224瀏覽量

22680 -

時序

+關(guān)注

關(guān)注

5文章

385瀏覽量

37277

原文標題:剪斷了,理就不會亂——Scan Reorder

文章出處:【微信號:IC_Physical_Design,微信公眾號:數(shù)字后端IC芯片設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

時序分析中的一些基本概念

時序分析中的一些基本概念

時序分析和時序約束的基本概念詳細說明

時序分析基本概念介紹——花一樣的“模式”

時序分析基本概念介紹——花一樣的“模式”

評論