本設計實例探討了分辨率更高、位數更少的三進制DAC。盡管精確的三進制DAC實現可能要比普通的二進制DAC更困難 (特別在分辨率提高時困難更大),但五個三態位 (35=243) 本質上就可與常規八個兩態位 (28=256) 性能相近。與所有簡單的DAC設計一樣,三態 DAC電源噪聲也會傳遞到輸出端。

當EDN忠實讀者和設計實例欄目的投稿人Jim Brannan提出要寫一篇關于三進制DAC設計的文章時,我感到非常高興。像Charlieplexing(一種采用較少管腳驅動多路復用顯示的技術)一樣,他的想法是利用三態輸出以便從一個管腳上獲取更多信息,而不僅僅是“0”和“1”。例如,對于一個三態的四位DAC,理論上能夠產生81(34)種輸出值,而不是通常(兩態)的16(24)種。而三態的五位DAC(35=243)本質上與常規的兩態八位(28=256)性能相近,盡管精確的三進制DAC實現可能要比普通的二進制DAC更困難,特別是分辨率的提高帶來更大的困難。

一如既往,我先Google是否有類似的創意想法。果然,找到了兩頁描述類似設計的文獻。Jim也看了,他覺得沒啥可補充的。所以,設計創意的文章也就擱淺了。但我覺得這個創意無論如何都值得說一下。另外,Jim的方法確有獨到之處。

在開始之前,或許該花點時間想一下你自己會如何構思一個三態DAC。在下面的想法占領你的大腦前,也許你會另辟蹊徑,想出一種新方法。

*************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************

好吧,這是我自己的實現思路:

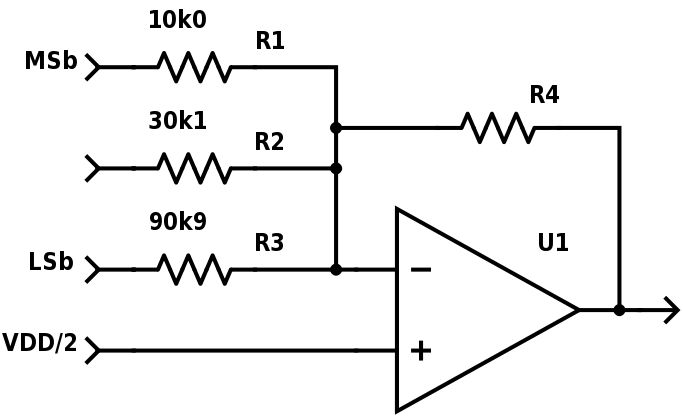

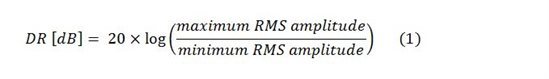

圖1:采用帶中間電源參考的加法放大器實現三進制 DAC。

實際上,我最初的想法是將放大器的(+)輸入設置為-VDD,但后來我意識到浮動輸出會被拉向負電源,可能會鉗位在-0.7V,且通常無法工作。VDD/2參考表示0、1、2狀態,對應于0、Z、1輸出值(“Z”表示高阻抗和/或輸入模式)。

另一個硬件問題是,當輸入處于中間電壓軌時,某些微控制器可能會吸收過多的供電電流,因此要確認這不會出問題。要禁用數字輸入模式,或使用可設置為模擬輸入的引腳。

驅動三進制DAC需要一個查找表,或從二進制到三進制的轉換程序。在大多數情況下,除非在一個寫周期內設置好引腳模式和值,否則DAC輸出將在其設置發生改變時產生毛刺現象。

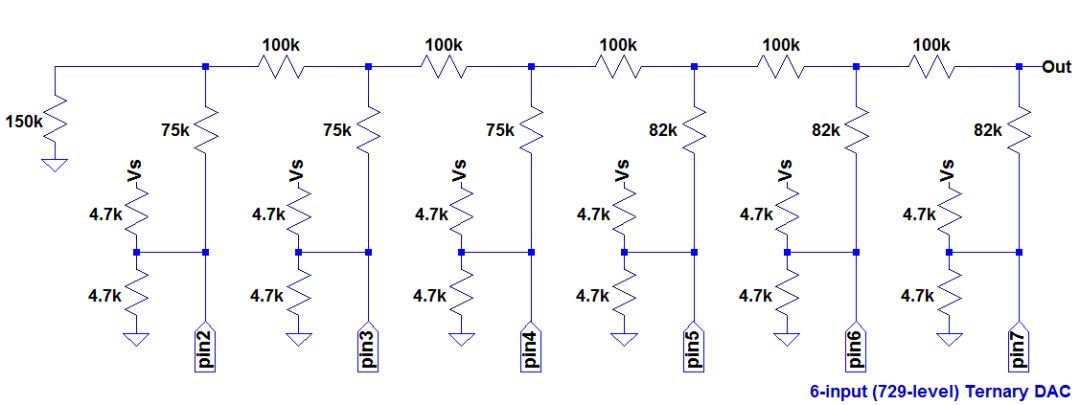

被Jim放棄的設計想法使用無源“R-2R”類型的DAC,他寫了用于搜索許多阻值組合的軟件。意識到無法創建一款完美的線性DAC,他的方案是使用查找表,DAC的表現有些不平衡也就只好接受了。

在Josh Bowman的博客中,他描述了自己對三進制DAC的構想。它采用一種類R-2R結構,用較低值的電阻將電源分壓以產生中間電平的“Z”值。

圖2: Josh Bowman的無源三進制DAC。

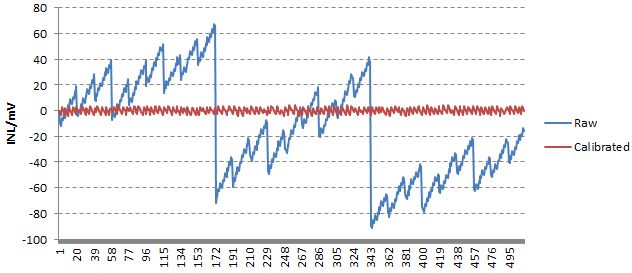

正如你在下面看到的,設計中有冗余的值,可用來進行校準。

圖3:原始和校準過的積分非線性(INL)性能。

在Arduino論壇上也有幾個關于三進制DAC設計的討論,感興趣可以去看看。

如果你對三進制DAC設計實現有自己的想法,請在寫下你的經驗。我們很樂意傾聽你的分享。請記住,與所有這些簡單的DAC設計一樣,三態DAC電源噪聲也會傳遞到輸出端。

《電子技術設計》2018年4月刊版權所有,轉載請注明來源及鏈接。

-

電源

+關注

關注

184文章

17188瀏覽量

247745 -

dac

+關注

關注

43文章

2225瀏覽量

190431

原文標題:三進制DAC:分辨率更高,位數更少

文章出處:【微信號:edn-china,微信公眾號:EDN電子技術設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

EVAL_PASCO2_SENSOR為什么無法從較低的分辨率高速獲得更高的分辨率?

ADC的噪聲、ENOB及有效分辨率

請問24位的分辨率是否是所有ADC的極限?

RF成像分辨率怎么提高

如何實現更高的分辨率或更窄的RBW測量?

如何使用gstreamer獲得更高的分辨率?

峰峰值分辨率與有效分辨率的區別

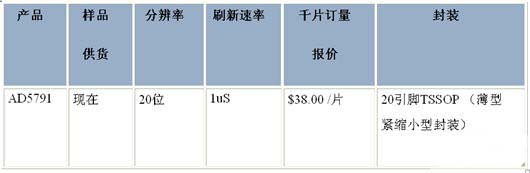

ADI推出分辨率+精度1ppm DAC

峰峰值分辨率與有效分辨率

分辨率的峰值分辨率和有效分辨率概念

ADC 的分辨率位數和有效分辨率哪個更重要

探討分辨率更高、位數更少的三進制DAC

探討分辨率更高、位數更少的三進制DAC

評論