隨機變化需要新方法、新工具,以及不同公司之間的合作。

極紫外(EUV)光刻技術正在接近生產,但是隨機性變化——又稱為隨機效應正在重新浮出水面,并為這項期待已久的技術帶來了更多的挑戰。

GlobalFoundries、英特爾、三星和臺積電希望將EUV光刻技術加入到7nm和5nm生產中。但就像以前一樣,EUV由幾部分組件組成,在芯片制造商能夠引入之前,它們必須整合在一起。包括光刻機、光源、光刻膠和掩膜。最近,行業已經開始發布關于量子隨機效應的警報,這種現象會引起光刻圖案隨機變化。

有些組件已經準備就緒,而有些則發展緩慢。事實上,EUV團隊首次將光刻膠及其相關問題列為EUV的最大挑戰,超過了電源。經過多年的推遲,EUV光源功率終于滿足了大批量生產(HVM)的要求。

光刻膠是用來制作圖案的光敏聚合物,它是造成隨機性效應的罪魁禍首之一。根據定義,隨機效應描述了具有光量子隨機變化的事件。它們是不可預測的,沒有穩定的模式。

在EUV的情況下,光子擊中光刻膠并引起光化學反應。但是對于EUV光刻膠而言,由于量子非定域效應,每個或多個反應期間可能出現新的不同的反應。因此EUV容易發生涉及隨機效應。一般來說,該行業將隨機性主要歸咎于光刻膠,但EUV的光掩膜和其他部分(EUV光子平均自由程較大)也可能會出現隨機變量。

隨機效應并不新鮮。事實上,這一現象多年來一直困擾著EUV團隊。眾所周知,隨機效應會導致光刻圖案的變化。行業一直在努力解決這個問題,但人們要么低估了問題,要么沒能及時解決問題,要么兩者兼而有之。

新情況是,行業終于迎來了另一個問題。一顆先進的邏輯芯片集成了十億個甚至更多的微小通孔。 如果EUV光刻過程中出現問題,芯片可能會遭受由于隨機效應引發的失效或缺陷(通孔缺失contact missing)。換言之,一顆芯片可能會因為一個觸點通孔的缺陷而失效。

這可能是一廂情愿的想法,但芯片制造商相信他們可以躲避7nm工藝節點潛在的由隨機性引發的缺陷。事實上,EUV可能出現在7nm工藝節點。但在5nm甚至是7nm工藝節點的情況下,芯片制造商可能無法避免這些和其他問題,除非行業出現一些新的突破。GlobalFoundries高級研究員兼高級技術研究總監Harry Levinson表示:“公平地講,我們的行業非常樂觀地看待我們向EUV光刻前進的方向。我們正準備將第一代引入到大批量生產中,展望第二代EUV光刻技術,抵抗隨機效應絕對是最重要的問題之一。”

無論節點如何,EUV隨機效應都為芯片制造商、晶圓廠工具供應商和IC設計團體帶來了麻煩。西門子公司DFM項目總監David Abercrombie表示:“從設計的角度來看,隨機效應確實是隨機的,因為你無法預測變化的位置和數量。因此,沒有系統的方法可以說一個特定的布局特征應該在這個區域還是在另一個區域中進行修改。換言之,除了避免的所有敏感特性的出現,將其轉化成傳統設計規則約束以外,完全沒有辦法在設計過程中補償隨機效應影響。”

作為回應,該行業正在采取措施解決一些問題。其中包括:

? 供應商正在改進EUV光刻膠。

? Applied Materials和ASML正在開發一種新的電子束測量工具,承諾可以檢測出隨機性缺陷。此外,創業公司Fractilia已經設計了一種方法來輔助測量。

? 然后,通過這些新的測量數據,芯片制造商請求有競爭力的晶圓廠工具供應商進行合作,并一起對信息進行整合。

-

光刻膠

+關注

關注

10文章

301瀏覽量

29982

發布評論請先 登錄

相關推薦

Futurrex高端光刻膠

光刻膠殘留要怎么解決?

Microchem SU-8光刻膠 2000系列

光刻膠在集成電路制造中的應用

光刻膠有什么分類?生產流程是什么?

光刻機工藝的原理及設備

光刻膠和光刻機的關系

光刻膠的原理和正負光刻膠的主要組分是什么

淺談EUV光刻中的光刻膠和掩模等材料挑戰

EUV光刻膠開發面臨哪些挑戰?

光刻膠黏度如何測量?光刻膠需要稀釋嗎?

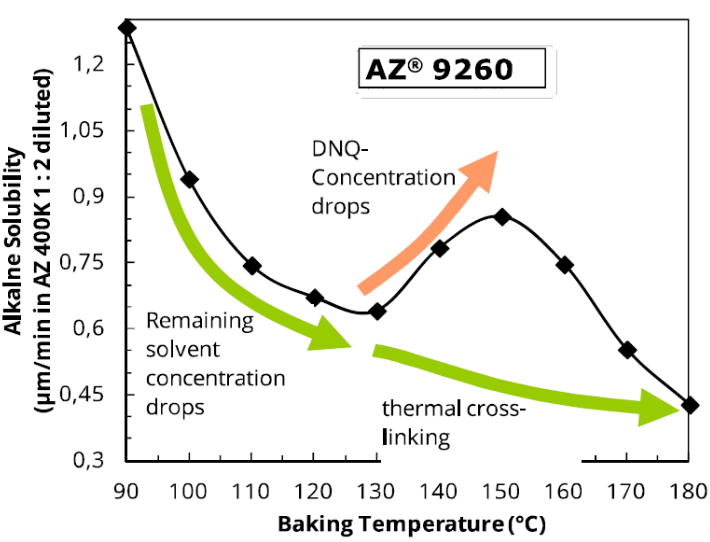

光刻膠的硬烘烤技術

極紫外(EUV)光刻新挑戰,除了光刻膠還有啥?

極紫外(EUV)光刻新挑戰,除了光刻膠還有啥?

評論