地線(xiàn)干擾的共阻干擾

1、本文出發(fā)點(diǎn)

本文基于噪聲產(chǎn)生的原理, 進(jìn)一步論述簡(jiǎn)單而實(shí)用的應(yīng)用:數(shù)模混合音頻系統(tǒng)中最簡(jiǎn)單的規(guī)避地噪聲手段—— “單點(diǎn)接地”。讓讀者明白“為什么要單點(diǎn)接地” 。希望讀者著重認(rèn)清單點(diǎn)接地的原理,從而化用、推廣到其他地方,而不是簡(jiǎn)單地記住本文中所提到的例子。

2、本文適用的讀者

“單點(diǎn)接地”是否有似曾相識(shí)的感覺(jué)?

假如你現(xiàn)在的情況是“聽(tīng)說(shuō)過(guò)單點(diǎn)接地, 但是不知道具體應(yīng)該如何單點(diǎn)接地;或者大致知道如何單點(diǎn)接地,但是不能清楚地理解單點(diǎn)接地的原理” 。那么很幸運(yùn),本文為你而寫(xiě)!

3、共阻干擾存在的幾種形式

本文重點(diǎn)是:講述了共阻干擾的幾種常見(jiàn)形式,會(huì)產(chǎn)生幾種經(jīng)典后果:干擾會(huì)被放大后輸出、干擾被衰減后輸出、干擾被原原本本地輸出等。

(地線(xiàn))共阻干擾存在的根本原因是: (地)導(dǎo)線(xiàn)存在阻抗,且干擾與被干擾信號(hào)有共同的信號(hào)回路。

3.1、共阻干擾的幾種形式

3.1.1、完全沒(méi)有共阻噪聲

理想狀態(tài),導(dǎo)線(xiàn)無(wú)阻抗、分布參數(shù),不存在噪聲。Av-niose = 0 :

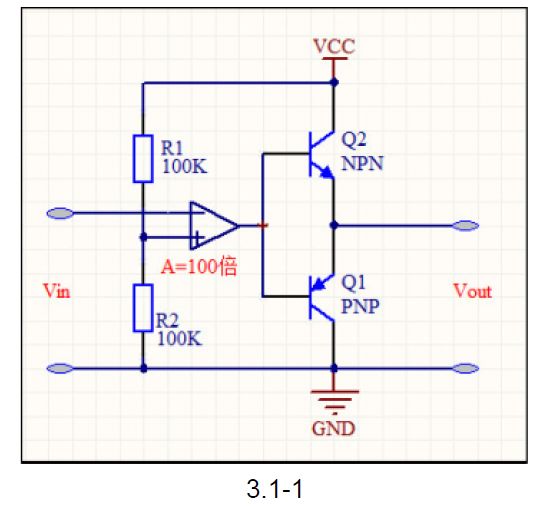

如圖3.1-1,理想狀態(tài)下, Vout = 100*Vin,輸出沒(méi)有噪聲。

3.1.2、共阻噪聲最糟糕的狀態(tài)

最壞的布線(xiàn)情況,噪聲會(huì)被“加倍放大” 。Av-niose >> 1 :

3.1-2

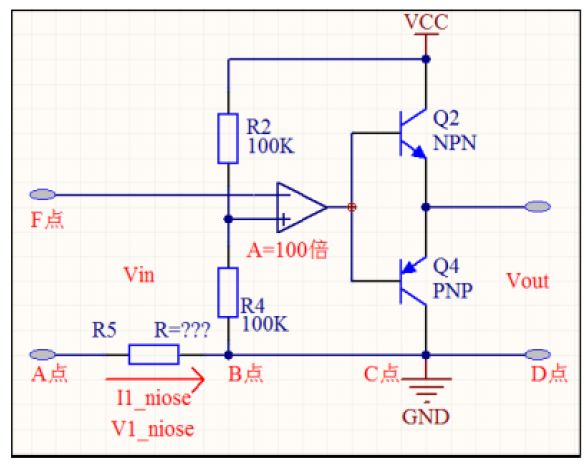

如圖3.1-2,由于AB點(diǎn)在PCB板上是一段銅箔, 不可避免存在阻抗(雖然銅的電阻率極小),假設(shè)其阻抗為R5。模擬輸入信號(hào)的回路經(jīng)過(guò)A——B段,當(dāng)有數(shù)字電流I1_niose 地回路流經(jīng)A——B點(diǎn)時(shí), R5既是模擬信號(hào)的回流地電阻,也是數(shù)字電路信號(hào)的回流地電阻,這個(gè)導(dǎo)線(xiàn)電阻由模擬、數(shù)字“共享” ,故稱(chēng)為共阻。而數(shù)字信號(hào)經(jīng)過(guò)R5會(huì)產(chǎn)生V1_niose,這個(gè)V1_niose電壓將會(huì)疊加在干凈的模擬輸入信號(hào)上,造成輸入信號(hào)的污染(干擾) ,故把這種—— 因?yàn)橛泄餐亓髀窂蕉a(chǎn)生的干擾現(xiàn)象叫“共阻干擾” 。

由于該電路放大的是BF端的電壓。(而不僅僅是AF端,如果不明白這一點(diǎn),必須重新學(xué)習(xí)功放!)所以Vout=(Vin+V1_niose)*100,其中輸出噪聲部分的信號(hào)是V1_niose*100!——可見(jiàn),噪聲被加倍放大了!!!這是共阻噪聲最為嚴(yán)重的一種狀況!

經(jīng)驗(yàn)性現(xiàn)象解釋?zhuān)河腥苏f(shuō):銅的電阻率這么低,即使V1_niose 放大一百倍也聽(tīng)不到,因?yàn)橛?a target="_blank">示波器根本沒(méi)有看到噪聲的存在!而且數(shù)字噪聲一般不在20—— 20KHz人耳可聽(tīng)見(jiàn)范圍!

這個(gè)說(shuō)法好像有道理,但是實(shí)際和理論都是不對(duì)的。原因如下: (1)人耳朵在安靜環(huán)境中, 通過(guò)耳機(jī),人們能清楚地聽(tīng)到毫伏級(jí)(幾毫伏)的音頻噪聲信號(hào),而普通示波器一般無(wú)法捕捉到這么微弱的波形。因?yàn)槠胀ǖ臄?shù)字示波器接上探頭后顯示在屏幕上的噪聲電平有20mV 左右,非常昂貴的示波器在拔掉探頭的情況下,顯示在屏幕上的底噪才可能小于1mV。所以人耳朵能聽(tīng)到噪聲但是示波器看不到,這很正常。(2)即使數(shù)字電路本身工作頻率遠(yuǎn)超過(guò)20KHz,但MCU內(nèi)部模塊間的啟動(dòng)關(guān)閉動(dòng)作的頻率有可能落在音頻范圍。而且,即使大于20KHz的數(shù)字信號(hào),經(jīng)過(guò)導(dǎo)線(xiàn)的分布電感與分布電容“濾波”后,形成V1_niose 將落在音頻范圍。這是我們能聽(tīng)到數(shù)字噪聲的原因。

3.1.3、共阻噪聲1:1 放大輸出

干擾不被放大、直接呈現(xiàn)在輸出端。Av-niose = 1:

3.1-3

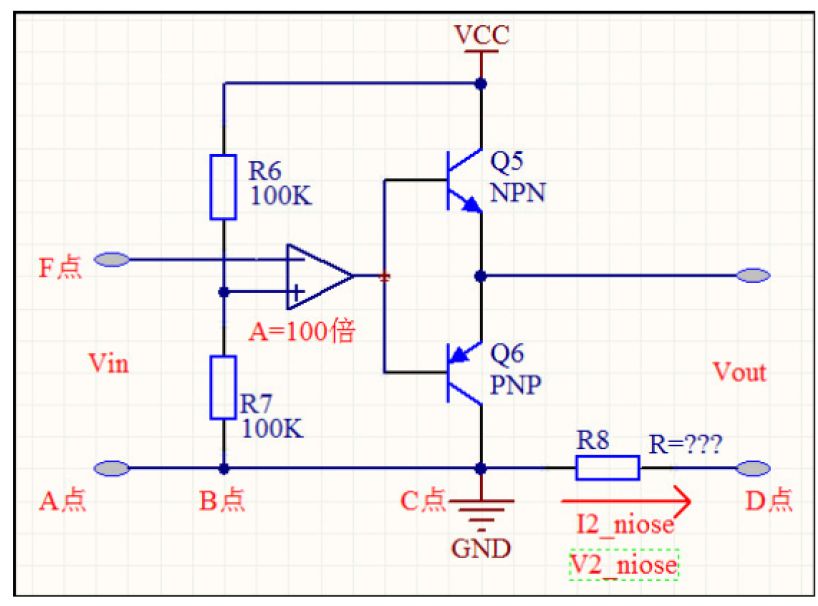

如圖,若數(shù)字噪聲只流過(guò)R8,那么Vout=Vin*100 + V2_niose,存在數(shù)字噪聲,但是噪聲沒(méi)有被放大, 所以一般情況下, 數(shù)字噪聲不明顯, 只是是在安靜的環(huán)境中可能可以聽(tīng)得到。

3.1.4、共阻干擾被衰減后輸出

干擾會(huì)被功放器件抑制, Av-niose << 1 :

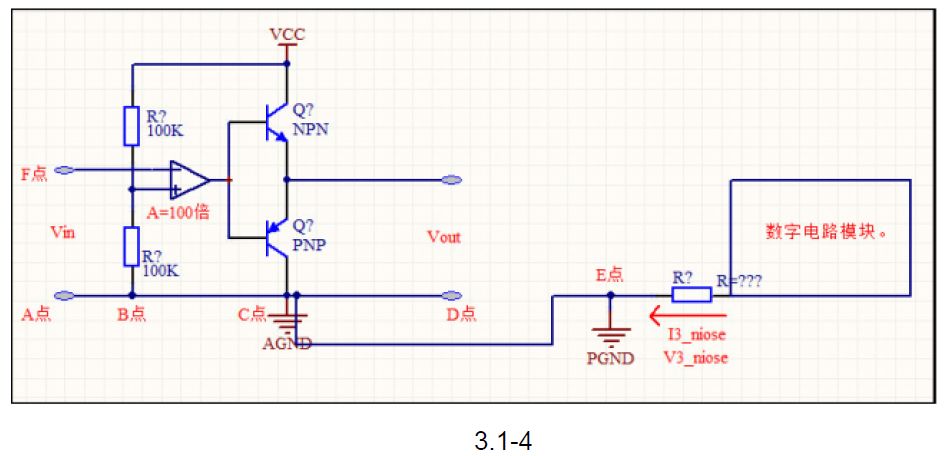

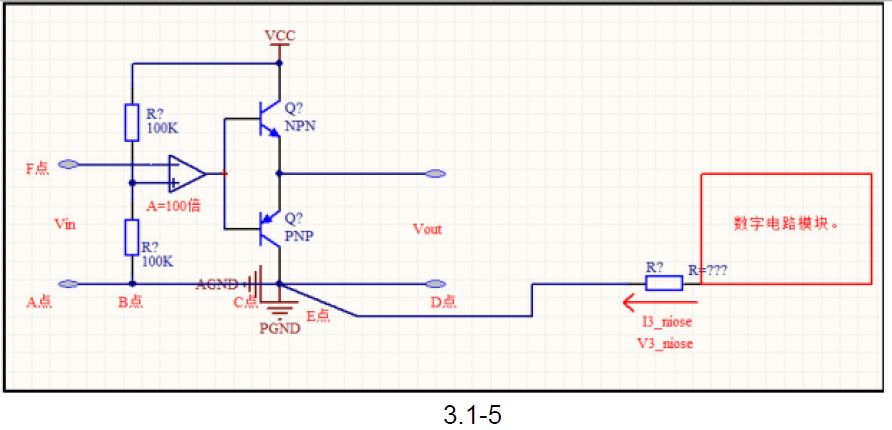

如圖,假如在數(shù)字電路端單點(diǎn)接地。那么,數(shù)字噪聲V3_niose 可以直接回流到電源,并沒(méi)有流經(jīng)功放區(qū)域, (其實(shí)深究起來(lái),還是有非常微小的部分噪聲流經(jīng)EC段PCB,并從其他路徑構(gòu)成回路,但是這個(gè)影響非常小。回路路徑如何形成?根據(jù)“噪聲的起源”章節(jié)中的內(nèi)容,其實(shí)足以領(lǐng)悟出來(lái)。)所以不會(huì)造成地線(xiàn)的共阻干擾噪聲。但是,有兩點(diǎn)值得擔(dān)心的:

(1)電源不是理想的電源,會(huì)存在“內(nèi)阻” ,所以數(shù)字電路會(huì)通過(guò)“干擾公共的電源從而干擾功放” ——幸運(yùn)的是, 這個(gè)干擾非常小, 一般情況下都不會(huì)引起系統(tǒng)出現(xiàn)噪聲,原因是:功放的電源紋波抑制比一般非常高!

(2)C與E之間同樣是銅箔,實(shí)際上也存在內(nèi)阻!這段地線(xiàn)也會(huì)產(chǎn)生共阻干擾。但是,實(shí)際上采用這種布線(xiàn)方式也不會(huì)出現(xiàn)干擾問(wèn)題,原因是:一、其阻抗引起的干擾相當(dāng)于電源抖動(dòng)的干擾, 而功放有一定的電源紋波抑制能力(這個(gè)是地紋波抑制, 實(shí)際測(cè)試過(guò)的一些芯片, 都是電源紋波抑制能力比地紋波抑制能力好,這應(yīng)該與Bypass電路有關(guān),有興趣者可以深究) 。二、這個(gè)干擾一般是聲音較大時(shí)干擾才比較大,但是聲音大后,噪聲會(huì)被音樂(lè)“蓋住” ,所以人感受不到噪聲的存在。

3.1.5、在電路板上不會(huì)存在地噪聲

如圖3.1-5,電池、數(shù)字地、模擬地的單點(diǎn)接地點(diǎn)都接在C、E點(diǎn)的重合處。這樣接地,在電路板上不會(huì)出現(xiàn)噪聲, Av-niose=0 。(但是,電池接上后,同樣會(huì)產(chǎn)生“ 3.1.4”的類(lèi)似情況,因?yàn)槊總€(gè)電源都有內(nèi)阻。這個(gè)讀者自行構(gòu)建模型分析!)

無(wú)論如何, 對(duì)于圖中的電路, 這已經(jīng)是最好的接地方式了! 而且這種接地方式從未出現(xiàn)過(guò)噪聲!

3.2、敏感點(diǎn)與不敏感點(diǎn)

由3.1 的內(nèi)容知道, PCB走線(xiàn)不當(dāng),噪聲會(huì)被“成倍放大” 、或會(huì)被“ 1 倍放大”。產(chǎn)生這種狀況說(shuō)明:對(duì)于音頻功放放大電路, PCB上存在“地噪聲敏感點(diǎn)和不敏感點(diǎn)”(或者說(shuō)是敏感段) 。

3.2.1、地噪聲敏感段PCB

圖3.1-2 的AB段的噪聲會(huì)被成倍放大, 所以AB段是“地噪聲敏感段PCB”,經(jīng)過(guò)敏感段PCB的數(shù)字地噪聲將會(huì)被“加倍放大”后輸出。

之所以會(huì)被加倍放大,是因?yàn)樵肼曅盘?hào)經(jīng)過(guò)功放的前端放大電路的地回流,這段PCB對(duì)應(yīng)于實(shí)際應(yīng)用中的很多功放的“ Bypass電容接地點(diǎn)(如圖3.1-2 中B點(diǎn))與功率地(如圖3.1-2 中C點(diǎn))之間的PCB”。也就是: BC間的PCB連走線(xiàn)極有可能成為地噪聲敏感段PCB。

3.2.2、地噪聲不敏感段PCB

圖3.1-3 的CD段是地不敏感段PCB,因?yàn)榻?jīng)過(guò)這一段PCB的噪聲放大倍數(shù)是1,噪聲不會(huì)被加倍放大。其原因在于地噪聲沒(méi)有經(jīng)過(guò)功放的前級(jí)放大區(qū)域,所以噪聲信號(hào)只會(huì)原原本本地在喇叭端輸出。

4、單點(diǎn)接地

本節(jié)重點(diǎn):第3 節(jié)共阻干擾的各種案例中,存在地噪聲可能會(huì)流經(jīng)“敏感

段PCB”這個(gè)現(xiàn)象。所以為了最大地減小地噪聲,要單點(diǎn)接地,讓噪聲不要經(jīng)過(guò)敏感段PCB。

4.1、單點(diǎn)接地與“敏感信號(hào)段”的聯(lián)系

細(xì)心的讀者已經(jīng)發(fā)現(xiàn), 第三節(jié)已經(jīng)存在單點(diǎn)接地。單點(diǎn)接地不應(yīng)單純理解為:在PCB上有一個(gè)物理的接地點(diǎn);而應(yīng)該理解為:在PCB上有一個(gè)接地點(diǎn),而且不同性質(zhì)的地回流信號(hào)(比如模擬回流和數(shù)字回流) 不會(huì)存在這個(gè)接地點(diǎn)以外的“公共路徑”(公共路徑—— 即地線(xiàn)上數(shù)字與模擬公有的PCB電阻“ R5”,前面已經(jīng)解釋過(guò))。

圖“ 3.1.4 和3.1.5”其實(shí)就是單點(diǎn)接地的情況,所以此處不再贅言。本節(jié)重點(diǎn)寫(xiě):如何去真正理解單點(diǎn)接地。

4.2、如何去理解單點(diǎn)接地

單點(diǎn)接地的思想,在《印刷電路板排版設(shè)計(jì)》有很詳細(xì)的講解。很老的書(shū),工藝可能和現(xiàn)在不同, 但其設(shè)計(jì)思想不變! 而且,作者認(rèn)為這是國(guó)產(chǎn)少見(jiàn)的不是“ Ctrl + C”和“ Ctrl + V”的書(shū)。鄭詩(shī)衛(wèi)寫(xiě)的,感謝鄭老前輩!

4.2.1、理解原理的重要性(經(jīng)驗(yàn)性廢話(huà))

平時(shí)我們經(jīng)常會(huì)聽(tīng)到“單點(diǎn)接地”這個(gè)詞,很多人說(shuō)“去掉數(shù)模混合電路噪聲的終極武器就是單點(diǎn)接地” 。但是某日有個(gè)鞋童淚流滿(mǎn)面的奔過(guò)來(lái)嚎叫:我已經(jīng)單點(diǎn)接地了,可是噪聲尚在· ·····

何故?

額!哥!不是單點(diǎn)接地就可以去掉噪聲,而是要“正確的單點(diǎn)接地”才能夠去掉噪聲。正確的數(shù)字、模擬前端、電池、功率地的單點(diǎn)接地點(diǎn)是:功放的功率地引腳(或者功率地、功放電源的去耦電容引腳。)

例如,我們?cè)谠O(shè)計(jì)一個(gè)實(shí)在的產(chǎn)品時(shí), 存在很多互斥不可兼得的“布線(xiàn)定理”時(shí),我們?nèi)绾稳∩幔?究竟是讓這個(gè)電路符合A 法則、放棄B 法則好呢,還是符合B法則、放棄A 法則好呢? 要做正確做出這種判斷,就要求我們清楚:什么是影響最大的、而什么的影響幾乎可以忽略不計(jì)的。

所以,除了實(shí)踐,還得最終把握其原理。

4.2.2、例說(shuō):了解敏感信號(hào)區(qū)的方法

使用前想評(píng)估某個(gè)特定芯片有哪些特征,需要一定的理論+ 專(zhuān)業(yè)常識(shí),推斷出芯片內(nèi)部的構(gòu)造,從而可以判斷“哪些是信號(hào)敏感點(diǎn),哪些不是敏感點(diǎn)” 。

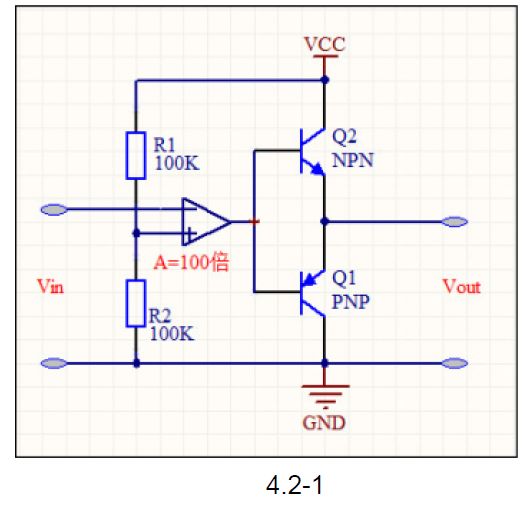

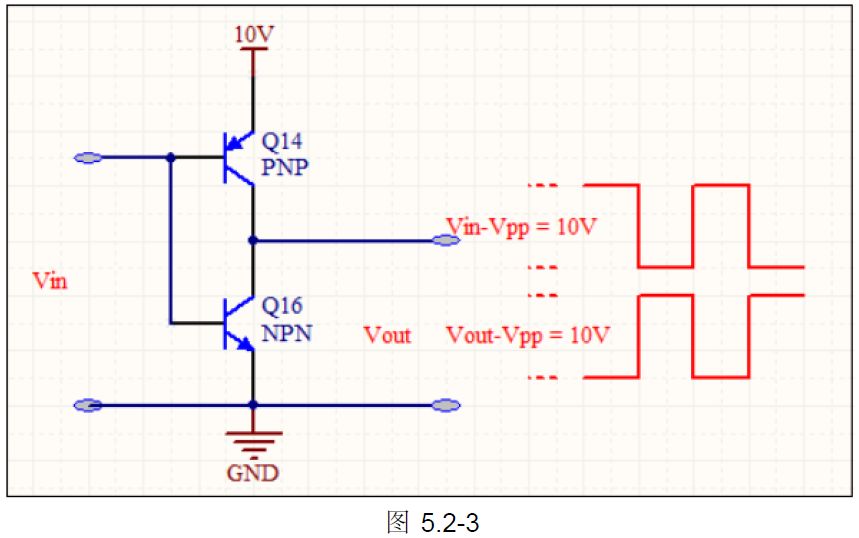

以功放為例,目前絕大多數(shù)AB類(lèi)音頻功放內(nèi)部構(gòu)造如下圖所示。前端為電壓放大,相當(dāng)于運(yùn)放,一般由偏置電路與共射放大電路組成,該部分功能是:對(duì)輸入的信號(hào)(包括噪聲)進(jìn)行電壓放大。而后級(jí)為射極跟隨電路,一般電壓放大倍數(shù)為1(沒(méi)有電壓放大能力) ,只是增強(qiáng)了輸出電流驅(qū)動(dòng)能力。

圖中的運(yùn)放“ +”端,通常相當(dāng)于功放的“ Bypass”引腳;而Q1的接地點(diǎn)的

地相當(dāng)于功放的功率地引腳。Bypass引腳通常接一個(gè)去耦電容到地, 該電容的地到功放的功率地間的PCB走線(xiàn)相當(dāng)于圖3.1-2 中的AC段PCB。假如這段PCB存在噪聲,那么相當(dāng)于噪聲混進(jìn)了功放前級(jí)的運(yùn)放,噪聲將會(huì)被“極大地放大” !

這就是“噪聲混進(jìn)了信號(hào)敏感段PCB”。

所以單點(diǎn)接地的目的是:不讓噪聲地回流經(jīng)過(guò)“敏感信號(hào)區(qū)的地線(xiàn)區(qū)域” 。

5、理論的延伸

本節(jié)重點(diǎn):從單點(diǎn)接地引出單點(diǎn)接電源,從單點(diǎn)接電源的“不夠普遍”這個(gè)現(xiàn)象探討“電源紋波抑制比” 。從原理上論證: 模擬芯片電源紋波抑制比較強(qiáng),而數(shù)字芯片無(wú)電源紋波抑制能力。

5.1、既然有單點(diǎn)接地,那么有沒(méi)有“單點(diǎn)接電源”?

顯然,答案是肯定的。

但奇怪的是:為什么總是聽(tīng)到前輩強(qiáng)調(diào)“單點(diǎn)接地” ,卻很少聽(tīng)到他們強(qiáng)調(diào)“單點(diǎn)接電源”?

日常生活常見(jiàn)的一個(gè)現(xiàn)象是: 當(dāng)一個(gè)事情經(jīng)常出現(xiàn)或者出現(xiàn)的后果十分嚴(yán)重時(shí),經(jīng)歷過(guò)的人們時(shí)常會(huì)把它掛在嘴邊, 沒(méi)經(jīng)歷過(guò)的人也能耳熟能詳。但當(dāng)事情出現(xiàn)的概率很小、或者后果影響很小時(shí),人們時(shí)常會(huì)把它忽略掉。

同樣,“單點(diǎn)接電源”也是如此,電源當(dāng)然會(huì)產(chǎn)生共阻噪聲。但是在音頻功放中,其影響通常非常小(原因是功放電源的紋波抑制比高) ,即在喇叭端一般聽(tīng)不到電源的紋波噪聲;而且在電源端的共阻干擾不會(huì)出現(xiàn)“噪聲被成倍放大”的情況(因?yàn)锽ypass電容接到地,而不是接到電源) 。所以一般情下電源存在共阻干擾,但是在輸出音頻上聽(tīng)不到,所以在音頻領(lǐng)域一般不會(huì)引起很大的重視。(這是對(duì)集成芯片而言, 對(duì)于分立元件搭建的功放電路, 有些構(gòu)造對(duì)電源紋波還是非常敏感的。)

注意:電源處理不好會(huì)加重模塊間的干擾,增加數(shù)字電路的電磁輻射。所以,在數(shù)字電路中, 必須得權(quán)衡是否要加強(qiáng)模塊間的電源隔離(這個(gè)理論可以在“噪聲的起源” 4.4 節(jié)中看到)。

5.2、討論“電源紋波抑制”

5.2.1、綜述:對(duì)電源紋波的敏感程度

模擬、數(shù)字電路通常對(duì)“電源紋波噪聲”的抑制能力表現(xiàn)不同, 一般來(lái)講模擬器件對(duì)電源紋波不敏感, 基本不會(huì)將電源紋波反應(yīng)在輸出上; 而數(shù)字電路通常會(huì)將電源紋波完全反應(yīng)在輸出上。

注意:模擬電路對(duì)信號(hào)噪聲敏感,混進(jìn)了噪聲后,直接影響輸出信號(hào);數(shù)字電路對(duì)信號(hào)的噪聲相對(duì)不敏感,因?yàn)榧词乖肼暫艽螅?IO口都能正確地判斷出高低電平。

5.2.2、模擬電路電源紋波抑制能力強(qiáng)的原因

一般的功放和運(yùn)放處理的都是模擬信號(hào), 它們可以將信號(hào)放大、縮小N 倍,一般都有很強(qiáng)的電源紋波(噪聲)抑制能力。至少將電源上的噪聲衰減10000倍以上輸出。

為什么運(yùn)放等模擬器件有這么強(qiáng)的電源抑制能力?

歸根結(jié)底,因?yàn)?a href="http://www.nxhydt.com/tags/穩(wěn)壓電源/" target="_blank">穩(wěn)壓電源、恒流源、放大區(qū)的共射放大電路、非飽和狀態(tài)的射級(jí)放大電路等都有很強(qiáng)的電源紋波(噪聲) 抑制能力—— 而運(yùn)放、功放等都由這些基本電路作為其內(nèi)部的偏置、放大電路單元,所以電源紋波抑制比很強(qiáng)。

深入的理論剖析并非一章一節(jié)可以闡明, 并且作者也自認(rèn)為沒(méi)有足夠深厚的功底。下面將簡(jiǎn)單論述芯片內(nèi)部其中一種電路模型: 為何放大區(qū)的共射電路有很強(qiáng)的電源紋波抑制比!

PS:請(qǐng)有興趣深入研究的讀者可以理解《模擬電子技術(shù)基礎(chǔ)》(童詩(shī)白第4版3、4 章節(jié)等相關(guān)內(nèi)容)章節(jié)后,再進(jìn)一步學(xué)習(xí)。

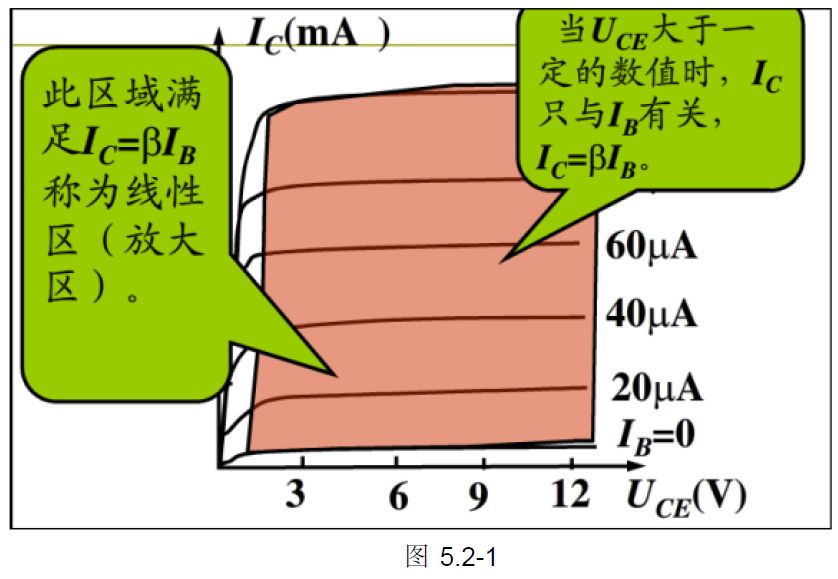

該圖是經(jīng)典的“三極管特征曲線(xiàn)圖” ,該圖已經(jīng)蘊(yùn)含了“共射放大區(qū)有很強(qiáng)的電源紋波抑制能力”這個(gè)信息!

真的嗎?不會(huì)吧?!

我啥時(shí)候騙過(guò)你? —— 請(qǐng)看分析。

對(duì)于共射放大電路。假設(shè)在放大區(qū)(圖中棕紅色區(qū)域) ,給三極管B極提供固定的電流Ib1 = 20uA,那么即使電源電壓( Uce電壓)在3~9V 波動(dòng),而Ic1 基本保持不變(這個(gè)圖中可以看到) 。Ic1 保持不變,意味著共射放大電路的電壓輸出不變!(理解這句話(huà)的前提是:理解共射放大電路。)

所以,對(duì)于圖中的三極管共射放大電路,假如在B極輸入一個(gè)信號(hào)Vin,即使電壓在3~9V波動(dòng),輸出只和輸入有關(guān),基本不受電源電壓波動(dòng)的影響!這表明:這個(gè)放大電路有很強(qiáng)的電源抑制能力!

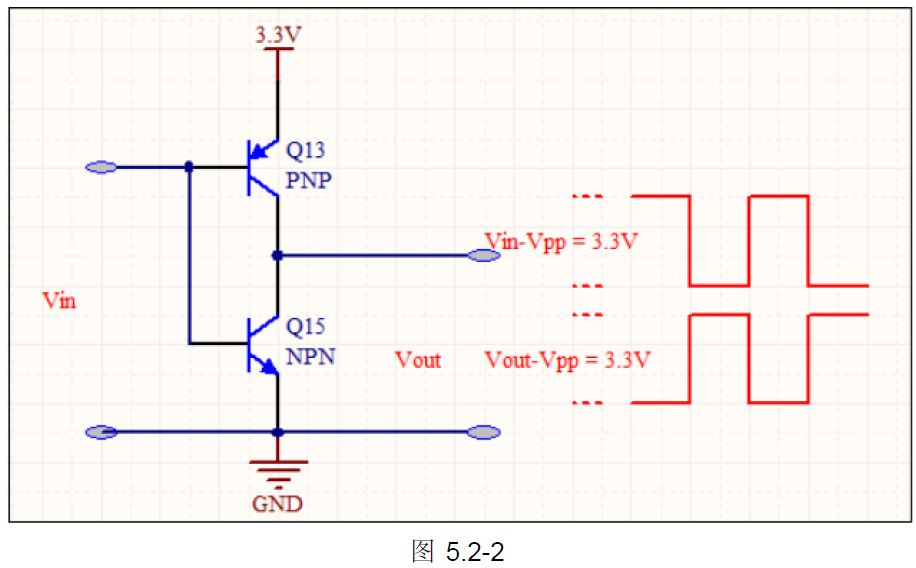

5.2.3、數(shù)字電路沒(méi)有電源紋波抑制能力

小功率三級(jí)管在輸出電流不是很大的情況下, 飽和導(dǎo)通的管壓降非常小, 可以認(rèn)為是0(對(duì)于這個(gè)壓降問(wèn)題, 有不少有了工作經(jīng)驗(yàn)的硬件工程師也經(jīng)常質(zhì)疑。那么,煩請(qǐng)各位用使用數(shù)據(jù)驗(yàn)證。呵呵!)。所以,當(dāng)輸入為3.3V 時(shí),輸出為3.3V。

當(dāng)電源電壓由3.3V 變?yōu)?0V 時(shí),所有數(shù)字電路都工作在10V 電源下,每個(gè)數(shù)字門(mén)電路的電壓也為10V——所以最終的結(jié)果是: Vin 和Vout 都變成一樣:都是10V 輸入、輸出電壓。

所以,由于數(shù)字電路IO 口的電壓工作在飽和導(dǎo)通狀態(tài)(不可以特殊的ECL等電路來(lái)論述),輸出電壓永遠(yuǎn)等于電源電壓。所以電源波動(dòng)毫不保留地反應(yīng)在輸出上,導(dǎo)致其電源紋波抑制能力為0. 這種特性在數(shù)字電路相互干擾的處理要十分留心。

6、本文精要

(1)因?yàn)橛泄餐亓髀窂蕉a(chǎn)生的干擾現(xiàn)象叫“共阻干擾” 。

(2)人耳朵在安靜環(huán)境中,通過(guò)耳機(jī),人們能清楚地聽(tīng)到毫伏級(jí)(幾毫伏)的音頻噪聲信號(hào),而普通示波器一般無(wú)法捕捉到這么微弱的波形。

(3)因?yàn)楣沧韪蓴_存在地噪聲的“敏感段PCB”,所以要單點(diǎn)接地,讓噪聲不要經(jīng)過(guò)敏感段PCB。

(4)單點(diǎn)接地的思想,在《印刷電路板排版設(shè)計(jì)》有很詳細(xì)的講解。(作者:鄭詩(shī)衛(wèi))

(5)一般來(lái)講模擬器件對(duì)電源紋波不敏感, 基本不會(huì)將電源紋波反應(yīng)在輸出上;而數(shù)字電路通常會(huì)將電源紋波完全反應(yīng)在輸出上。

-

pcb

+關(guān)注

關(guān)注

4295文章

22776瀏覽量

393255 -

電路板

+關(guān)注

關(guān)注

140文章

4810瀏覽量

96119 -

地線(xiàn)

+關(guān)注

關(guān)注

10文章

216瀏覽量

26691

原文標(biāo)題:寫(xiě)給硬件初學(xué)者--地線(xiàn)干擾的共阻干擾

文章出處:【微信號(hào):fcsde-sh,微信公眾號(hào):fcsde-sh】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

圖解PCB地線(xiàn)干擾及抑制

列車(chē)用高速數(shù)字PCB電路板抗干擾設(shè)計(jì)

射頻電路板抗干擾設(shè)計(jì)

【轉(zhuǎn)】PCB設(shè)計(jì)中的地線(xiàn)抑制和干擾

射頻PCB電路板的抗干擾設(shè)計(jì)

地線(xiàn)的共阻抗干擾與消除對(duì)策

PCB地線(xiàn)的干擾與抑制

列車(chē)用高速數(shù)字pcb電路板抗干擾設(shè)計(jì)

PCB中防止共阻抗干擾的地線(xiàn)設(shè)計(jì)解析

PCB電路抑制共阻抗干擾的措施有哪些

PCB及電路是如何抗干擾的

如何抑制PCB電路中的共阻干擾

地線(xiàn)干擾的共阻干擾深度解析(pcb電路板設(shè)計(jì)必知)

地線(xiàn)干擾的共阻干擾深度解析(pcb電路板設(shè)計(jì)必知)

評(píng)論