Dc綜合是基于路徑,每個路徑上都有Cell和net,所以基于路徑的綜合就是計算路徑上的delay和rc(dc是使用互連線模型進行估算)。

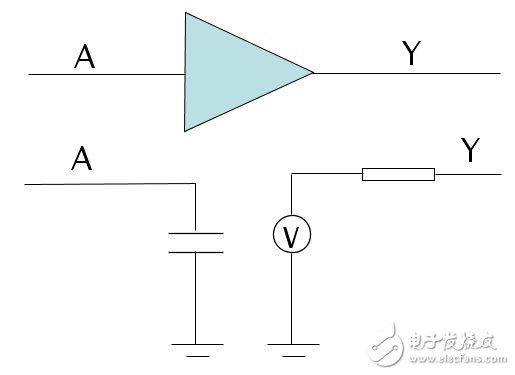

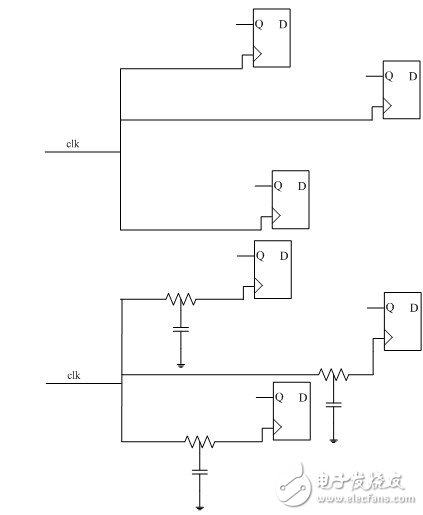

在了解delay和rc的計算時,我們要先了解一下一個cell對于drive(前級)和driven(后級)所用到的模型是什么。如下圖,一個buffer,從前級看過來是一個load(capacitance,想獲得這個load,可以通過load_of buffer/a獲得),從后級看來是一個drive(resistance)。電路的的驅動能力是上一級的1/R,即電阻的倒數,驅動能力大,說明看過去的電阻小,也說明這個器件比較大(大器件有較大的驅動能力)。電路的負載能力是下一級的load(即電容)總和,負載能力大,說明能驅動下級的期間就很多。

大器件是大電容,小電阻,而小器件是小電容,大電阻。理解這些,對于dc綜合以及后端apr版圖都有很好的操作。

對于cell的延遲,dc是根據input_transition和out_load對應的查找表來計算的。

對于net的延遲,dc是根據wire_load_model中的fanout_length和resistance,capacitance,area的查找表計算的。

例如:

Wire_load(small){

Resistance: 0.2;

Capacitance: 1.0;

Area:0;

Slop:1.0;

Fanout_length(1,0.022);

Fanout_length(2,0.046);

Fanout_length(3,0.070);

Fanout_length(4,0.095);

}

比如現在扇出是2,

根據fanout_length(2,0.046)可以知道這個互連線的長度是0.046,然后再根據capacitance,resistence可以得出這個互連線的電容為:0.046x1.0,互連線電阻為:0.046x0.02。

如果扇出是5,在查找表中沒有找到fanout_length為5的項,互連線長度將會是=fanout_length(4,0.095)+(5-4)*slop=0.095+1*1.0=1.095

得出了rc就可以計算出信號的transition時間=2.2RC。

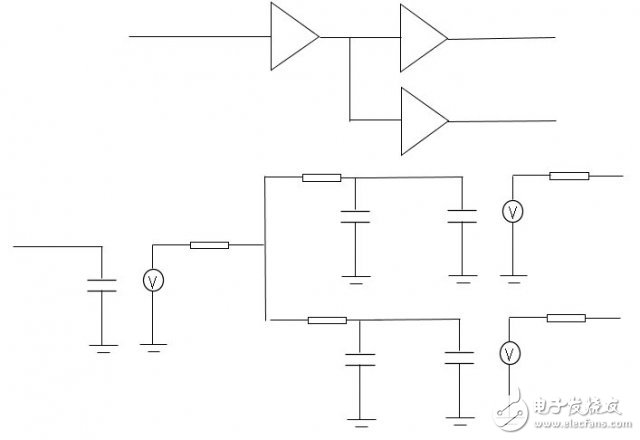

實際的互聯線如下:

2.2RC=(Rnet+Rout)×(Cnet+Cin)

無論如何,要記住的就是dc是基于路徑分析的(怎么劃分路徑請參考另一篇:),每個路徑上有cell延遲和net延遲,而cell延遲是根據input_transition和out_lod得出的,net延遲是根據fanout_length,resistance,capacitanc得出的。驅動和電阻成反比,負載和電容成正比。

由上面可以知道fanout影響到load(capacitance),transition,delay。了解了上面,我們來理解下dc中對design建模,所用到的一些跟fanout有關的參數。

Dc中的約束,其實就是給chip設計一個環境,比如驅動這個chip輸入端口的cell,或者這個chip輸出端口驅動了那些單元或者端口接入了哪些負載,以及這個芯片的工藝,電壓,溫度,等等。。。

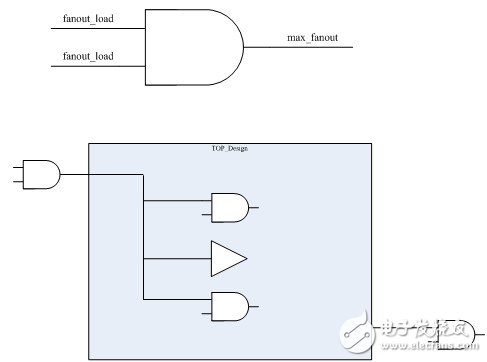

對于一個cell來說,輸出端口具有max_fanout屬性,輸入端口有fanout_load屬性。

例如將一個AND2作為design的驅動cell(set_driving_cell),這樣就把AND2的max_fanout屬性加在了輸入端口上。如果一個AND2的輸出端口max_fanout是5,輸入端口fanout_load是2。一個buffer輸入端口的fanout_load是3。那么這個AND2的輸出端可以接2個AND2,或者可以接一個buffer,或者可以接一個buffer和一個AND2。如上圖所示,則會引起DC產生DRC錯誤。因為輸入端口的fanout_load=2XAND2+buffer=7,超過了AND2的max_fanout2.如果使用了系統提供的set_max_fanout 5 [all_inputs],將會忽略set_driving_cell中cell的max_fanout屬性,而使用set_max_fanout屬性

如果將一個AND2作為design的負載,那么這個輸出端口上的fanout_load屬性將會為2.dc中一般的做法是set_fanout_load [expr [get_attribute slow/and2/a fanout_load] *xxx] [all_outputs],來設置輸出端口的fanout_load屬性。

這樣dc就可以根據這些設置,選擇優化端口處的器件,以及時序。

說道fanout,所以順帶說明一下容易混淆的max_fanout,max_capacitance。如上圖所示,

輸入端口的fanout_load=2個與門的fanout_load和一個buffer的fanout_load。

輸入端口的load(capacitance)=2個與門的load_of和一個buffer的load_of。(如果通過set_load設置了輸入端口,另外還要加上set_load的值)。

Max_fanout檢查的是輸入端口的fanout_load最大值,

Max_capacitance檢查的是輸入端口load值。

兩者概念不同。

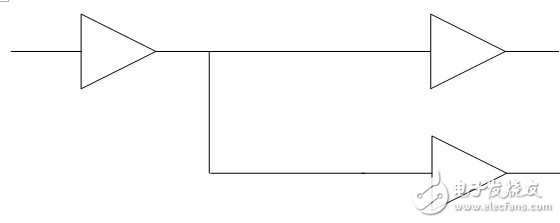

下面講下fanout與delay,看如下一個例子:

到buffer的net延遲是2,buffer延遲是1,fanout為1時net延遲為3,每增加一個扇出,net延遲增加2.如果一個信號經過這個扇出網絡后,那么延遲為:2+1+(3+(8-1)×2)=20;

如果把扇出結構優化成如下形式:

那么信號經過這個網絡后,延遲為:2+1+2+1+(3+(4-1)×2)=15.

那么延遲減少了5。

接下來講一下skew,既然知道了fanout對于delay的影響,下面看一個例子:

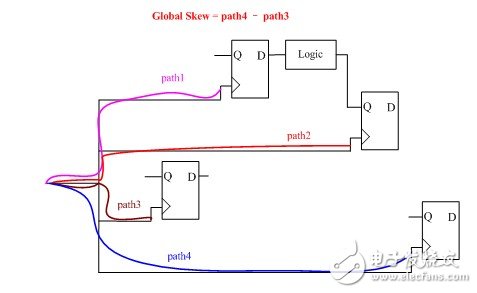

由于時鐘到每個觸發器的互連線長短不一樣,造成信號到達clock pin的時間也不一樣,觸發器也不會同時翻轉。Skew的定義就是最長路徑減去最短路徑的值。

根據時鐘域以及路徑關系,skew可以分為global skew,local skew,interclock skew。

Global skew是指,同一時鐘域,任意路徑的最大skew。

Local skew是指,同一時鐘域,任意2個有邏輯關聯關系的路徑最大skew。

interClock skew是指,不同時鐘域之間路徑的最大skew

另外還有一個useful skew。本來打算在setup time和hold time中講解。這里先大概說下

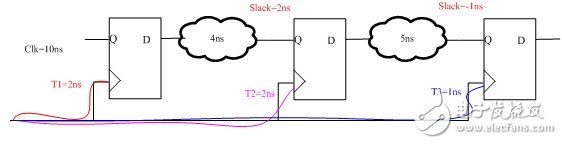

如下圖:時鐘周期為10ns,各時鐘路徑延遲如下:可以看到有一條路徑的slack為-1,說明這條路徑違規。可以看到與這條路徑相關的skew是T3-T2=-1ns。

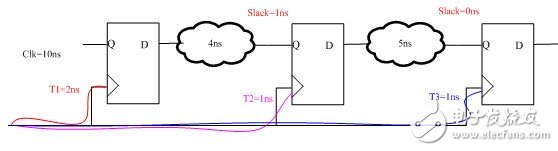

下面我們利用useful skew向前面一個slack比較充裕的路徑(slack=2ns)借點time,來修正現在這條路徑。如下圖:

經過useful skew,修正了原來的violation。

這就是useful skew的作用,可以向前,或者向后接time來修正violation

-

RC

+關注

關注

0文章

225瀏覽量

48758 -

Delay

+關注

關注

0文章

10瀏覽量

10877

發布評論請先 登錄

相關推薦

元器件在電路中的作用以及使用方法

示波器的使用方法

Skew Correction Using Delay Li

什么是參比電極_參比電極使用方法_參比電極的作用是什么

時序分析之useful skew的作用分析

useful skew的作用及使用方法

useful skew的作用及使用方法

評論