一些多層高速板上的貼片晶振有時在設計時會挖空相鄰的平面層,如下所示:

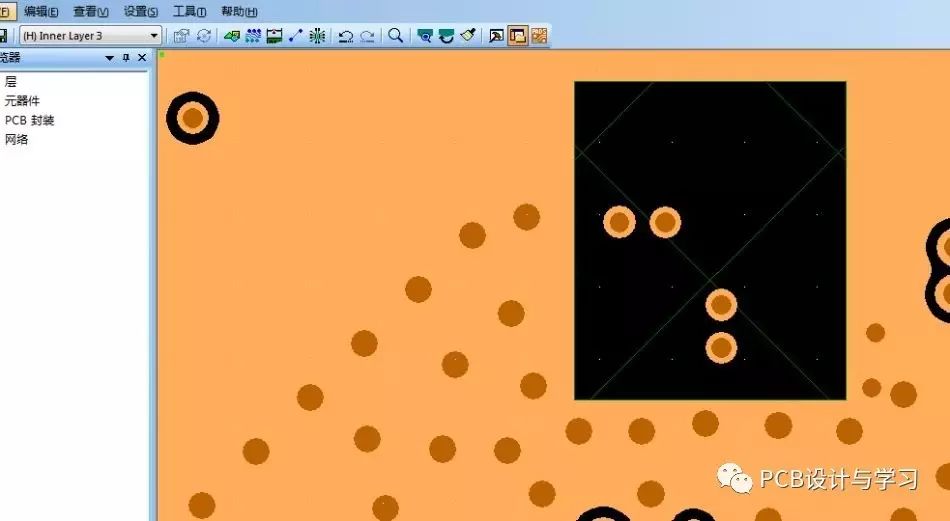

這是一塊四層板,底層有一個貼片晶振,

第三層的地平面在設計時用禁止區域將晶振正下面的地平面挖空,

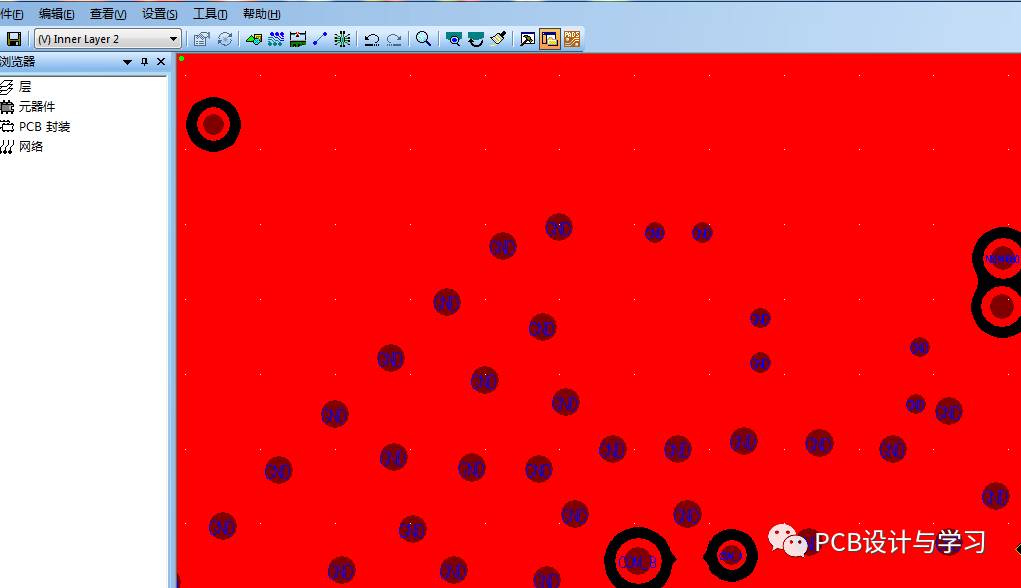

第二層晶振下面的平面沒有挖空,

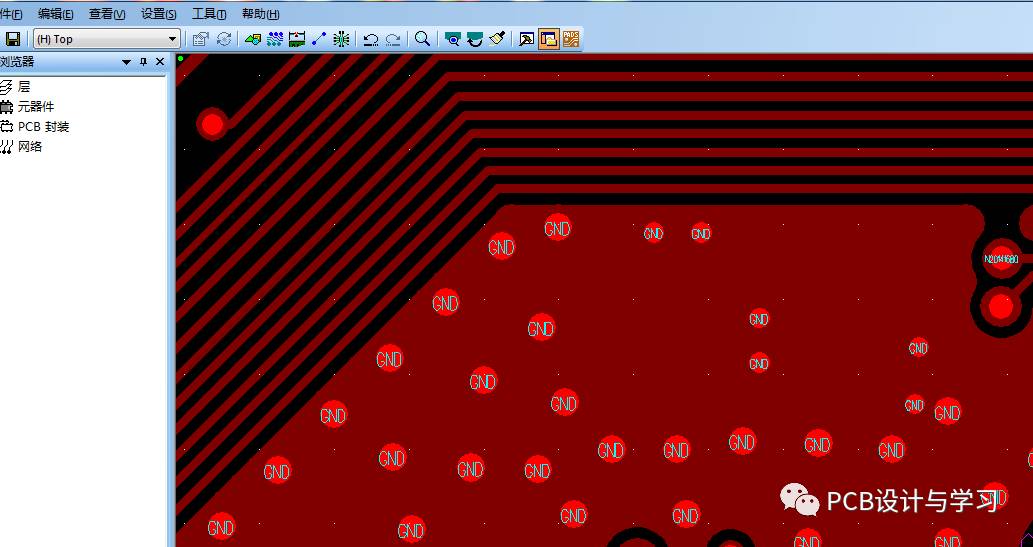

頂層也沒有挖空。

很多人不解,在貼片晶振鄰近平面層挖空的用意是什么呢?

因為貼片晶振兩個焊盤是長方形的焊盤,剛好和鄰近的平面形成了一個電容器,由電容計算公式C=εs/4πkd可知,長方形的焊盤與鄰近的地平面之間寄生的電容量和焊盤的面積S,焊盤到平面的距離d有關。一般情況焊盤的面積S都不會變了,所以晶振長方形的焊盤與鄰近的地平面之間寄生的電容量主要由焊盤到平面的距離d決定。d一般都很小,比如1.6MM的四板,層壓結構如下圖所示,

由圖可知,芯板占了主要的厚度,焊盤到平面的距離d只有3.5mil,非常的小,如果用電容計算公式C=εs/4πkd算出來的寄生電容值是很大的。

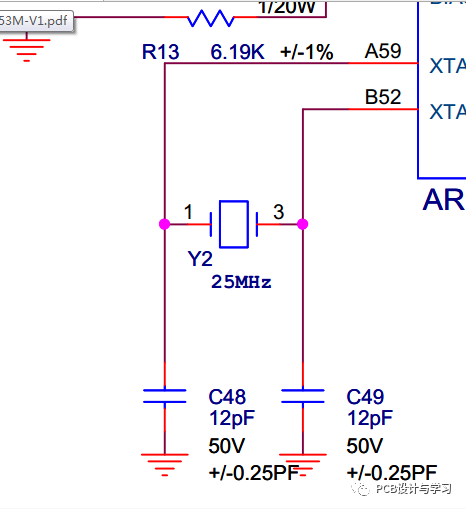

有個例子是這樣的,原廠有個參考原理圖,晶振的諧振電容是

12pF,

但是PCB樣板做回來后,測試發現樣板的頻偏很大。

后來把晶振的兩個諧振電容改成4.7pF后,頻偏才有所改善。

由此可見,貼片晶振的兩個焊盤腳與其下方的平面存在著寄生電容。寄生電容會影響系統的頻偏,頻偏過大時,系統在平常工作環境可以正常運行,但是在極限條件下,如高低溫條件,很有可能不能正常運行了。如果貼片晶振的兩個焊盤腳與其下方的平面存在著寄生電容很大,諧振電容不貼時,晶振的頻偏也是很大。那么這個PCB板用來生產,出來的產品雖然平常工作時沒有什么問題 ,但是在一些高低溫的條件下,就可能會出問題了,這是一個很大的風險。所以在設計PCB時,遇到貼片晶振時,應該考慮挖空晶振下方的平面層。

-

電路板

+關注

關注

140文章

4907瀏覽量

97426 -

貼片

+關注

關注

10文章

865瀏覽量

36881 -

晶振

+關注

關注

34文章

2826瀏覽量

67908 -

PCB設計

+關注

關注

394文章

4670瀏覽量

85292

原文標題:多層高速電路板上貼片晶振鄰近參考層挖空的用意

文章出處:【微信號:gh_eb821dd72e77,微信公眾號:PCB和原理圖設計與共享】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

多層高速pcb設計中那些不得不說的事

多層高速板有貼片晶振時在pcb設計需考慮挖空相鄰的平面層

多層高速板有貼片晶振時在pcb設計需考慮挖空相鄰的平面層

評論