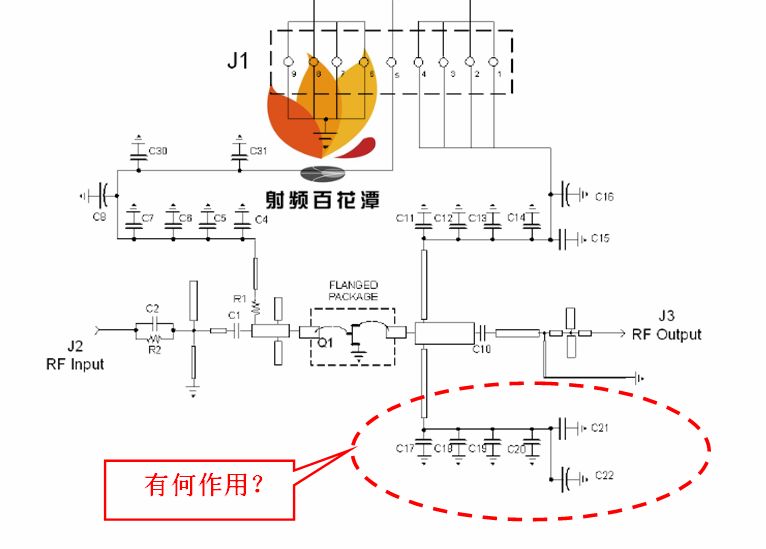

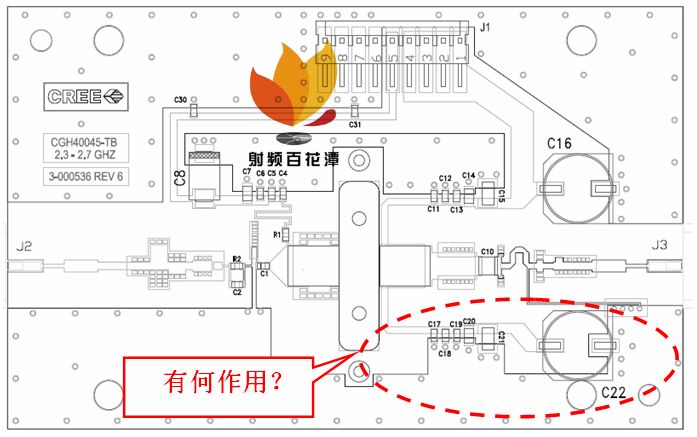

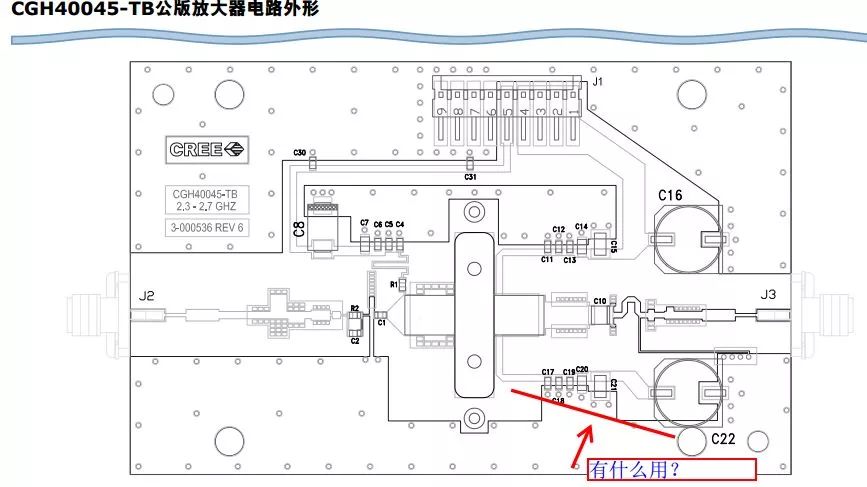

CGH40045F-TB漏級偏置電路采用對稱設計,主要分析原因在于降低偏置網絡阻抗,提高視頻帶寬VBW,從而減小功放管的電記憶效應。

圖1 CGH40045-TB PCB圖

以下簡單介紹下VBW與電記憶效應:

低阻抗通路的帶寬被稱為視頻帶寬(VBW),范圍為100KHz~200MHz,個人理解為調制信號的帶寬,即信道帶寬,跟輸入的調制信號有關。

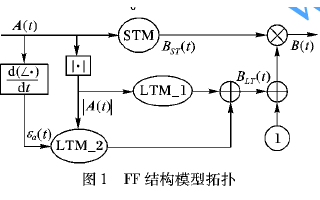

功率管的記憶效應分為熱記憶效應和電記憶效應,熱記憶效應主要跟晶體管溝道溫度周期有關,電記憶效應主要來源于功率放大電路的直流偏置。記憶效應的本質在于當前的時刻不僅跟輸入信號有關,還跟過去的某一時刻有關,體現在增益和相位上。

當功放管在數字預失真方案中,減小記憶效應對功放的影響顯的尤為重要,偏置電路是記憶效應的一個重要來源,現實中,功率管的漏極到電源之間的電路阻抗(video impedance)在低頻(VBW 10MHz)時并非為0,該阻抗的存在使得加載到功率管漏極的電壓并非是個恒定值,而是隨著功放輸入信號變化。如果是純阻性的,僅僅引起增益壓縮,如果存在電抗部分,則引起記憶效應,因此在設計時,需要該阻抗越小越好。同時工程實驗證明在同樣的輸入信號,同樣的DPD系統中,較大的視頻帶寬(VBW)的ACPR要比較小的視頻帶寬(VBW)的ACPR要好。

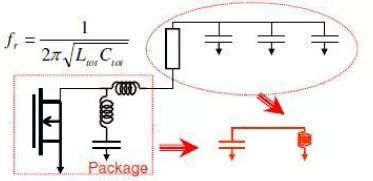

圖2 晶體管VBW計算公式

圖2所示,fr表征的是晶體管輸出段低頻諧振頻率,頻率越高,VBW越寬,Ltot指得是供電線跟旁路電容組成的等效電感,Ctot指的是晶體管漏級之間的電容,因此在可操作性上提高VBW的措施是降低Ltot。

具體措施如下:

1.如圖1所示,漏級雙供電方式,并聯降低阻抗,減小低頻信號的影響。

2.將uF級的電容靠近漏級放置,電容的工作頻率實際大于其SFR,這樣電容呈感性,從而減小Ltot,提高VBW。

3.縮短漏級供電線長度,小于1/4波長,但是這樣會犧牲一部分功率。

-

電路

+關注

關注

172文章

5852瀏覽量

171931 -

射頻

+關注

關注

104文章

5551瀏覽量

167578 -

Cree

+關注

關注

3文章

91瀏覽量

34454

原文標題:CREE射頻功放提高視頻帶寬降低記憶效應設計分析

文章出處:【微信號:gh_f97d2589983b,微信公眾號:高速射頻百花潭】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CREE射頻功放提高視頻帶寬降低記憶效應設計分析

CREE射頻功放提高視頻帶寬降低記憶效應設計分析

評論