當下,5G商用化的步伐正在逐步加快,移動通信正在迎來一個新的時代。然而,不同國家劃分的5G通信頻段各不相同,適應這個頻段的芯片并不一定能夠適應那個頻段,于是就可能出現尷尬的一幕:出國旅游,5G手機竟然“失靈”了。如何解決5G芯片“水土不服”的問題呢?

近日,電子科學與工程學院(示范性微電子學院)博士生張凈植在2018年國際固態電路會議(ISSCC)上發表論文,提出了一種“基于強耦合變壓器的電流提升技術”,并在此基礎上研發了一款芯片實現了多個頻段全部覆蓋,讓5G“全球通”變成了可能。

△ISSCC大會主席、MIT教授Anantha Chandrakasan(右)和多倫多大學教授Kenneth C. Smith為張凈植頒發“Silkroad Award”獎牌

張凈植為論文第一作者,其導師康凱教授為論文通訊作者,電子科技大學為唯一作者單位。據了解,該論文是中國大陸地區發表在該會議上的首篇有關毫米波集成電路設計的論文,為我校首次以第一作者單位在該會議正文單元上發表的論文。

張凈植同時獲得該會議頒發的“Silkroad Award”,該獎項是頒發給以第一作者身份第一次在這個會議上發表論文的亞太地區的學生。張凈植成為中國大陸地區歷史上第4位獲此殊榮的學生,同時也是大會歷史上第20位獲此獎項的學生。

“通用芯片”:解決“5G時代”的新問題

張凈植研發的這款芯片,源于三年前的偶然發現。2015年,康凱教授正承擔國家5G技術方面的重大專項,張凈植有機會參與其中,負責其中關于頻率源的部分研究任務。

在4G時代,各個國家所用的頻段都在3GHz以下,不少手機生產商采用了多個芯片來覆蓋所有頻段,并且在頻率較低的情況下,器件性能好,即使用一個芯片來覆蓋所有頻段,設計也相對比較簡單。而到了5G時代,不同的國家劃分的應用于5G通信的頻段大大提高,中國用的是24.75-27.5GHz和37-42.5GHz頻段,美國用的是27.5-28.35GHz、37-38.6GHz和38.6-40GHz頻段,歐洲用的是24.25-27.5GHz頻段,日韓則采用26.5-29.5GHz。而同一個手機要支持這么多不同的高頻段,則相對困難,這可能就會導致我們出國旅游時手機無法正常通信。

那么問題來了,究竟能否研發一款寬頻帶“通用芯片”全部覆蓋以上各個不同的高頻段呢?

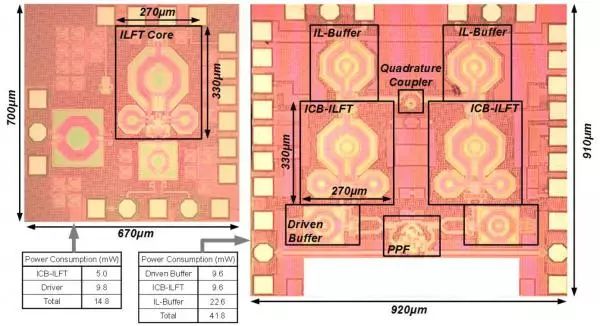

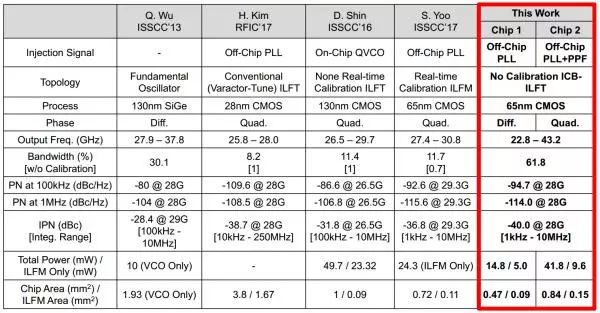

答案是肯定的。張凈植在國際固態電路會議展示的研究成果,就是兩方小小的“通用芯片”:大的芯片只有910微米×920微米(1微米=10-6米),小的芯片為700微米×670微米,面積都小于1平方毫米,大小相當于一根針的橫截面。

△左邊是差分輸出芯片,是核心電路的驗證模塊;右邊是正交輸出芯片,是完整的、可以用于5G系統的芯片。

這種小芯片卻具有“兼容并蓄”的廣闊“胸懷”,極大地提升了注入鎖定倍頻器的工作帶寬。它的專業稱呼是“基于CMOS(互補金屬氧化物半導體)工藝的超寬帶注入鎖定倍頻器”,簡而言之,就是為了解決5G芯片在不同電磁頻段“水土不服”的難題而專門設計的。

在與業界最先進技術的比較中,該技術在僅消耗兩倍功耗的情況下,將工作帶寬提升了5.2倍。它還解決了毫米波頻段中“低相位噪聲信號源的大帶寬設計”挑戰,為毫米波領域超寬帶低相位噪聲信號源設計提供了一個可行方案,對5G通信的高頻段多頻帶應用有著實際意義。

歷時三年:過程一波三折

從2015年萌生想法到2016年9月真正開始設計,張凈植嘗試了多種思路。他首先想到,輸入電流和工作帶寬是正相關的,如果要提高電路的帶寬就得想辦法增強輸入電流。而要增強輸入電流,一種方法是增大輸入信號,但一般而言,外部給的輸入信號大小是固定的,所以此路不通。還有一種方法,就是提高輸入極的增益,但業界已經把輸入極優化得很好,想進一步提升基本不太可能。

在不斷提出問題又不斷自我否定之后,張凈植提出了一個突破性的想法:能不能用無源電路把電流提升,然后插入一個變壓器,這樣就可以使電流提高N倍同時能把帶寬也提高N倍呢?又經過三個月的努力,他和團隊在2016年12月份完成芯片設計并進行了第一次流片。

2017年3月,終于拿到芯片。測試的結果令他非常激動:和2017年國際國內最新的研究成果相比,他們的研究已經在性能上遠遠勝出。此前,業界做出的芯片工作帶寬大概在10-30%,而他們的芯片帶寬可以達到60%以上。于是,他和康凱教授商量,很有必要再次優化設計并做第二次流片。

芯片優化設計的時間十分緊湊:做芯片一般要依次完成原理圖、版圖、模塊級聯,最后才是完成總版并進行評估,但到了2017年4月,他們才剛做到模塊級聯環節,進度比預期慢很多。考慮到芯片設計不容有失,否則流片就會功虧一簣,他們決定不能急于求成,最終到5月才完成第二版設計。

由于芯片造價成本高昂,而且準備第二次流片時沒有項目支撐,他們經過許多周折,向國內外其他單位尋求支持。第二次流片終于結束,但在過海關時卻卡了很久,直到8月底才拿到第二版芯片。他們快速行動,花了一周時間測試芯片的性能,然后快速寫論文投給了國際固態電路會議。10月,國際固態電路會議給出了評審意見。團隊成員終于松了一口氣:總算沒有失之交臂!

△右邊兩欄為該論文達到的工作指標,其中,帶寬為22.8-43.2GHz,積分相位噪聲為-40.0dBc,功耗為5.0mW。與業內同類工作對比,該成果的帶寬達到了其他工作的5.2倍,同時沒有帶來相位噪聲的惡化。

肯吃苦、多拼搏,為行業做更多貢獻

2018年2月,國際固態電路會議召開。該會議是目前國際公認集成電路領域的權威會議,有著“Chip Olympics(芯片奧林匹克)”的雅稱,自1954年成立以來,共發表相關學術論文7500余篇。中國大陸地區作者于2005年發表首篇論文,截至目前在該會議上發表的相關文章有24篇。

此前,我校碩士生郭開喆、余益明同學(原電子工程學院)和本科生周雄同學(原通信與信息工程學院)的論文曾入選該會議“學生科研前瞻”單元匯報展示。如今,張凈植再次創造歷史,并與來自日本北海道大學的博士生Kodai Ueyoshi共同獲得大會為亞太地區的優秀學生論文設立的“Silkroad Award”獎項。

對于這次研究成果,張凈植十分感激康凱教授及團隊的大力支持。他說,集成電路不同于其他學科,每一次設計完成以后拿出去加工,就沒有改正的機會了。每一次流片的成本都非常大,設計過程中的任何一點小失誤,都可能導致全盤皆輸。正是康凱教授和團隊在芯片設計方面的悉心指導和嚴格要求,以及對流片工作的大力支持,才使他有機會參與到這項重要的研究工作中來,并取得了一定的成績。

張凈植表示,“做這一行非常累,要做好足夠的心理準備,熬夜也是常有的。只有肯吃苦、肯拼搏,才能為這個行業做出更多貢獻!”目前,團隊正在進一步優化設計,準備做第三版設計和流片工作。他說,“我們的芯片設計從一開始就是面向應用并且和工業界緊密結合的,隨著5G通信時代的到來和各種應用逐漸推廣,我們的芯片也可能會進入產品化階段,應用到手機和基站,讓5G也可以實現‘全球通’”。

-

5G

+關注

關注

1353文章

48370瀏覽量

563414 -

固態電路

+關注

關注

0文章

10瀏覽量

8020

原文標題:恭喜電子科大!5G“通用芯片, 轟動全球!

文章出處:【微信號:icunion,微信公眾號:半導體行業聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IP地址與5G時代的萬物互聯

紫光展銳5G芯片通過墨西哥運營商Telcel測試

嵌入式設備中的4G/5G模塊管理

請問Lierda 5G EVK具體支持哪些linux系統?

請問mx880 5G數據終端可以設置優先5G網絡嗎?

成都新基訊發布兩款5G芯片,推動5G通信產業發展

美格智能聯合羅德與施瓦茨完成5G RedCap模組SRM813Q驗證,推動5G輕量化全面商用

5G 外置天線

“通用芯片”:解決“5G時代”的新問題

“通用芯片”:解決“5G時代”的新問題

評論