鎖存器Latch概述

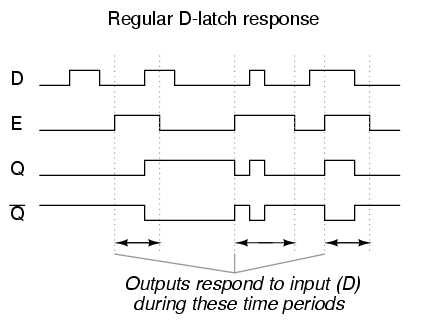

鎖存器(Latch)是一種對脈沖電平敏感的存儲單元電路,它們可以在特定輸入脈沖電平作用下改變狀態(tài)。鎖存,就是把信號暫存以維持某種電平狀態(tài)。鎖存器的最主要作用是緩存,其次完成高速的控制器與慢速的外設(shè)的不同步問題,再其次是解決驅(qū)動的問題,最后是解決一個I/O口既能輸出也能輸入的問題。鎖存器是利用電平控制數(shù)據(jù)的輸入,它包括不帶使能控制的鎖存器和帶使能控制的鎖存器。

鎖存器Latch結(jié)構(gòu)

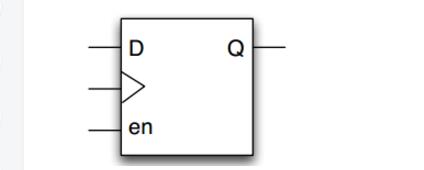

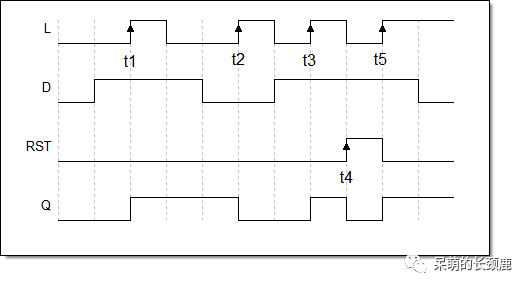

latch:鎖存器,是由電平觸發(fā),結(jié)構(gòu)圖如下:

鎖存器latch的優(yōu)缺點(diǎn)

優(yōu)點(diǎn):

1、面積比ff小

門電路是構(gòu)建組合邏輯電路的基礎(chǔ),而鎖存器和觸發(fā)器是構(gòu)建時序邏輯電路的基礎(chǔ)。門電路是由晶體管構(gòu)成的,鎖存器是由門電路構(gòu)成的,而觸發(fā)器是由鎖存器構(gòu)成的。也就是晶體管-》門電路-》鎖存器-》觸發(fā)器,前一級是后一級的基礎(chǔ)。latch完成同一個功能所需要的門較觸發(fā)器要少,所以在asic中用的較多。

2、速度比ff快

用在地址鎖存是很合適的,不過一定要保證所有的latch信號源的質(zhì)量,鎖存器在CPU設(shè)計(jì)中很常見,正是由于它的應(yīng)用使得CPU的速度比外部IO部件邏輯快許多。

缺點(diǎn):

1、電平觸發(fā),非同步設(shè)計(jì),受布線延遲影響較大,很難保證輸出沒有毛刺產(chǎn)生

2、latch將靜態(tài)時序分析變得極為復(fù)雜

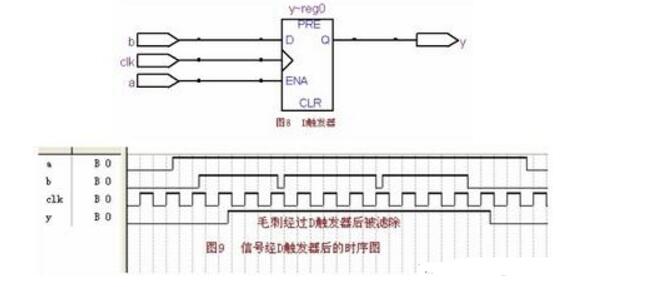

觸發(fā)器Flip-flop結(jié)構(gòu)

lip-flop:觸發(fā)器,是時鐘邊沿觸發(fā),可存儲1bitdata,是register的基本組成單位,結(jié)構(gòu)圖如下:

flip-flop的優(yōu)缺點(diǎn)

優(yōu)點(diǎn):

1、邊沿觸發(fā),同步設(shè)計(jì),不容易受毛刺的印象

2、時序分析簡單

缺點(diǎn):

1、面積比latch大,消耗的門電路比latch多

鎖存器Latch和觸發(fā)器flipflop的區(qū)別

1、鎖存器Latch和觸發(fā)器flipflop

鎖存器能根據(jù)輸入端把結(jié)果自行保持;觸發(fā)器是指由時鐘邊沿觸發(fā)的存儲器單元;由敏感信號(電平,邊沿)控制的鎖存器就是觸發(fā)器;

2、寫電路時,產(chǎn)生鎖存器的原因

if語句中,沒有寫else,默認(rèn)保持原值,產(chǎn)生鎖存器,可能不是想要的結(jié)果;

case語句中,沒有寫完整default項(xiàng),也容易產(chǎn)生鎖存器;

例子:

always@(aorb)

begin

if(a)q=b;

end

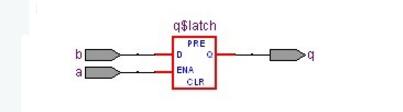

產(chǎn)生了鎖存器,如下

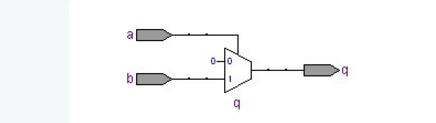

沒有鎖存器的情況

always@(aorb)

begin

if(a)q=b;

elseq=0;

end

3、避免使用D鎖存器,盡量使用D觸發(fā)器

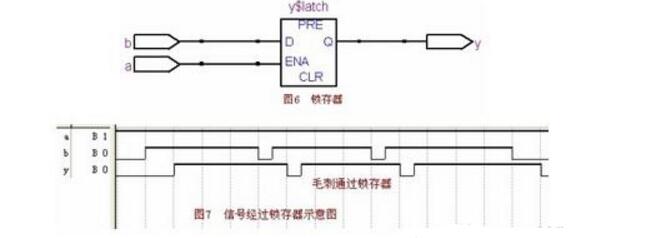

D鎖存器

moduletest_latch(y,a,b);

outputy;inputa;inputb;regy;

always@(aorb)begin

if(a==1’b1)

y=b;

endendmodule

D觸發(fā)器

moduletest_d(y,clk,a,b);

outputy;inputclk;inputa;inputb;regy;

always@(posedgeclk)begin

if(a==1‘b1)

y=b;

endendmodule

從圖8可知,例10對應(yīng)的電路是D觸發(fā)器。信號a被綜合成D觸發(fā)器的使能端,只有在時鐘上沿到來且a為高時,b信號的值才能傳遞給a;只要在時鐘上升沿期間信號b是穩(wěn)定,即使在其他時候b還有毛刺,經(jīng)過D觸發(fā)器后數(shù)據(jù)是穩(wěn)定的,毛刺被濾除。

-

鎖存器

+關(guān)注

關(guān)注

8文章

905瀏覽量

41448 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

1996瀏覽量

61057

發(fā)布評論請先 登錄

相關(guān)推薦

鎖存器Latch和觸發(fā)器Flip-flop有何區(qū)別

鎖存器Latch和觸發(fā)器Flip-flop有何區(qū)別

評論