什么叫DCM(Digital Clock Management)?

DCM內部是DLL(Delay Lock Loop(?)結構,對時鐘偏移量的調節是通過長的延時線形成的。DCM的參數里有一個PHASESHIFT(相移),可以從0變到255。所以我們可以假設內部結構里從Clkin到Clk_1x之間應該有256根延時線(實際上,由于對不同頻率的時鐘都可以從0變到255,延時線的真正數目應該比這個大得多)。DCM總會把輸入時鐘Clkin和反饋時鐘Clkfb相比較,如果它們的延時差不等于所設置的PHASESHIFT,DCM就會改變在Clkin和Clk_1x之間的延時線數目,直到相等為止。這個從不等到相等所花的時間,就是輸出時鐘鎖定的時間,相等以后,Lock_flag標識才會升高。

當DCM發現Clkin和Clkfb位相差不等于PHASESHIFT的時候,卻去調節Clk_1x和Clkin之間延時,所以如果Clk_1x和Clkfb不相關的話,那就永遠也不能鎖定了。呵呵。

如何使用DCM

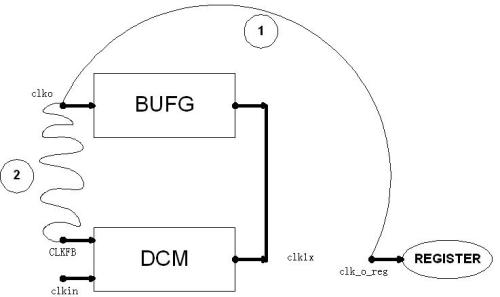

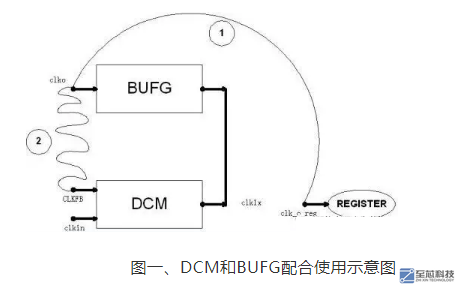

DCM一般和BUFG配合使用,要加上BUFG,應該是為了增強時鐘的驅動能力。DCM的一般使用方法是,將其輸出Clk_1x接在BUFG的輸入引腳上,BUFG的輸出引腳反饋回來接在DCM的反饋時鐘腳CLKFB上。另外,在FPGA里,只有BUFG的輸出引腳接在時鐘網絡上,所以一般來說你可以不使用DCM,但你一定會使用BUFG。有些兄弟總喜歡直接將外部輸入的時鐘驅動內部的寄存器,其實這個時候雖然你沒有明顯地例化BUFG,但工具會自動給你加上的。

使用DCM可以消除時鐘Skew

使用DCM可以消除時鐘Skew。這個東西一直是我以前所沒有想清楚的,時鐘從DCM輸出開始走線到寄存器,這段Skew的時間總是存在的,為什么用DCM就可以消除呢?直到有一天忽然豁然開朗,才明白其原委。對高手來說,也許是極為Easy的事情,但也許有些朋友并不一定了解,所以寫出來和大家共享。

為說明方便起見,我們將BUFG的輸出引腳叫做Clk_o,從Clk_o走全局時鐘布線到寄存器時叫做Clk_o_reg,從Clk_o走線到DCM的反饋引腳CLKFB上時叫Clkfb,如圖所示。實際上Clk_o, Clk_o_reg, Clkfb全部是用導線連在一起的。所謂時鐘Skew,指的就是Clk_o到Clk_o_reg之間的延時。如果打開FPGA_Editor看底層的結構,就可以發現雖然DCM和BUFG離得很近,但是從Clk_o到Clkfb卻繞了很長一段才走回來,從而導致從Clk_o到Clk_o_reg和Clkfb的延時大致相等。總之就是Clk_o_reg和Clkfb的相位應該相等。所以當DCM調節Clkin和Clkfb的相位相等時,實際上就調節了Clkin和Clk_o_reg相等。而至于Clk_1x和Clk_o的相位必然是超前于Clkin, Clkfb, Clk_o_reg的,而Clk_1x和Clk_o之間的延時就很明顯,就是經過那個BUFG的延遲時間。

對時鐘Skew的進一步討論

最后,說一說時鐘Skew的概念。時鐘Skew實際上指的是時鐘驅動不同的寄存器時,由于寄存器之間可能會隔得比較遠,所以時鐘到達不同的寄存器的時間可能會不一樣,這個時間差稱為時鐘Skew。這種時鐘Skew可以通過時鐘樹來解決,也就是使時鐘布線形成一種樹狀結構,使得時鐘到每一個寄存器的距離是一樣的。很多FPGA芯片里就布了這樣的時鐘樹結構。也就是說,在這種芯片里,時鐘Skew基本上是不存在的。

說到這里,似乎有了一個矛盾,既然時鐘Skew的問題用時鐘樹就解決了,那么為什么還需要DCM+BUFG來解決這個問題?另外,既然時鐘Skew指的時時鐘驅動不同寄存器之間的延時,那么上面所說的Clk_o到Clk_o_reg豈非不能稱為時鐘Skew?

先說后一個問題。在一塊FPGA內部,時鐘Skew問題確實已經被FPGA的時鐘方案樹解決,在這個前提下Clk_o到Clk_o_reg充其量只能叫做時鐘延時,而不能稱之為時鐘Skew。可惜的是FPGA的設計不可能永遠只在內部做事情,它必然和外部交換數據。例如從外部傳過來一個32位的數據以及隨路時鐘,數據和隨路時鐘之間滿足建立保持時間關系(Setup Hold Time),你如何將這32位的數據接收進來?如果你不使用DCM,直接將Clkin接在BUFG的輸入引腳上,那么從你的Clk_o_reg就必然和Clkin之間有個延時,那么你的Clk_o_reg還能保持和進來的數據之間的建立保持關系嗎?顯然不能。相反,如果你采用了DCM,接上反饋時鐘,那么Clk_o_reg和Clkin同相,就可以利用它去鎖存進來的數據。可見,DCM+BUFG的方案就是為了解決這個問題。而這個時候Clk_o到Clk_o_reg的延時,我們可以看到做內部寄存器和其他芯片傳過來的數據之間的時鐘Skew。

由此,我們可以得出一個推論,從晶振出來的時鐘作為FPGA的系統時鐘時,我們可以不經過DCM,而直接接到BUFG上就可以,因為我們并不在意從Clkin到Clk_o_reg的這段延時。

-

時鐘

+關注

關注

10文章

1720瀏覽量

131364 -

DCM

+關注

關注

0文章

157瀏覽量

26417

發布評論請先 登錄

相關推薦

基于FPGA的DCM時鐘管理單元概述

DCM產生時鐘的邊緣過沖~~

DCM在FPGA中指的是什么?

怎么消除5ns偏斜

DCM外部反饋路徑有什么問題?

Spartan 6 DCM LOCKED沒有輸出時鐘

DCM輸出時鐘約束的示例

如何使用DCM減少時鐘偏差?如何使用DCM來增加時鐘?

如何使用DCM,DCM使用說明

FPGA DCM時鐘管理單元簡介及原理

賽靈思DCM概述和應用技巧

FPGA的DCM時鐘管理單元概述

使用DCM怎樣消除時鐘Skew?

使用DCM怎樣消除時鐘Skew?

評論