國產襯底片在雙極型集成電路制造中的應用

摘要:隨著國產襯底的生產工藝和控制能力的不斷提升,國產襯底的應用也越來越廣。作者就國產襯底在雙極型集成電路制造中普遍關心的問題做了全面的評估,包括物理參數、電參數、圓片合格率,以及大規模生產的工程能力指數。評估結果說明國產襯底在品質上已經完全能夠媲美進口襯底,滿足大規模生產的需求。

關鍵詞:集成電路制造;硅襯底;雙極型集成電路;襯底物理參數;襯底翹曲;失焦;電參數;工程能力指數。

1 引言

國產硅襯底在分立器件,如 TVS,肖特基二極管和 VDMOS 等產品的生產制造中已經被大量使用,但在雙極型集成電路生產制造中少有使用,主要原因是雙極型集成電路在生產過程中有著大量的熱高溫過程,如外延生長工藝,DN 深磷和 DP 對通隔離的推進工藝,這些工藝溫度都在 1 150 ℃ 以上,且 DP 或 DN 推進工藝的時間又在 24 小時以上,襯底的應力變化和翹曲變形都比較大,稍有不慎,就會引起應力碎片或光刻失焦,造成報廢或低合格率。所以在大規模使用國產襯底上,我們一直比較保守,不能形成規模生產。

國產襯底的質量在最近幾年有了長足的進步,重復性,一致性也取得了很大的提升。加之最近襯底供應偏緊,襯底國產化的工作愈發緊迫。本文作者通過對國產襯底和國外主流大廠的襯底的對比試驗,就硅襯底本身的性能,產品的電參數(PCM 參數), 圓片的合格率做了全面地比較,同時對大規模生產中硅片是否翹曲進行了跟蹤觀察。電參數的過程能力指數也做了統計計算,其結果非常喜人,為國產襯底在大規模生產中的應用奠定了基礎。

2 實驗

2.1 實驗對象

選取了雙極型集成電路中的典型產品,電源管理和音頻功放產品作為評估對象。其工藝過程中都含有 1 150 ℃的外延工藝,和 1 150 ℃,24 小時以上的 DN 或 DP 推進工藝。

2.2 實驗方法及結果比較

分別就進口襯底和國產襯底作分組對比,首先比較硅襯底的物理特性參數,其次比較電參數特性和不同產品的圓片合格率。

最后,對國產襯底在大規模生產中實際表現進行跟蹤評估。主要考核是否在生產過程中出現硅片破損,光刻失焦(defocus) 和在 e-chuck 機臺上的滑片現象。

同時對主要 PCM 數據的工程能力指數(Cpk)進行評估。

3 分組對比數據

3.1 硅襯底的物理參數對比結果

表 1,主要測量參數對比 。圖 1,正面魔鏡下對比。圖 2,背面顯微鏡下對比。結論如下。

(1)硅片的幾何尺寸,電阻率徑向梯度、氧梯度、氧含量、碳含量、TIR、STIR、OISF、 位錯密度等參數國產襯底片和進口襯底片相當, 沒有顯著差異。

(2)硅片表面(正面和背面)的鏡檢結果顯示,國產的襯底片和進口襯底片相當,沒有顯著差異。

(3)WARP 和 TTV 參數,在數值上國產襯底片略差于進口襯底片,雖然都在規范內,但差異確實存在。

3.2 分組電參數(PCM)對比

由于 PCM 測量參數比較多,我們挑選了影響器件特性的主要參數,重點比較了下面 6 個參數。LPNP_BETA,NPN__BETA,R_CHAIN_SP/CO/IN,R_CHAIN_SN/CO/IN,BVISO 和 R_PINCH(BASE)。

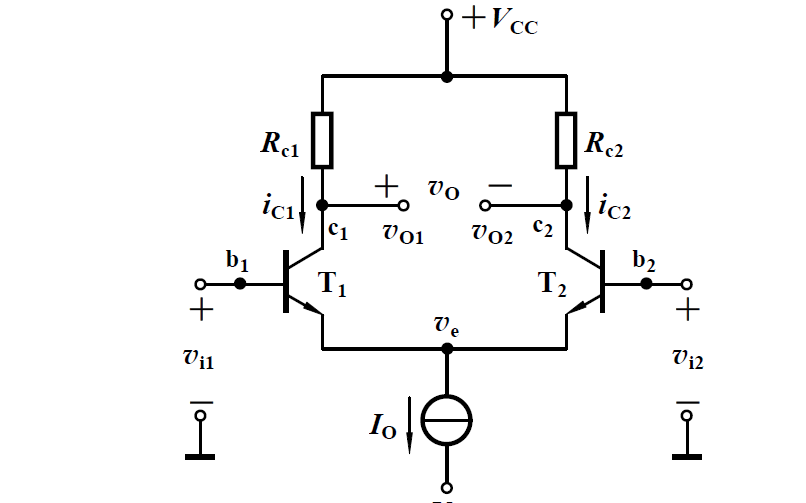

PNP 晶體管和 NPN 晶體管的放大倍數 BETA 是雙極性集成電路的重要參數,對最終產品的特性有著重大影響。

BVISO 是隔離區的耐壓,反映隔離的水平,耐壓低器件漏電流會顯著增加。

R_PINCH(BASE) 是發射極和基極的擠壓電阻,反映了對結深和結濃度的控制能力。

R_CHAIN_SP/CO/IN, R_CHAIN_SN/CO/IN 是 SP 區域和 SN 區域的接觸鏈電阻,由于和襯底硅直接接觸,也列為考察對象。

數據對比詳見圖 3~圖 8。

這些 PCM 數據都非常接近,符合匹配的條件。在 LPNP-BETA 的項目上國產襯底的表現稍微好于進口襯底。在電參數方面國產襯底和進口襯底已經沒有顯著差異了,微小的差異也在完全可以接受的范圍之內,有些參數國產襯底表現得更好。

3.3 分組圓片合格率對比

表 2 是音頻產品和電源產品的分組圓片合格率對比結果。國產襯底和進口襯底在圓片合格率上沒有明顯區別,都達到了一個比較高的水平。

4 大規模生產中電參數性能表現

我們對 3.2 節中的重點的 6 個電參數作了 Cpk統計,共包括了 2 000 片圓片,計 10 000 個原始數據源,其過程能力指數 CpK 如表 3 所示。我們的要求是 CpK 大于等于 1.66,所有 CpK 指數都達標,符合大生產的需求。

5 硅襯底本身的穩定性考察

在硅襯底生產中,硅襯底中會有各種應力存在,同時硅襯底片會有一定的翹曲度,如果控制不好,會引起后續集成電路生產中的各種問題,主要表現為以下幾個方面。

(1)應力碎片。由于雙極型集成電路生產過程中,長時間熱高溫過程比較多。特別容易引起應力碎片,其表現為在舟中某一片硅片會沿晶向一分為二或者莫名其妙的斷裂。

(2)滑片。由于硅襯底的翹曲,造成 e-chuck不能很好地吸住硅片,硅片在設備的極板上有滑動現象,造成設備報警,嚴重時會造成碎片,需要工程師現場處置,引起額外的設備宕機時間。

(3)光刻失焦現象。還是由于硅襯底的翹曲,造成光刻工藝不能完美地對焦,局部區域無法聚焦,這些區域的圖形不能完美地形成,最終引起圓片低合格率。

我們在線跟蹤了十萬片國產襯底片的流片情況, 統計了萬片的不良事件發生片數,表 4 是十萬片的實際數據統計結果。

這些結果表明: 雖然翹曲度在數值上略差于進口片,但襯底廠商的生產制程管控能力還是很強的,重復性一致性非常好,襯底片能夠適應后續這么多的熱高溫處理過程的挑戰而保持良好的狀態,沒有明顯的變形翹曲,不良事件的發生片數幾乎為零。這對規模化大生產能力的形成與提升有著至關重要的作用。

6 結語

通過主要物理參數和電參數的比較,說明國產襯底的性能已經和進口襯底相媲美。合格率數據上已經看不出區別。至于 WARP 和 TTV 的不足,可以通過優化砂漿配液[1]、線切割工藝[2],優化腐蝕工藝和優化拋光工藝 [3-5]來改善。

大規模生產的數據表明,國產襯底的質量十分穩定,其工藝過程能力數據也非常好,所以國產襯底可以完全地,完美地取代進口襯底。受此鼓舞,我們也在積極驗證 200 mm 的國產襯底,初步結果也符合預期。國產襯底的時代真正來臨了。

-

硅襯底

+關注

關注

1文章

16瀏覽量

9407 -

集成電路制造

+關注

關注

0文章

11瀏覽量

6936

原文標題:國產襯底片在雙極型集成電路制造中的應用

文章出處:【微信號:appic-cn,微信公眾號:集成電路應用雜志】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

集成電路制造技術的應用

中國集成電路發展探秘

《炬豐科技-半導體工藝》超大規模集成電路制造技術簡介

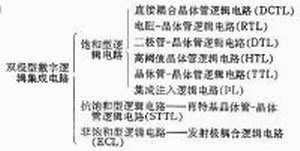

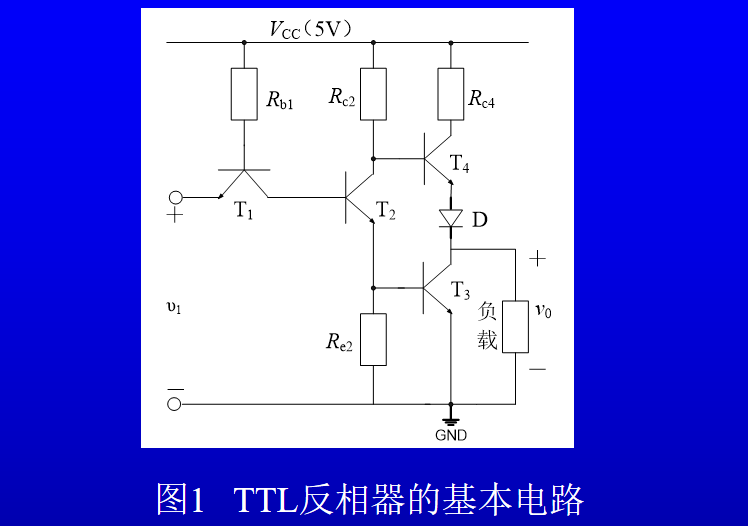

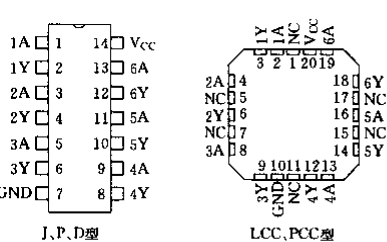

什么是雙極型集成電路

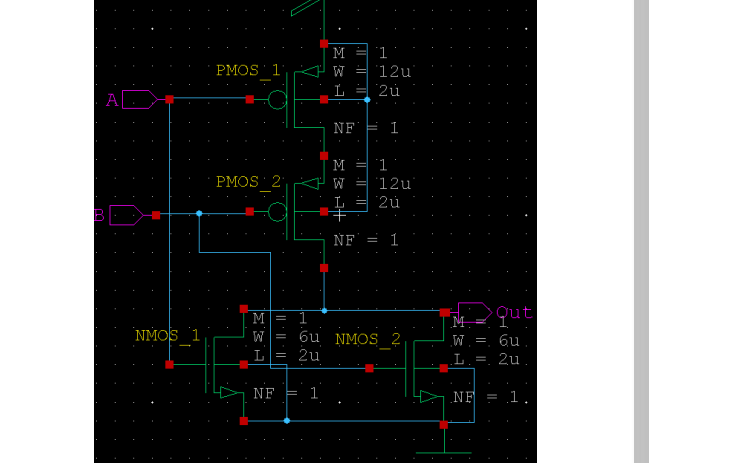

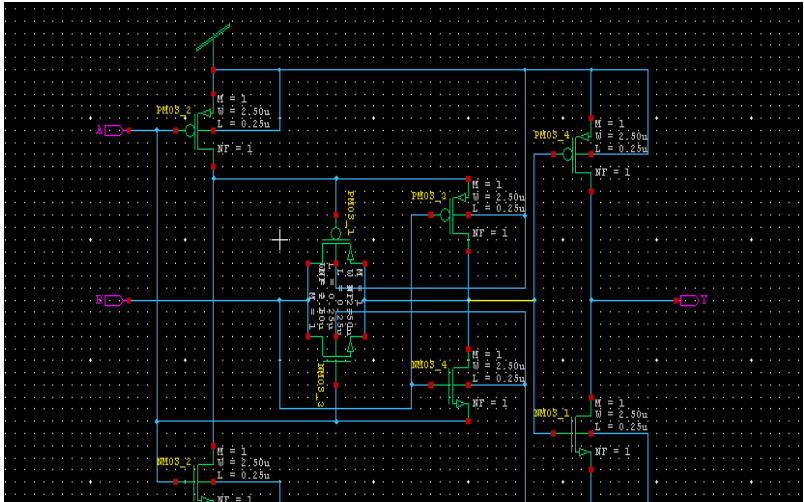

Cadence軟件的介紹和CMOS集成電路的版圖設計詳細資料概述

IC設計基礎教程之數字集成電路基本單元與版圖的詳細資料概述

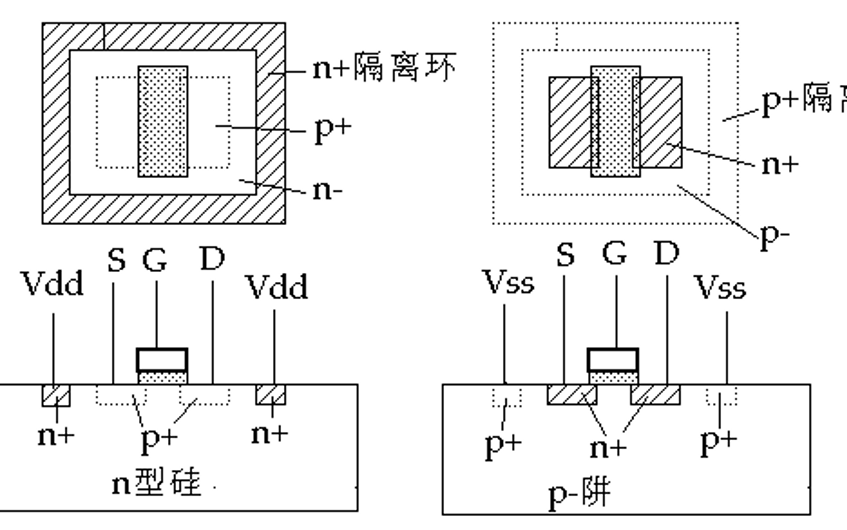

CMOS集成電路制造工藝的詳細資料說明

國產襯底片的發展在雙極型集成電路制造中的應用詳細資料概述

國產襯底片的發展在雙極型集成電路制造中的應用詳細資料概述

評論