在ARM體系中,通常有以下3種方式控制程序的執行流程:

? 在正常程序執行過程中,每執行一條ARM指令,程序計數器寄存器(PC)的值加4個字節;每執行一條Thumb指令,程序計數器寄存器(PC)的值加2個字節。整個過程是順序執行。

? 通過跳轉指令,程序可以跳轉到特定的地址標號處執行,或者跳轉到特定的子程序處執行。其中,B指令用于執行跳轉操作;BL指令在執行跳轉操作的同時,保存子程序的返回地址;BX指令在執行跳轉操作的同時,根據目標地址的最低位可以將程序狀態切換到Thumb狀態;BLX指令執行3個操作:跳轉到目標地址處執行,保存了子程序的返回地址,根據目標地址的最低位可以將程序狀態切換到Thumb狀態。

? 當異常中斷發生時,系統執行完當前指令后,將跳轉到相應的異常中斷處理程序處執行。在當異常中斷處理程序執行完成后,程序返回到發生中斷的指令的下一條指令處執行。在進入異常中斷處理程序時,要保存被中斷的程序的執行現場,在從異常中斷處理程序退出時,要恢復被中斷的程序的執行現場。

ARM體系中異常中斷種類:

? 復位(Reset):當處理器的復位引腳有效時,系統產生復位異常中斷,程序跳轉到復位異常中斷處理程序處執行。復位異常中斷通常用在下面兩種情況:系統加電時和系統復位時。跳轉到復位中斷向量處執行,稱為軟復位。

? 未定義指令(Undefined Instruction):當ARM處理器或者是系統中的協處理器認為當前指令未定義時,產生未定義的指令異常中斷。

? 軟件中斷(Software Interrupt SWI):這是一個由用戶定義的中斷指令。可用于用戶模式下的程序調用特權操作指令。在實時操作系統中可以通過該機制實現系統功能調用。

? 指令預取中止(Prefetch Abort):如果處理器預取的指令的地址不存在,或者該地址不允許當前指令訪問,當該被預取的指令執行時,處理器產生指令預取中止異常中斷。

? 數據訪問中止(Data Abort):如果數據訪問指令的目標地址不存在,或者該地址不允許當前指令訪問,處理器產生數據訪問中止異常中斷。

? 外部中斷請求(IRQ):當處理器的外部中斷請求引腳有效,而且CPSR寄存器的I控制位被清除時,處理器產生外部中斷請求(IRQ)異常中斷。系統中各外設通常通過該異常中斷請求處理器服務。

? 快速中斷請求(FIQ):當處理器的外部快速中斷請求引腳有效,而且CPSR寄存器的F控制位被清除時,處理器產生外部中斷請求(FIQ)異常中斷。

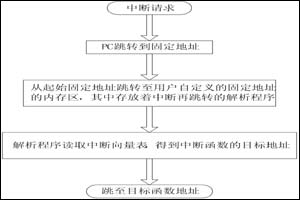

對異常中斷的響應過程(這幾點都是ARM核自己已經完成的動作):

? 保存處理器當前狀態、中斷屏蔽位以及各條件標志為。這是通過將當前程序狀態寄存器CPSR的內容保存到將要執行的異常中斷對應的SPSR寄存器中實現的。各異常中斷有自己的物理SPSR寄存器。

? 設置當前程序狀態寄存器CPSR中相應的為。包括:設置CPSR中的位,使處理器進入當前相應的執行模式(處理器模式);設置CPSR中的位,禁止IRQ中斷,當進入FIQ模式時,禁止FIQ中斷。

? 將寄存器lr_mode設置成返回地址。

? 將程序計數器值(PC),設置成該異常中斷的中斷向量地址,從而跳轉到相應的異常中斷處理程序處執行。

從異常中斷處理程序中返回(這些返回動作是需要自己寫代碼完成的):

? 恢復被中斷的程序的處理器狀態,即將SPSR_mode寄存器內容復制到CPSR中。

? 返回到發生異常中斷的指令的下一條指令執行,即將lr_mode寄存器的內容復制到程序計算器PC中。

復位異常中斷處理程序不需要返回。在復位異常中斷處理程序開始整個用戶程序的執行,因而它不需要返回。

-

寄存器

+關注

關注

31文章

5317瀏覽量

120003 -

ARM處理器

+關注

關注

6文章

360瀏覽量

41662

原文標題:ARM異常中斷處理

文章出處:【微信號:mcugeek,微信公眾號:MCU開發加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ARM處理器中斷處理的編程實現

ARM S3C4510B系統的異常中斷機制解析

ARM體系中異常中斷種類及處理辦法

ARM體系中異常中斷種類及處理辦法

評論