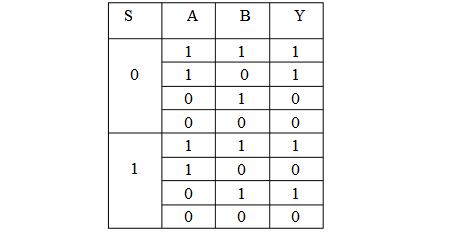

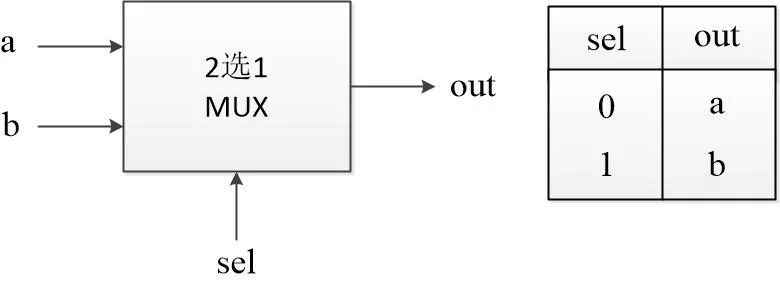

二選一多路選擇器真值表

二選一多路選擇器邏輯表達(dá)式為:

根據(jù)邏輯表達(dá)式所列真值表如下圖所示

1位二選一多路選擇器及其VHDL描述

實(shí)驗(yàn)步驟:

1、新建一個(gè)文件夾,打開Quartus2軟件,選擇FLE-》NEW菜單,在彈出的NEW對話框中選擇DEVICE DESGIN FILE 頁的原理圖文件編輯器輸入項(xiàng)VHDL FILE,按確定鍵打開VHDL 編輯器窗口;

2、在VHDL 編輯器窗口輸入2選1多路選擇器的VHDL 描述;

PORT(ab:IN BIT:

s:INBIT:

y :OUT BIT):END ENITY mux2 1a:

ARCHITECTURE one OF mux21a IS

BEG IN

y《=aWHEN s=‘0“ELSE b:ENDARCHITECTURE one;或者:

ENTITYmux21a IS

PORT(ab:IN BIT:

s:INBIT:

y:OUT BIT);END ENTITYmux2 1a;

ARCHITECTURE one OF mux2 1a IS

BEG IN

y《=a WHEN s=”O(jiān)“ELSE b;ENDARCHITECTURE one;

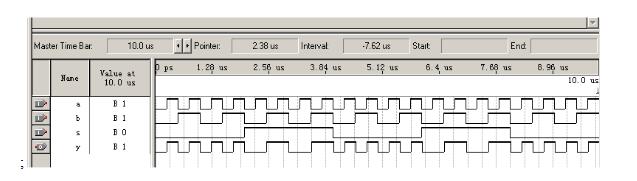

3、打開波形編輯器,分別運(yùn)行2 選1多路選擇器,觀察他們的輸出波形:

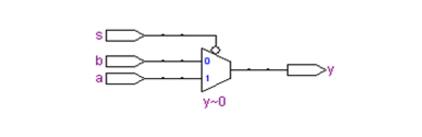

4、調(diào)出VHDL 描述產(chǎn)生的2 選1多路選擇器的原理圖。點(diǎn)擊TOOLS-》NELIST

VIEWERS-》RTLVIEWERS,即調(diào)出VHDL描述產(chǎn)生的2 選1多路選擇器的RIL 電路圖,如下所示

實(shí)驗(yàn)小結(jié):

經(jīng)過本次試驗(yàn)初步了解了Quartus2 軟件的使用,及VHDL 表達(dá)和設(shè)計(jì)電路的方法。

1位的二選一多路選擇器的邏輯表達(dá)式實(shí)現(xiàn)

設(shè)計(jì)來源

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/03/17 08:26:28

// Design Name:

// Module Name: disTwo2OneSelector

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module disTwo2OneSelector(

input sl,

input a,

input b,

output out

);

reg out;

always @(sl or a or b)

begin

// “? :”表達(dá)式的返回值必須賦給一個(gè)變量。

out=sl?b:a;

end

endmodule

模擬源

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/03/17 08:45:19

// Design Name:

// Module Name: simTwo2OneSelector

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module simTwo2OneSelector(

);

reg simA,simB,simSl;

wire simOut;

initial

begin

simSl=0;

simA=0;

simB=0;

// 在激勵(lì)程序運(yùn)行的瞬間,“simSl=0;simA=0;simB=0;”語句已經(jīng)執(zhí)行完了。

// 在0-10個(gè)時(shí)間單位,激勵(lì)程序的狀態(tài)保持不變。

#10

simSl=0;

simA=1;

simB=0;

#10

simSl=1;

simA=0;

simB=0;

#10

simSl=1;

simA=0;

simB=1;

end

// 設(shè)計(jì)文件模塊名 對象名 (。設(shè)計(jì)文件模塊中的類中的參數(shù)(激勵(lì)文件模塊中的類中的參數(shù)))

disTwo2OneSelector objTwo2OneSelector(.a(simA),.b(simB),.sl(simSl),.out(simOut));

endmodule

-

vhdl

+關(guān)注

關(guān)注

30文章

816瀏覽量

127951 -

多路選擇器

+關(guān)注

關(guān)注

1文章

22瀏覽量

6487

發(fā)布評論請先 登錄

相關(guān)推薦

至芯科技之a(chǎn)ltera 系列FPGA教程 第九篇 二選一多路選擇器的設(shè)計(jì)

至芯科技之a(chǎn)ltera 系列FPGA教程 第十篇 二選一多路選擇器激勵(lì)的設(shè)計(jì)

【夢翼師兄今日分享】 二選一數(shù)據(jù)選擇器的設(shè)計(jì)

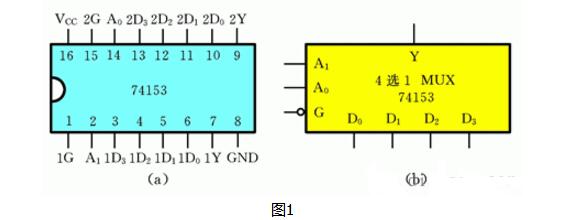

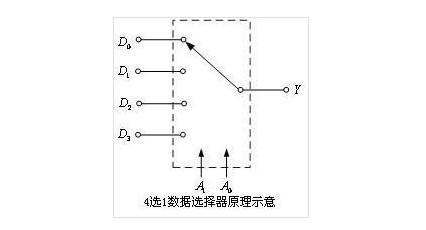

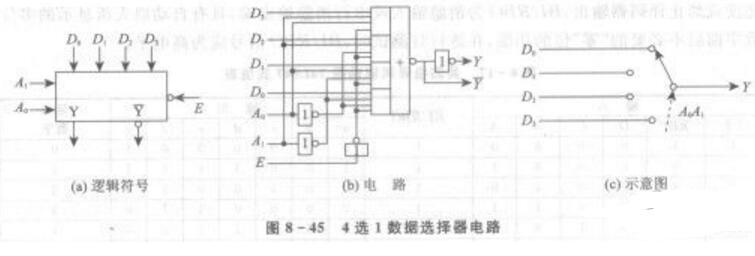

EDA四選一多路選擇器的設(shè)計(jì)

4選1多路選擇器是什么?

基于FPGA的多路選擇器設(shè)計(jì)(附代碼)

八選一多路選擇器Verilog代碼及仿真結(jié)果MUX_8

eda四選一多路選擇器的設(shè)計(jì)

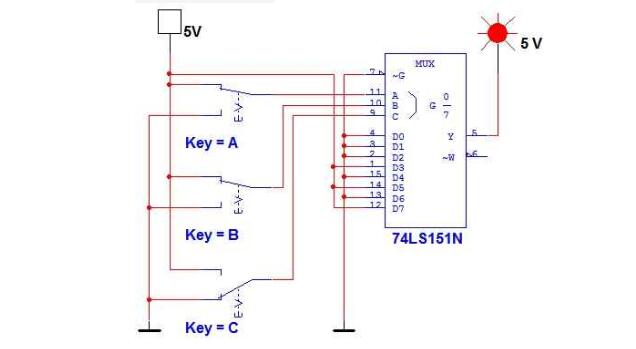

8選1多路選擇器電路圖(五款8選1多路選擇器電路)

EDA四選一多路選擇器的設(shè)計(jì)資料下載

設(shè)計(jì)一個(gè)1位的二選一多路選擇器及其VHDL描述

設(shè)計(jì)一個(gè)1位的二選一多路選擇器及其VHDL描述

評論