Dual-Gate TFT-LCD 抖動算法FRC 研究與實現

在 TFT-LCD 驅動的關鍵設計技術中,抖動算法 FRC(frame rate control)是一種重要的技術。它能夠用 6 bit source 的輸出來達到 8 bit full color(16.7 M colors)的顯示效果,這樣可以降低數據傳輸率以降低功耗,同時可以節省源驅動(Source Driver, SD)芯片的面積。通過分析和實踐,提出了針對用于平板電腦的 Dual-Gate TFT-LCD 屏和翻轉方式,需要采用優化的 FRC 算法提高顯示效果。在應用于平板電腦的 dual-gate TFT-LCD 屏的 FRC 方案中,分析了傳統方案產生周期性豎線的原因,然后提出了改進方案,消除了豎線,提高了顯示質量。最后,總結了 FRC 算法具體需要考慮的因素。

1 FRC 算法原理

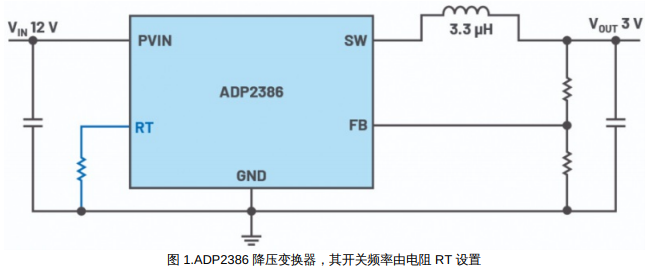

TFT-LCD(薄膜晶體管液晶顯示器)是目前主流的顯示技術,它是利用液晶的旋轉和透光的特性進行顯示的一種技術,具有平板化,輕薄等特點。在 TFT-LCD 屏 的關鍵設計技術中,抖動算法 FRC(frame rate control)是一種重要的技術。FRC(Frame Rate Control)像素抖動算法是利用人眼的視覺惰性,對相鄰的 2 個灰階實施時間和空間混色來實現中間亮度的顯示,從而達到在 TFT-LCD 上實現目標灰階顯示的一種方法。每一種顏色均由 RGB 分量組成,RGB 分量的比特數決定了顏色的豐富度。比特數越大代表顯示的顏色越豐富。很多LCD panel 使用 6 bit source driver,6 bit 驅動芯片理論上只能產生 64 種模擬電位,對應 64 種灰階,無法滿足畫面質量要求。因此需要抖動算法也就是 FRC 算法來實現全彩色的顯示。FRC 算法對輸入的 8 bit 圖像數據的低 2 位作為抖動矩陣的選擇依據,取高 6 bit 為輸出給顯示驅動芯片的輸入數據,通過時間和空間平均,混合出其他灰階。混合原理如圖 1。

8 bit 中低 2 位為 0,灰階直接由 6 bit 低位補 0。其他的中間灰階由這些相鄰的低 2 位灰階為“00”的像素按比例混合。

FRC 算法在 253,254,255 灰階時會發生飽和現象,無法實現真正的 8 bit 顏色顯示。

這是 FRC 算法的一個局限,所以現在又提出了HiFRC 算法,通過擴展 1 bit,然后低 3 bit 選擇,512 種灰階中選擇 256 個灰階來實現全彩色。這個不在本文中詳述。

圖 2 給出了 FRC 具體的混合方法,有“1”的地方就是將高 6 位數據加 1,有“0”的地方就是高 6 位直接輸出。圖 2 符合上面公式列出的像素混色方法。

當低 2 bit 為“00”時,不用進行混合,直接高 6 bit 輸出。

當低 2 bit 為“01”時,在一幀內。

目標灰階(6 bit)=3/4×(高 6 bit 灰階)+1/4×(高 6 bit 灰階 +1)

在同樣的位置的灰階,4 幀之間,也符合上面公式的混色原理。

當低 2 bit 為“10”時,在一幀內。

目標灰階(6 bit)=2/4×(高 6 bit 灰階)+2/4×(高 6 bit 灰階 +1)

在同樣的位置的灰階,4 幀之間,也符合上面公式的混色原理。

當低 2 bit為“11”時,在一幀內。

目標灰階(6 bit)=1/4×(高 6 bit 灰階)+3/4×(高 6 bit 灰階 +1)

在同樣的位置的灰階,4 幀之間,也符合上面公式的混色原理。

以上的 FRC 圖形算法滿足下面 2 個要求。

亮階與暗階在空間上的分布是均勻的,且幀間比例是相同的。

對任何一個像素而言,算法循環完成后,亮階與暗階比例是一致的。

但是這個算法只考慮了像素,沒有考慮到子像素。而 TFT 每個像素中含有 RGB 3 個子像素,對應著 SD 芯片的 3 個輸出通道。算法圖形以子像素為單位進行排列,可以獲得更好的算法效果。

2 FRC 算法應用

2.1 Dual-gate 顯示面板

Dual-gate panel 指的是 SD 芯片的一個輸出連接到相鄰 2 列子像素上,控制 2 個子像素的柵開關在一行的顯示時間內交替打開。這樣 SD 芯片的一個輸出通道就可以分時復用地驅動 2 個子像素,從而可以節省一半的 SD 芯片面積。

Gate 和 source panel 連接圖如圖 3 所示。Gate driver 一行一行打開,source driver 把數據一行一行送進顯示器。Dual-gate 每次送進去的就是半行奇子像素或者半行偶子像素。

2.2 用于 PAD TFT-LCD 屏驅動芯片極性翻轉

用于 PAD TFT-LCD 屏驅動芯片包括 tcon,source driver 和直流 VCOM 電壓等功能模塊。直流 VCOM 就是 VCOM 電壓固定,source 電壓正負翻轉。驅動芯片配合 Dual gate 屏的時序,可以支持 1-dot,2-dot 和 column inversion。考慮到功耗和顯示效果的平衡,默認的 polarity 翻轉方式是 2 dot inversion。2-dot inversion 實際是 1+2 dot inversion,source 極性“ 2 行”翻轉 1 次。這里的 2 行實際指的是 source 的 2 行,對于 dual gate panel 來說,其實就是 panel 顯示的一行。輸出 channel 的極性如圖 4 所示。

因為 TFT-LCD 的液晶顯示特性,source 電壓和 VCOM 的壓差表示真正顯示的灰階。S1~S6 表示 source channel,“+”表示 source 輸出的電壓大于 VCOM,是正極性,“-”表示 source 輸出的電壓小于 VCOM,是負極性。正負相同的壓差,理論上應該顯示相同的灰階,但是液晶分子的轉向卻完全相反,這樣就可以避免當液晶分子轉向一直固定在一個方向時所造成的特性破壞。但是假如 common 電壓有一點誤差,這時正、負極性的同一灰階電壓便會有差別,灰階的感覺也會不同。這樣對 FRC 的效果也會有影響。

3 FRC 效果分析

3.1 原有 FRC 效果分析

圖 5 列出了 dual-gate 的 TFT panel 中,source 和 gate 的連接,反映了 2-dot inversion 的掃描方式和 FRC 算法。子像素交替連接到 2 個 gate。

采用傳統的 FRC 算法,顯示會有周期性的豎線,在 4n+2(低 2 bit 為 01)尤其明顯。通過分析,發現存在這種現象的原因是沒有考慮到dual-gate 的特性和極性翻轉方式,以及 P/N 正負電壓顯示的不平衡。

圖 6 中,“P”代表正極性,“N”代表負極性,“+”代表高 6 位加 1。

從一幀內來看,R 存在 2 列 P/N+, 2 列 N/P+,每 2 行一個循環。B 存在 2 列 N+/P, 兩列 P/N+, 每兩行一個循環。G 存在兩列 N/P+, 兩列 P/N+,每兩行一個循環。這樣每兩列之間存在一個周期性的豎線。從兩幀來看,第二幀的豎線出現在同樣的位置。這樣加強了豎線的效果。

可以看出無論時間上還是空間上,四列像素都存在周期性變化,尤其是子像素,存在兩列 P/N+,兩列 N/P+ 這樣的周期性循環。而 P/N+ 和 N/P+ 在極性不對稱的情況下,透光率不同,導致屏幕有周期性豎條紋。

圖 7 是 4n+1(低兩 bit 為 01)的灰階,配合 source 極性的 FRC 算法圖形。可以看出,也存在周期性的豎條紋,但是因為豎線 +1 的像素只有 1/4, 導致豎條紋不明顯。這個和實際測試結果也是相符合的。

4n+3 (低兩 bit 為 11)的灰階效果和 4n+1(低兩 bit 為 01)的灰階的效果相似。所以我們重點解決的問題是 4n+2 時候的 FRC 算法問題。

3.2 改進 FRC 效果分析

要消除傳統 FRC 算法在 Dual-Gate 屏顯示時導致的豎條紋,就需要使豎線不在同樣的位置疊加,色塊要平均。考慮這種正負source 極性的不平衡,基于 2-dot inversion,得出能在每個子像素平衡的算法。發現基于不同的算法圖形,有很多種算法都能消除豎線,實現色塊的平衡。而下面的算法就是最小的矩陣單元,也是最簡單的可以實現 FRC 效果改進的算法。這個矩陣算法是針對 4n+2(低兩位為 10)的 FRC 算法。

圖 8 改進的低兩位為 10 的 FRC 算法。

時間上的抖動使用 2 幀循環的算法周期,空間上的抖動使用 2×2 的像素矩陣的算法單元。采用子像素的算法圖形,R/B 的算法圖形和 G 的算法圖形是列錯開的。

圖 9 中,在一幀內,R、G、B 在橫,豎,斜線方向都是平衡的,既有 P、N,也有P+、N+。在幀與幀之間,色塊也是平衡的。這樣不會有周期性的豎線產生,也沒有橫線和斜線的產生。

首先是在 FPGA 上驗證這種算法。通過在 FPGA 上用下面的 FRC 算法實現 8 bit 的圖像源轉化為 6 bit像素數據作為輸入給芯片,關掉芯片內部的算法,這樣芯片的輸入就直接輸入給source driver,來達到驗證新的算法的目的。

FPGA 驗證通過上下屏分別顯示老算法和新算法效果的辦法,來對比驗證,發現新的算法確實能夠明顯的改善豎線。FPGA 驗證為我們對芯片的改版提供了信心。最后按照這個算法生產了芯片,在 4n+2 時,豎線效果消除了,達到了客戶滿意的效果,實現了芯片最后的成功量產。

4 結語

本文通過理論分析和實際驗證,指出了傳統 FRC 算法沒有考慮 daul-gate TFT-LCD 的連接方式和極性翻轉方式而出現的周期性豎線的原因,并且提出了改進的 FRC 算法,解決了這個問題。進一步提出了針對不同的屏幕,不同的翻轉方式,會有不同的 FRC 算法的觀點。總結出了 FRC 算法需要考慮以下 6 個方面。

(1)時間均勻性。亮灰階和暗灰階在循環幀內的比例是相同的。

(2)空間均勻性。亮灰階和暗灰階在空間內的比例是相同的。

(3)P、N 極性。source channel 的正負極性越對稱,FRC 效果越好。

(4)POL 翻轉方法。source channel 的極性翻轉方式影響算法圖形。

(5)空間規律性。明暗像素交替具有空間規律性。

(6)時間規律性。明暗像素交替具有時間規律性。

要達到好的顯示效果,算法應該遵循的一些guideline。

(1)RB 算法和 G 算法最好錯開。

(2)算法循環的幀數在考慮時間混色平衡的基礎上,越小越好。

(3)算法圖像的矩陣在考慮空間混色平衡的基礎上,越小越好。

-

TFT-LCD

+關注

關注

13文章

151瀏覽量

31772 -

集成電路設計

+關注

關注

4文章

45瀏覽量

17697

原文標題:Dual-Gate TFT-LCD 抖動算法FRC 研究與實現

文章出處:【微信號:appic-cn,微信公眾號:集成電路應用雜志】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FRC算法具體需要考慮的因素總結

FRC算法具體需要考慮的因素總結

評論