前面主要介紹了Optimize的一些基本概念,那么今天就來講解一下它的一些實際運用,以及我們怎么才能用好這個強大的命令!!

說到Optimize,那和它聯系最緊密的就是Timing了。在做實際design中,從place到signoff,Timing violation是伴隨著整個流程揮之不去的陰影。那P&R中,Timing violation的趨勢是怎么樣的呢?

很多人腦海里浮現的是左邊呈倒金字塔形的這張吧,認為每前進一步就會修掉一些violation。其實則不然,右邊那張才是更合理化的趨勢圖。工具P&R的核心,placement和routing,其實都不是那么的timing aware。Routing以后甚至會出現violation path的增多(因為Route之前都不care DRC)。那其實整個Timing closure的過程中,出力最大的就是Optimize。因此,我們非常有必要來了解一些傳統的Optimize的注意點

1Before Optimize

正所謂"臨陣磨槍,不亮也光",Optimize可是個超級命令,通常運行時間都在幾個小時,甚至幾十個小時以上。耗費這么大的財力物力,我們可不希望它跑得毫無價值。在開始運行place_opt之前,對design的基本情況進行一些基本檢查真的是非常有必要的。整理了一下,以下幾點是比較有用的:

1)跑一遍check_design,檢查一下design中包括(netlist,Timing library,Floorplan)

2)檢查sdc文件是否clean。是否有一些定義不合理的約束。

3)報一遍zero wireload model的timing,如果zwl timing的結果都不理想的話,試著要去調整下sdc文件等等

4)采用get_attribute [get_lib_cell *] dont_use或者report_dont_use報出當前設計中的dont use cell,一些特別weak的cell我們需要禁用。

5)檢查一下有沒有打開需要的active scenarios

set_scenario_status

6)檢查所需要的Optimize mode。

Performance(opt.timing.effort)

Power(opt.power.effort)

Density(-max_density)

2During Optimize

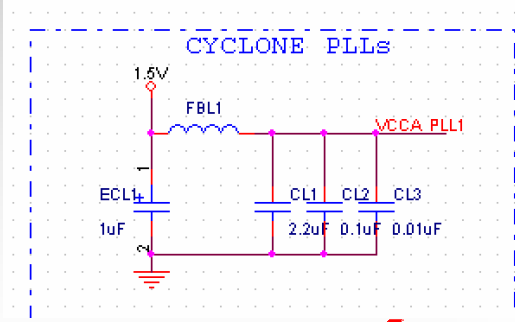

這個期間,是Optimize自己后臺運行的過程。我們也做不了什么操作,正好來復習一下Optimize的transform。我們知道它可以做很多的動作,而工具中可以讓它操作的object又有很多,這兩者之間的關系在下面這張表中可以體現出來:

3After Optimize

當Optmize做完,結果不理想該腫么辦呢?

Debug唄~~

提供以下幾點建議:

1)從log入手:

1.查看下各個Path Group的WNS/TNS的收斂趨勢。

2.查看下DRV的收斂趨勢。

3.查看下Optimize過程中各個transform的detail report。包括move的instance數目,距離。包括routing conestion等等,檢查下有沒有異常值。

2)分析Timing情況

1. 總體概括性地檢查一下critical path,而不是去看最差的一條,通常Path Group的timing變差具有共性

2. 分析一下path上的cell/net delay, 看看有沒有“bad buffering,bad sizing,weak cell”這些情況

3. 檢查一下Placement結果吧,看看某些區域的density是不是較大,可以采用keepout margin或者cell spacing constraint來增大cell之間的距離

4. macro是否擺放不合理,channel留太少,或者macro上的routing過差,可以采用添加合適的blockage,或者重新擺放macro位置來解決

5. 可以自己創建Path Group來優化timing,Optimize默認創建的Path Group是reg2reg, reg2cgate. 我們可以采用group_path來自己創建需要重點優化的Path。

3)通過report相關的命令來檢查一些潛在的誤操作或者工具的bug

report_dont_use可以報出當前design中的dont use cell

report_dont_touch可以報出當前design中的dont touch cell

4)運行incremental的optimize

它會基于當前Placement的結果來優化density,以及基于Optimize的結果來繼續優化WNS和TNS

optimize的介紹就到此為止了,看似簡單的一個命令其實要用好他卻不容易。如何挖掘工具潛能,取得較好的優化結果,這是一個反復迭代,反復分析設計的過程。總之,多嘗試,多跑跑設計,才能對工具愈發熟練。

-

design

+關注

關注

0文章

157瀏覽量

45714 -

timing

+關注

關注

0文章

7瀏覽量

10182

原文標題:芯片誠可貴,時序價更高——Optimize(二)

文章出處:【微信號:IC_Physical_Design,微信公眾號:數字后端IC芯片設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

介紹一下UPS的一些基礎知識

分享一些學習STM32的內容

關于stm32的一些簡單的介紹

Allegro中網絡表的導入以及回編到Capture中的一些

Verilog HDL語言組合邏輯設計方法以及QuartusII軟件的一些高級技巧

簡單介紹optimize的內容以及它的一些實際運用

簡單介紹optimize的內容以及它的一些實際運用

評論