諸如電信設備、存儲模塊、光學系統、網絡設備、服務器和基站等許多復雜系統都采用了 FPGA 和其他需要多個電壓軌的數字 IC,這些電壓軌必須以一個特定的順序進行啟動和停機操作,否則 IC 就會遭到損壞。

LTC2924 是一款簡單且緊湊的電源排序解決方案,采用16引腳SSOP 封裝(見圖1和圖2)。

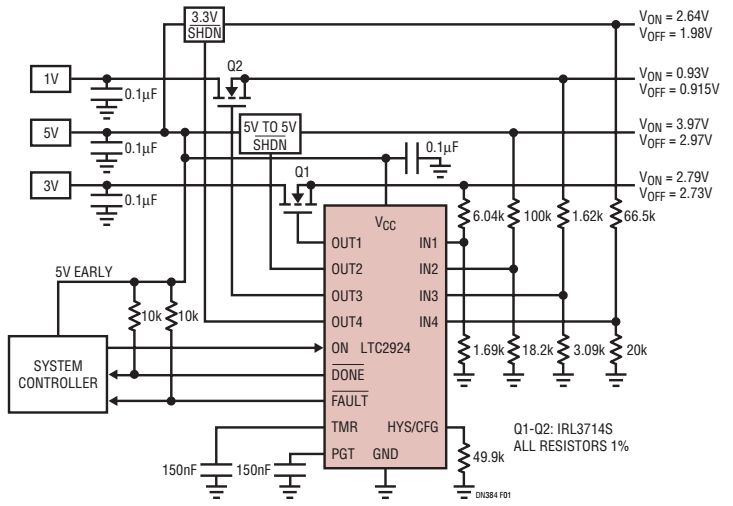

圖1: 采用外部 N 溝道 MOSFET 的典型應用

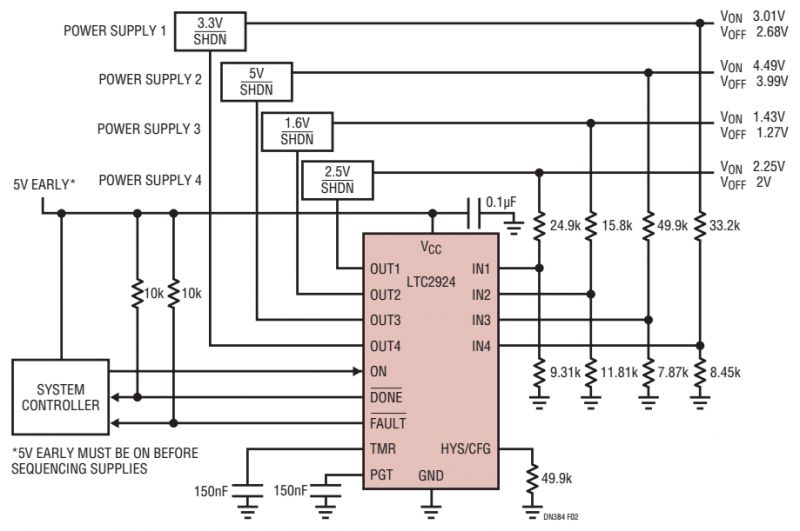

圖2: 采用停機引腳的 4 個電源排序器

采用單個 LTC2924 便可輕松完成 4 個電源的排序任務,而且,同樣可以很容易地把多個 LTC2924 級聯起來,用于對數目不限的電源進行排序。在允許功能度略有下降的情況下,利用單個 LTC2924 就能夠對 6 個電源進行排序。

LTC2924 通過輸出引腳(OUT1 至 OUT4)來控制 4 個電源的啟動和停機順序以及斜坡速率。每個 OUT 引腳采用了一個與內部充電泵相連的 10μA 電流源和一個與 GND 相連的低電阻開關。這種組合使得這些輸出擁有足夠的靈活性,以將其直接與多個電源停機引腳或外部 N 溝道MOSFET,開關相連。

LTC2924 通過 4 個輸入引腳(IN1 至 IN4)來監視每個被排序電源的輸出電壓。這些輸入采用精準比較器和一個經過修整的帶隙電壓基準來提供優于 1% 的準確度。4 個通道的上電和斷電電壓門限均采用阻性分壓器來設定。每個通道的上電門限和斷電門限可單獨地進行選擇。

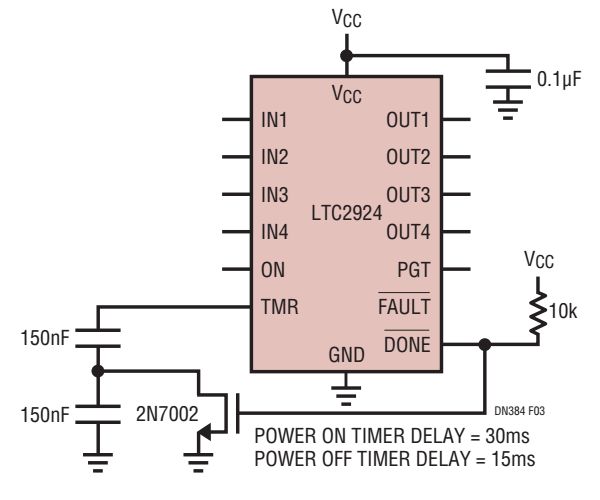

LTC2924 的定時器引腳(TMR)被用來在一個電源的啟動操作完成到下一個電源的啟動之間提供一個任選延遲。延遲時間通過在 TMR 引腳和地之間布設一個電容器來選擇(延遲=200ms/μF),而把 TMR 引腳浮置將去除任何延遲。啟動延遲與停機延遲可以不同。圖 3 示出了一種停機延遲為啟動延遲一半的簡單電路。

圖3: 設置不同的 ON/OFF 延遲

LTC2924 還包括一個電源良好定時器(PGT)。每當一個電源被使能時,LTC2924 將起動 PGT。如果任一個電源未能在分配的時間間隔之內達到其規定的標稱電壓,則檢測到一個上電故障。

結論

LTC2924 適合眾多的電源排序和監視應用。由于所需的外部元件極少并采用了 16 引腳窄式 SSOP 封裝,因此,基于 LTC2924 的電源排序解決方案占用的板級空間極小。

電源使能引腳無需設計師進行配置,但仍然具有足夠的通用性,能夠直接驅動停機引腳或外部 N 溝道 MOSFET。可簡單地通過增設一個電容器來實現電源的軟起動。如果需要對 4 個以上的電源進行排序,則可把多個 LTC2924 級聯起來,以對幾乎無限數量的電源進行排序。使 LTC2924 適合特定的應用無需借助軟件,而且,可在系統集成期間簡單地通過改變電阻值和電容值來對設計進行精調。由于設計簡單易行、元件成本低廉且占板面積小,因而使得 LTC2924 成為電源排序和監視用途的絕佳選擇。

-

電源排序

+關注

關注

0文章

9瀏覽量

7130 -

LTC2924

+關注

關注

0文章

3瀏覽量

6980

原文標題:如何防止系統受損?從電源排序入手

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

低噪聲解決方案助力設計安靜且緊湊的工業用電源

電源排序得以簡化

電路圖LTC3407是一款帶有集成電源開關的雙同步降壓DC / DC轉換器

四種FPGA 電源排序方案

關于電源排序的解決方案你了解嗎

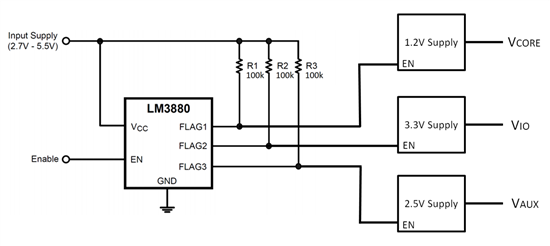

基于LM3880/LM3881的簡單6通道電源軌排序解決方案

一個簡單6通道電源軌排序解決方案說明

LTC2924一款簡單且緊湊的電源排序解決方案

LTC2924一款簡單且緊湊的電源排序解決方案

評論