今天咱來扒一扒工程設計中關于信號完整性的那點事,Bala一下工程設計中常遇到的5類典型問題。沒有因為這些糾結過的,應該還沒開始做SI設計。相信在一線摸爬滾打的工程獅看了會有共鳴!

第1類問題:必須依靠仿真的問題

有些問題,第一次設計時,如果不依靠仿真,沒什么好辦法知道到底行不行或者有沒有危險。舉一個常見的栗子:一拖多拓撲結構,這是一個出現概率很高的設計場景。假如有一個主控板,通 過背板(有些公司叫底板)拖6塊板卡,如果是第一次設計,那怎么評估這個方案行不行!靠設計規則?靠經驗法則?靠猜?那純粹是撞大運。當然有些人會說了,打一板試試就知道了。當然可以,但是像這種系統級的方案, 打板一次費用和周期都幾乎不可接受(當然土豪除外)。要提前評估方案的可行性,理論分析是少不了的,但這個問題僅靠理論分析搞不定。

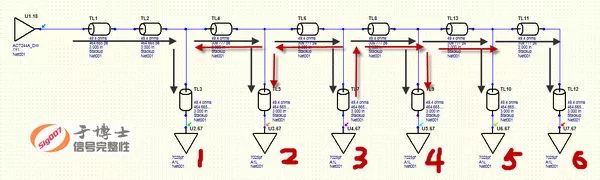

咱先從理論上看看這個拓撲中會發生什么。芯片的input buffer對信號來說通常表現出很高的阻抗,信號傳輸到接收芯片會發生反射。下圖中6個接收端都會有反射。反射回來的信號遇到走線 分叉會分別進入兩條岔路,比如從3反射回來的信號沿主干線向左右兩個方向傳輸,傳到1、2、4、5、6等接收器時再次發生反射。也就是3反射的信號會干擾其他芯片的接收信號。同樣的,其他任何一個接收器的反射信號都會 干擾別的接收器。反射過程會發生很多次,延時疊加,反復的反射震蕩,這是一個很復雜的過程,理論上簡單,但最終會疊加出來一個神馬東西?想不出來,得靠軟件。

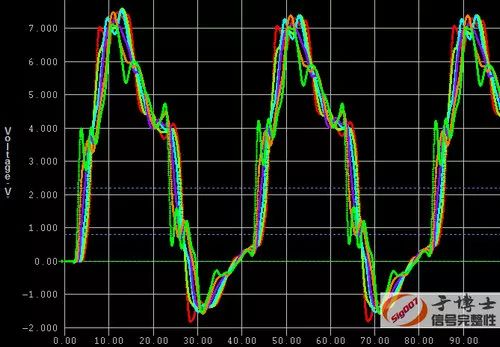

如果不做任何處理,波形長啥樣?簡單的仿真就能發現明顯的風險,見下圖,高低電平沖得太厲害了,有隱患。

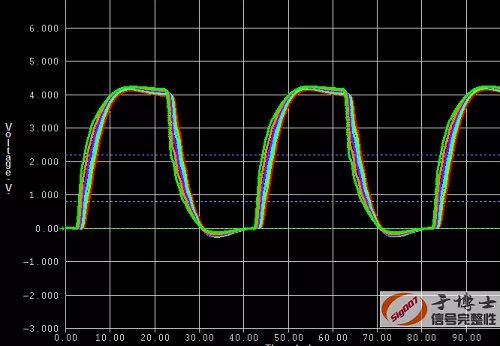

通過簡單的處理,消弱反射信號在各個接收器之間反復反射震蕩,我們可以把波形搞成這個樣子。這下放心多了。類似這種需要仿真的問題很多,通過仿真規避風險效果很好的。

第2類問題:無法仿真或很難仿真的問題

仿真是信號完整性設計很有效的手段。仿真軟件很神奇,迷倒了一大批工程師。

如果這個東西真這么簡單那就太好了,click、click、click...,OK,完活,多爽!

哪有如此美妙的世界!

過于依賴仿真,干活時候會經常遇到糾結痛苦的事。尤其把自己定位成仿真工程獅的,面對問題,有時候會無處下手,不知道該仿什么。真要遇到這種事,就該好好考慮一下了,有些事不是仿 真能搞定的,也許你遇到的是這第2類問題。

比如下面這個栗子,很酸爽,但絕對沒有糖炒的好吃。

有些單板上會有個別時鐘信號對抖動要求非常高,如果這個時鐘抖動大了,誤碼測試就不過關。高速串行接口對時鐘都是有要求的,我們看下典型接口信號抖動構成,時鐘信號的抖動對傳輸信 號的抖動貢獻是不能忽略的。那么問題來了,硬件人員把這個問題丟給你,怎么解決無所謂,硬件要的就是結果,搞定就行。那你怎么搞定這個事?靠仿真么?怎么仿?仿什么?

開工之前,分析一下那些因素會影響時鐘的抖動,先列張主要因素的清單:

1、反射(萬惡的反射,哪都有它)

2、串擾(萬惡的串擾,哪都有它)

3、模態轉換(有影響要注意)

4、參考平面(隱藏的雷區)

5、差分對設計(被很多人忽略的)

6、時鐘芯片的電源(重頭戲)

7、層疊結構安排走線層安排(一念之差的變數)

8、提供時鐘的晶振選型(硬件選型會慎重的,通常不用SI人員處理)

9、晶振電源的處理(不可忽略)

其他Layout相關的細節就不說了,單單上面提到的這些就夠仿真工程獅喝一壺的(整點二鍋頭還是伏特加?)。

好吧,仿真工程獅,仿真工程獅,咱開仿。打開神奇的軟件,然后呢,沒然后了........。往軟件里面塞什么內容讓它跑仿真?

那個什么,電源對抖動的影響,仿真腫么破?那個參考平面的影響,仿真腫么破?從仿真的角度來做頭疼是必然的。但是如果你換一個角色,以信號完整性設計工程師的角度去看會豁然開朗。 該仿真的仿真,仿不了的設計上控制一下不就可以搞(tou)定(lan)了。反正最終要的就一個結果,抖動降下來就OK。

黑貓白貓抓住耗子是好貓。好產品是設計出來的,不是仿出來的。不糾結,做好貓!

第3類問題:需要仿真但僅靠單一的仿真手段還不行

舉個典型栗子......。咳咳,又是栗子,夠了,被拍飛........。

好吧,鼻青臉腫的咱回來接著說。電源的磁珠濾波(又是萬惡的磁珠濾波),話說電源上用磁珠濾波那是比比皆是,話說這個磁珠濾波吃掉了多少硬件人員的加班時間,調試調試再調試,調試 到崩潰。咋能偷點懶呢?

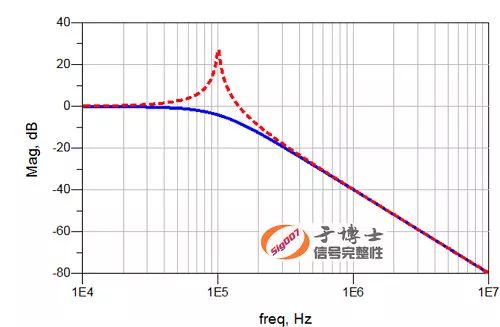

拿來神奇的仿真軟件,click、click、click... ... ...OK。三下五除二整出了下面這個漂亮的頻響曲線,藍色的那條是設計好的。怯怯地說一句,偷懶了,直接拷貝的老圖,沒重新做圖,直 接被拍飛........。

完工了?真的完工了嗎?呃,別高興太早,一大群邪惡的Bug正在排隊趕來準備挖坑呢。象下圖這樣,磁珠和電容后面拉出來的那條小尾巴,你把它放哪里?拉多長?

拉線太長了肯定不太好,地球人都知道。試想一下,如果這個小尾巴剛好通過電路板入口電源銅皮正上方會怎樣?

所以相鄰的平面層要考慮,如果你把它放在表層,那它下面緊鄰的平面層最好是GND。如果安排在內層呢?內層電源平面層往往被分割的很亂,如果這種磁珠濾波器用的比較多,那可能放不下 。平面層放不下就得放信號層,問題又來了,夾在上下兩個平面之間,而且旁邊會有其他信號線。這都是坑,要小心處理。

這個問題仿真能解決磁珠和電容的選型問題,規避那些坑就不能靠仿真了,只能Layout時,認真進行設計控制。

第4類問題:需要進行風險監控的細節問題

有句老話怎么說來著?魔鬼隱藏在細節中!對,是魔鬼,絕對是魔鬼!不少魔鬼會讓你不得不激情高昂的去加班去返工。

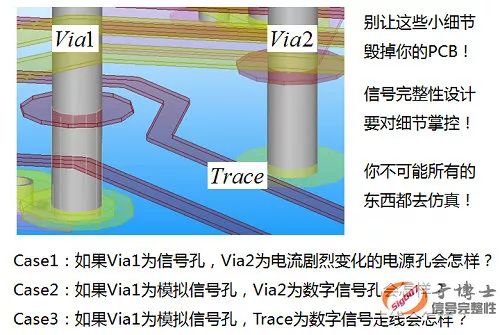

PCB是一個立體結構,不要總用平面思維去看待PCB。不羅嗦,上圖,自己看。俺課件中摘出來的圖片,話說每次講課這張圖我都會講好長時間。

第5類問題:需要Layout前整體規劃的問題

不羅羅索索的說教了,整的跟個唐僧似的招人煩,和老于一起重溫一下很久以前經歷的一件事。歷史上的某天,某君打來電話,給老于出了道難題,醬紫的......。

某君:于博士,我有塊板子要投板,有點不放心,想讓你看看行不行。

老于:啥情況,說說!

某君:板子上有10G差分接口,有DDR3。

老于:10G是單lane的還是接口的......。

某君:單lane。

老于:好,知道了,你繼續。

某君:我把10G差分對走在了靠近top的幾個內層,DDR3信號線走的是靠近bottom的內層。

老于:咋不把10G差分對放在靠bottom的內層?有風險,調一下走線層吧!

某君:差分對線寬線距定了,要調到下面幾層,阻抗沒法控制100歐......

老于:你DDR控制到40幾歐?

某君:是。

老于:和板廠溝通,重新定一個層疊就行了唄,這不費多少精力。

某君:層疊都定好了,不能改了。

老于:打下背鉆吧。

某君:BGA下的孔太小,怕不安全。

老于:... ...

好糾結的困局,這點事如果畫板子之前整體做個規劃,哪些信號走哪個信號層,哪個平面層放GND,哪個平面層放電源,也就沒這么糾結了。

本來沒坑,自己給自己挖了一個。

類似問題還有很多,別小看這個,整體規劃可以規避很多不必要的麻煩。

第6類問題

咱接著Bala,下面一個問題是......。啊......,又被拍飛........。

好吧,咱不Bala了還不行嗎,干活去......。誰拿了我的烙鐵......,快還給我......。誰也別攔著,今天我一定把這些球球兒都整下來......

-

芯片

+關注

關注

453文章

50417瀏覽量

421850 -

接收器

+關注

關注

14文章

2458瀏覽量

71800 -

信號完整性

+關注

關注

68文章

1397瀏覽量

95386

原文標題:信號完整性設計中的5類典型問題

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

工程設計中常遇到關于信號完整性的5類典型問題

信號完整性工程設計中常遇到的5類典型問題

信號完整性工程設計中常遇到的5類典型問題

評論