如果處理器和現(xiàn)場可編程門陣列FPGA全部由同樣的電壓供電運行,并且不需要排序和控制等特殊功能的話,會不會變的很簡單呢?不幸的是,大多數(shù)處理器和FPGA需要不同的電源電壓,啟動/關(guān)斷序列和不同類型的控制。

幸運的是,電源管理IC集成電路 (PMIC) 能夠控制目前的高級處理器、FPGA和系統(tǒng),并為它們供電,從而大為簡化了整個系統(tǒng)設(shè)計。

現(xiàn)在,你也許想知道哪一款PMIC可以為你的片上系統(tǒng) (SoC) 供電,還有就是要這么做的話,該從哪里入手。為你的SoC和系統(tǒng)選擇合適的電源解決方案是系統(tǒng)設(shè)計人員最常見的挑戰(zhàn)之一。所以,TI推出了數(shù)款全新工具,在使用我們的PMIC時,這些工具能夠簡化器件選型、評估和設(shè)計。

在這些工具中,有一些是TI Designs參考設(shè)計,它們可以幫助設(shè)計人員開始、驗證和加快設(shè)計。多個TI Designs已經(jīng)發(fā)布,給出了可由TI PMIC供電的很多不同SoC—以下是當前列表:

-

TIDA-00478使用TPS65218為Xilinx Zynq 7010供電。

-

TIDA-00551使用TPS65911 為Xilinx Zynq 7015供電。

-

TIDA-00604使用TPS65023為Altera Cyclone III供電。

-

TIDA-00605使用TPS65023為Altera Cyclone IV供電。

-

TIDA-00607使用TPS65218為Altera MAX 10供電。

-

TIDA-00621使用TPS65911。

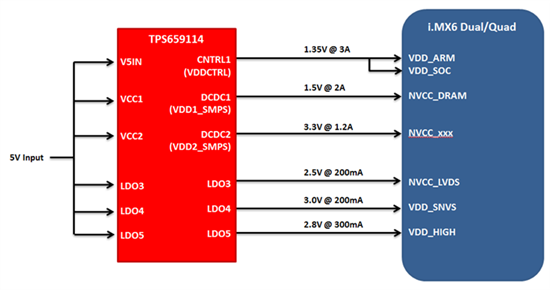

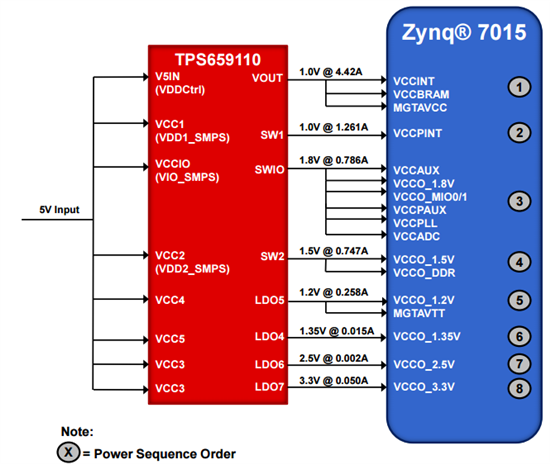

圖1是為ARM處理器供電的TPS65911的方框圖。與所有TI PMIC一樣,TPS65911非常靈活,并且可被用于數(shù)款器件。圖2顯示的是為Xilinx Zynq 7015 FPGA供電的TPS65911。

圖1:TPS65911的方框圖

圖2:為Xilinx Zynq 7015供電的TPS65911的方框圖

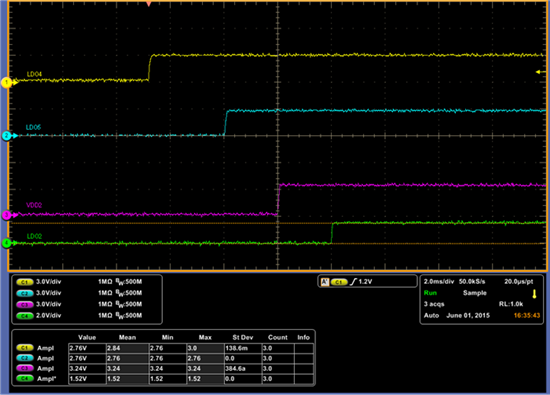

隨這些設(shè)計一同提供的還有電路原理圖、方框圖、印刷電路板 (PCB) 文件和測試結(jié)果。這些測試使得設(shè)計人員能夠評估他們正在嘗試用于特定SoC的PMIC的性能,并且為他們提供可以在他們自己的設(shè)計中使用的示例設(shè)計文件。測試結(jié)果包括啟動排序、負載瞬態(tài)、效率測試,以及圖3中顯示的其它內(nèi)容。

圖3:TPS65911的示例啟動時序

-

FPGA

+關(guān)注

關(guān)注

1626文章

21669瀏覽量

601869 -

電源管理

+關(guān)注

關(guān)注

115文章

6155瀏覽量

144238

發(fā)布評論請先 登錄

相關(guān)推薦

數(shù)字芯片設(shè)計驗證經(jīng)驗分享文章 實際案例說明用基于FPGA的原型來測試、驗證和確認IP——如何做到魚與熊掌兼

如何利用FPGA設(shè)計來驗證和加快你的設(shè)計過程

如何利用FPGA設(shè)計來驗證和加快你的設(shè)計過程

評論