大家好,到了每日學習的時候了。今天我們來聊一聊數字電路設計中的抖動。

既然說到了抖動,那么什么是抖動?那首先我們就來了解一下什么是抖動。

隨著通信系統中的時鐘速率邁入GHz級,抖動在數字設計領域中日益得到人們的重視。在高速系統中,時鐘或振蕩器波形的時序誤差會限制一個數字I/O接口的最大速率。不僅如此,它還會導致通信鏈路的誤碼率增大,甚至限制A/D轉換器的動態范圍。在此趨勢下,高速數字設備的設計師們也開始更多地關注時序因素。抖動反映的是兩個時鐘周期之間存在的差值,這個誤差是在時鐘發生器內部產生的,和晶振或者PLL內部電路有關。除此之外,還有一種由于周期內信號的占空比發生變化而引起的抖動,稱之為半周期抖動。總的來說,jitter可以認為在時鐘信號本身在傳輸過程中的一些偶然和不定的變化之總和。

************************************************************************************************************************

一、抖動的幾個重要概念

1. 抖動的基本概念

在理想情況下,一個頻率固定的完美的脈沖信號(以1MHz為例)的持續時間應該恰好是1us,每500ns有一個跳變沿。但不幸的是,這種信號并不存在。實際上,信號周期的長度總會有一定變化,從而導致下一個沿的到來時間不確定。這種不確定就是抖動。

抖動是對信號時域變化的測量結果,它從本質上描述了信號周期距離其理想值偏離了多少。在絕大多數文獻和規范中,時間抖動(jitter)被定義為高速串行信號邊沿到來時刻與理想時刻的偏差,所不同的是某些規范中將這種偏差中緩慢變化的成分稱為時間游走(wander),而將變化較快的成分定義為時間抖動(jitter Wander反映的主要是時鐘源隨著時間、溫度等的緩慢變化,影響的是時鐘或定時信號的絕對精度。在通信或者信號傳輸中,由于收發雙方都會采用一定的時鐘架構來進行時鐘的分配和同步,緩慢的時鐘漂移很容易被跟蹤上或補償掉,因此wander對于數字電路傳輸的誤碼率影響不大,高速數字電路測量中關心的主要是高頻的jitter。

2. 抖動的分類

抖動有兩種主要類型:確定性抖動和隨機性抖動。

確定性抖動是由可識別的干擾信號造成的,這種抖動通常幅度有限,具備特定的(而非隨機的)產生原因,而且不能進行統計分析。隨機抖動是指由較難預測的因素導致的時序變化。例如,能夠影響半導體晶體材料遷移率的溫度因素,就可能造成載子流的隨機變化。另外,半導體加工工藝的變化,例如摻雜密度不均,也可能造成抖動。

3. 抖動的測試方法

由于信號邊沿的時間偏差可能是由于各種因素造成的,有隨機的噪聲,還有確定性的干擾。所以對這個時間偏差通常是隨機的,而是有一定的統計分布,在不同的應用場合這個測量的結果可能是用有效值(RMS)衡量,也可能使用峰峰值(peak-peak)衡量,更復雜的場合還會對這個時間偏差的各個成分進行分解和估計。因此抖動的精確測量需要大量的樣本以及復雜的算法。

************************************************************************************************************************

二、抖動的測量方法

可以通過許多基本測量指標確定抖動的特點,基本的抖動參數包括:

1. 周期抖動(Period jitter)

測量實時波形中每個時鐘和數據的周期的寬度。這是最早最直接的一種測量抖動的方式。這一指標說明了時鐘信號每個周期的變化。

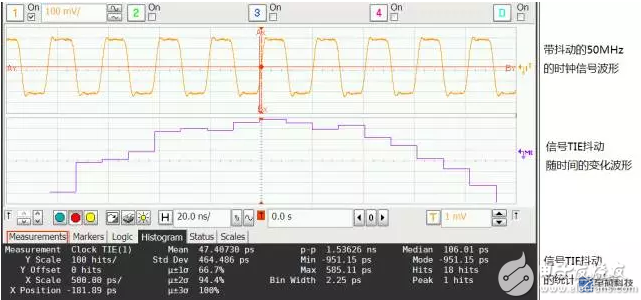

如圖為帶抖動的50MHz的時鐘信號進行周期抖動測量的結果,借助于相應的抖動分析軟件,觀察到信號周期隨時間的變化曲線,以及信號周期的最大值、最小值、周期變化的峰峰值、周期變化的方差等。

2. 周期到周期抖動(Cycle to Cycle jitter)

為了衡量時鐘信號相鄰周期的變化快慢,有時會用“周期到周期抖動”進行衡量,測量任意兩個相鄰時鐘或數據的周期寬度的變動有多大,通過對周期抖動應用一階差分運算,可以得到周期間抖動。這個指標在分析瑣相環性質的時候具有明顯的意義。

有些特殊的應用(比如針對DDR2/3的時鐘信號)還定義了N-cycle jitter,即相鄰N個時鐘周期的抖動變化。下圖是對同一個50MHz的時鐘波形進行Cycle-Cycle抖動測量和統計的結果。

3. 時間間隔誤差抖動(Time Interval Error)

所謂時間間隔誤差,是指被測信號邊沿相對于其參考時鐘有效邊沿的抖動。

測量時鐘或數據的每個活動邊沿與其理想位置有多大偏差,它使用參考時鐘或時鐘恢復提供理想的邊沿。TIE在通信系統中特別重要,因為他說明了周期抖動在各個時期的累計效應。

下圖是對同一個50MHz的時鐘信號進行TIE抖動的分析和統計結果。

************************************************************************************************************************

三、結論

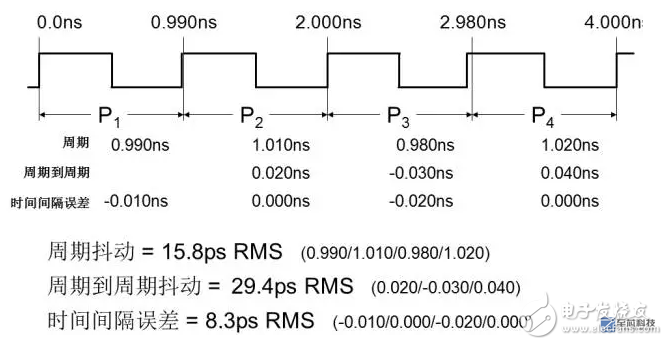

從前面舉的例子可以看到,對于同一個信號,用不同的方式進行測量和衡量,得到的結果可能是不一樣的。如圖所示,對于同一個帶抖動的時鐘信號,對其進行周期抖動測量、周期到周期抖動測量以及時間間隔誤差抖動測量,得到的結果可能是不一樣的。

因此,對于一個信號進行抖動測量之前需要先明確關注的抖動類型,否則測量結果的物理含義是不明確的。

對于更復雜的數字信號來說,除了關心其抖動的RMS值以及峰峰值以外,還會關心該抖動的不同組成成分,因為不同成分的抖動對于電路的影響是不一樣的,相應的應對手段也不一樣。比如很多高速總線都會對高速數字信號的隨機抖動成分(Random Jitter)、周期性抖動(Periodic Jitter)、ISI抖動(Inter-Symbol Interference jitter)等進行進一步的分解和研究。

抖動是數字信號,特別是高速數字信號非常重要的一個概念,越是高速的信號,其比特周期越短,對于抖動的要求就越嚴格。

今天就聊到這里,各位,加油!

-

數字電路

+關注

關注

193文章

1600瀏覽量

80502 -

高速信號

+關注

關注

1文章

222瀏覽量

17677

發布評論請先 登錄

相關推薦

簡談數字電路設計中的抖動

基于LabVIEW的數字電路設計和仿真

高速數字電路設計

數字電路設計的信號完整性問題探討

FPGA CPLD數字電路設計經驗分享.

簡談數字電路設計中的抖動

簡談數字電路設計中的抖動

評論