自1985年首款FPGA誕生以來,FPGA已經是一名在電子信息領域征戰了30年的老兵,這名戰功赫赫的老兵如今已經正式開赴了一個新的戰場。但是FPGA并不是萬能的。相對于串行結構處理器,其設計的靈活性是以工作量的增加為代價的。FPGA與ARM、DSP(如下圖所示)的比較如下。

一、從語言本身的差異來看,基于Verilog HDL和VHDL的硬件語言與C/C++相比,在代碼靈活性、開發效率等方面還有較大差距。通常一段十幾行的C語言代碼使用硬件語言實現后,代碼量會增加到幾十行之多。同時,在進行硬件語言描述時,一個合格的FPGA工程師不僅要實現相應的邏輯功能,還要在頭腦里浮現編寫的代碼所生成的邏輯結構,并考慮到門延時對系統時序的影響。這樣才能夠設計出穩定高效的邏輯結構,減少后期時序調整的工作。

二、從語言本身的差異來看,基于Verilog HDL和VHDL的硬件語言與C/C++相比,在代碼靈活性、開發效率等方面還有較大差距。通常一段十幾行的C語言代碼使用硬件語言實現后,代碼量會增加到幾十行之多。同時,在進行硬件語言描述時,一個合格的FPGA工程師不僅要實現相應的邏輯功能,還要在頭腦里浮現編寫的代碼所生成的邏輯結構,并考慮到門延時對系統時序的影響。這樣才能夠設計出穩定高效的邏輯結構,減少后期時序調整的工作。

三、從工作頻率來看,ARM、DSP等處理器采用的是成熟的內核結構,具有較好的時序特性,其最高頻率通常為600MHz~1.25GHz。為提高處理能力,TI等芯片廠商采用多核的設計方式,設計了具有8核DSP、8核ARM的處理器,每個核心的最大工作頻率可 達1.25GHz,通過設置可以開啟和關閉其中的內核來靈活地協調功耗與處理能力之間的矛盾。目前TI公司正在設計具有8核ARM+8核DSP的處理器,來滿足高速系統中集中運算的需求。而在FPGA的設計中,不同的系統具有不同的最高工作頻率,該頻率可以在編譯報告中獲得。對于Altera公司的FPGA,通過TimeQuest工具調整時序,可以提升設計工程的最高頻率。一個具有良好設計的FPGA工程的最高頻率可達150MHz以上。

四、從執行方式來看,基于嵌入式平臺的C/C++語言在已有的硬件結構中執行,只需正確配置相關寄存器即可。而使用硬件語言的設計需自行設計硬件結構,在生成結構前還要經過前仿真、綜合、布局布線、后仿真等步驟,開發周期較長。這一情況在較為復雜的FPGA工程設計中尤為嚴重。例如,一個添加了4個DDR2的IP的工程在i5處理器、4G內存的計算機上,編譯時間甚至在20min以上。

五、從算法應用來看,ARM、DSP等處理器中集成了加法器、乘法器等運算單元,尤其是在DSP中,可以在一個周期內進行8×8位甚至16×16位的乘法運算。同時,這些處理器還支持浮點運算能力。而FPGA對這部分運算并不擅長,即使在較為簡單的加法運算中,若進行加法的兩個數據具有較高的位寬,由于傳統的加法中的進位方式是串行結構,所以在其生成的結構中會產生較長的門延時,從而會降低時序的余量,甚至會降低系統編譯后的最高工作頻率。

六、從算法設計來看,在ARM、DSP等處理器中設計算法前,需要提前構思算法的流程圖,然后進行代碼的編寫。而在FPGA設計中,主要包含三種設計方式:面向狀態的設計,面向活動的設計和面向結構的設計。

(1)面向狀態的設計是以狀態機為代表的設計方式,即通過控制信號和時序信號觸發狀態機進行狀態的遷移。狀態機的設計是FPGA開發中必不可少的環節,這部分內容將 在7.2.2節中詳細敘述。

(2)面向活動的設計是以數據流和流程圖為代表的設計方式。尤其是在傳輸系統、實時算法設計中,常使用基于數據流的設計方式。常見的數據流的操作方式包括數據的寄存器同步緩沖、數據傳遞、數據運算與流水設計、數據的存取等。

(3)面向結構的設計常用于較大的系統設計中,用于描述模塊與模塊、單元與單元之間的互聯關系,主要包括數據信號與控制信號。根據不同的層次描述,主要可以分為系統級結構描述、寄存器級結構描述、門級結構描述等。

為了解決這些硬件工程師所面臨的問題,Altera Xilinx等FPGA公司不遺余力地對開發平臺進行了完善,如下以Altera的解決方案為例。

對于第一點提及的設計語言的問題,Altera推出了Qsys(SOPC)等片上軟核,使工程師在FPGA中同樣可以使用更為靈活的C語言進行編程。Qsys(SOPC)中包含了片內、片外存儲器、定時器及各種接口等IP,使工程師可以按需定制自己的片內處理器。使用這種方式,在一定程度上緩解了硬件描述語言開發周期過長的缺點,也成為一種對FPGA系統進行前期功能驗證的有效手段。

對于第二點提及的通用模塊或接口占用開發周期的問題,Altera和供應商設計了大量具有知識產權的IP(Intellectual Property,知識產權),包括運算類、通信類、數字信號處理類、門類、輸入/輸出類、接口類、JTAG擴展類、存儲類等多種類別。這些IP是經過嚴格測試和優化過的,其中部分IP免費,上面提到的SOPC中應用的大部分IP都是免費的。

值得注意的是,盡管大部分基本功能的IP可以在不同系列的FPGA間通用,依然有一些IP并不支持所有系列的FPGA,使用這些IP在不同系列的FPGA間進行工程移植時需要注意。所使用的IP是否支持當前芯片,可以在Quartus II的MegWizard管理器中查閱,也可以在官網中查閱。Altera支持的所有IP及其適用系列可參考以下網址:http://www. altera.com.cn/products/ip/ip-index.jsp。

對于第三點提到的工作頻率的問題,不同的處理器具有不同的應用領域。在高速數據處理過程中,ARM、DSP等固然可達到較高的工作頻率,然而相對于FPGA,其高速的優勢僅體現在串行結構的算法中。在FPGA的設計中,可利用其硬件設計的靈活性,采用并行算法或將串行算法改造為并行算法,然后在FPGA中實現。經測試,在工作頻率為1GHz的DSP中(TMS320C6416),對SDRAM中分辨率為2048×2048的圖像進行中值濾波后重新寫入SDRAM,耗時為7s;而在FPGA中,完全可以在圖像輸入時進行實時處理,僅消耗幾個時鐘周期的處理,近似可認為0延時—實時。

對于第四點提及的編譯時間過長的問題,Altera致力于開發新版本的平臺,提升編譯效率的同時,增加了增量編譯的功能。配合區域鎖定,可以鎖定已編譯過且在后續修改中沒有改動過的模塊,對這部分模塊不進行重新編譯,從而可減少編譯時間。

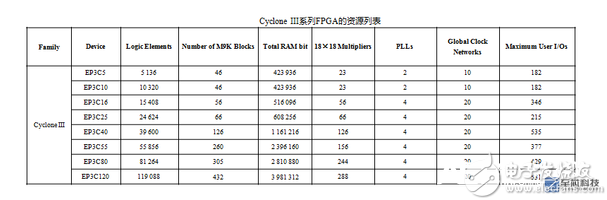

對于第五點提及的運算能力的問題,Altera FPGA中內嵌了多個DSP塊。每個DSP塊中包含加法器和乘法器結構,根據系列不同,具有不同的數據位寬。多個DSP塊中的加法器和乘法器可以互相拼接,從而支持更高位寬的運算。結合相關的運算類IP,可以流水線的形式完成運算,每個周期輸出一次計算結果。表1.10為Cyclone III系列FPGA的資源列表。可以看到,與DSP相比,Cyclone III的乘法器資源還是比較豐富的,這使得在FPGA內部進行并行運算成為可能。

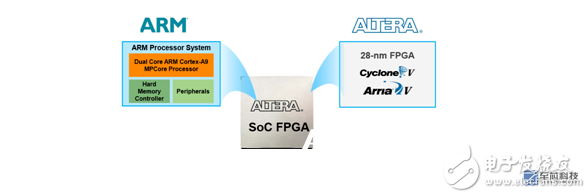

最后,Altera又推出了嵌入了雙核28nm的ARM Cortex-A9的FPGA,同時以足夠的DSP塊和足夠的乘法器資源,完善了FPGA+DSP+ARM架構,并以單片SoC FPGA的模式,解決了過往FPGA力所不能及的缺陷,解決了未來多IC集成的前瞻性問題,如圖1.28所示。而這卻僅僅只是一個開始,在未來Altera FPGA的發展中,更多的以實現FPGA+DSP+ARM為架構,并行實現高速運算,解決過去的難題,不斷地突破極限。在未來的數字系統設計中,這必然是一種趨勢。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602023 -

時序

+關注

關注

5文章

386瀏覽量

37290

發布評論請先 登錄

相關推薦

對比ARM、DSP,深入了解FPGA

對比ARM、DSP,深入了解FPGA

評論