目前市場上有幾百種關于信號完整性和降噪的書。如果你是個新手或者需要一個進修課程,你可以考慮閱讀Douglas Brooks編寫的“信號完整性問題和PCB設計”。如果需要進行更深入的探討,可以閱讀Howard Johnson編寫的“高速數字設計”。

FPGA可能會由于太多的高速SSO而對系統中的信號(或其它FPGA信號)帶來嚴重破壞,因為這會導致稱為同時切換噪聲(SSN)的噪聲。SSN也叫做地反彈或VCC反彈,對于單端標準,SSN是在輸出由低到高時提供瞬態電流和由高到低時吸收瞬態電流的過程中,由多個輸出驅動器同時切換和導致器件電壓與系統電壓之間的變化而引起的。

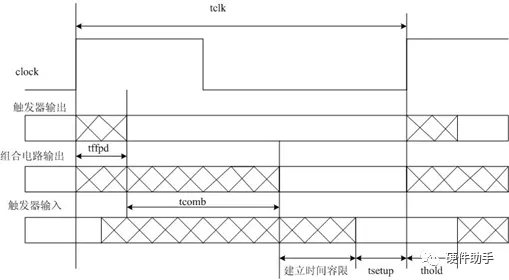

在高到低的轉換引起地反彈時,由低到高轉換也會導致VCC下降。由于電容通常安放在VCC和接地層之間,因此SSN典型地存在于這兩個地方。由低到高轉變時地反彈也有可能出現。 于是,SSO變成了干擾信號,它會產生可能耦合到鄰近信號的噪聲。對于某個區域而言太多SSO可能會導致電源的擾動。由于以下2個原因,SSO已經變成一個必須認真對待的問題:1. 切換時間大幅下降;2. 過孔尺寸和走線寬度的減小加上更大的板厚度已經推高了板極電感,這將大幅增加出現地反彈的可能性。更大的負載電容也可能導致SSN,雖然程度上會輕一點。當有效VCC低于期望值,從而導致I/O緩存的轉換速度低于期望速度時,SSN也可能導致時序問題變得突出起來。

有幾個方法可以減小SSN。有些器件只需通過限制I/O標準的選擇就可簡化這個問題,但不是所有器件都能這么做。一些供應商建議將高速總線輸出分布到整個裸片上,如果SSN是你唯一關注的問題,那么這絕對是一個很好的建議。不過,如果按照這個建議去做,有2個基本問題將會冒出來。

首先,這可能會帶來下游布通性問題,因為將信號散布到整個裸片上經常會引起更多的走線交叉。而這就導致需要更多的信號布線層。其次,大多數設計在散布信號前也要求進行仔細研究,因為當一個總線散布到特定的塊或區外時會引起塊/區間的兼容性問題。因此,如果你能在考慮布通性的同時,小心地將一個較小的總線分布到一個或兩個塊/區域內,那么系統將會工作得很好。

如果你被一個具有相鄰高速切換輸出的設計所困擾,有好幾種技術能幫助你解決潛在的SSN問題。首先對你的設計進行合適的布局和去耦合。對于去耦合,使用距離盡可能近的電源和地平面對,中間用一個SMT電容隔開。使用SMT電容進行去耦合也有助于減小電感,而電感是產生系統噪聲的一個主要因素。

如果你仍然覺得需要使用去耦電容(為了減小SSN),應該使得這些電容的位置盡可能靠近高速輸出引腳。Altera的一項研究發現,如果這些電容到引腳的距離大于1英寸,在使用適當的SMT電容去退耦時,這些電容變得效率極低。其他減小SSN或者其可能產生影響的建議包括:避免將敏感信號(復位、時鐘和使能等)位于SSO附近;可能時,使用較小偏移的輸出和使用最低電感的過孔;通過在合適位置插入延時使得輸出信號交替出現。即使已經完成了PCB的生產,這個建議仍然可以應用。

參考將被連接到FPGA上的器件的相關資料。對于每個器件,確定最大輸入低電壓門限(單位毫伏)。這是FPGA驅動該器件需要的最大電壓,所以該設備仍然可以檢測到一個有效邏輯低狀態(最大VIL值)。同樣,還要確定器件可以容忍且能繼續工作的最大輸入負脈沖信號(單位毫伏)。

在某些情況下,最大容許的地反彈可能不是或者不僅是以上給出的值。而是要通過獲得最大輸入低電壓門限的最小值、最大輸入負脈沖信號、或者所有器件的最大地反彈來確定最大的系統地反彈。

然后,根據具有相似負載特點的網絡連接的數目和種類對類似的FPGA總線進行分組。接著研究每個部分、區域或者塊的電源和接地引腳數目,還有對于所使用的每個I/O標準,每個電源和接地管腳對所允許的SSO數目。這些數目可以用于計算每個組的總電容負載和每個輸出驅動的電容,以確定可以容忍的SSO最大值。

你也應該咨詢供應商以確定基于每個塊和每一對塊你是否超過了推薦的SSO數目,前提是供應商已經研究了這些問題。同時,因為有多個因素會導致SSN,所以最好建立一個具有內置抗噪聲性能的魯棒系統。否則,就使用針對每個引腳限制I/O標準的器件,這樣就可以減少可能的SSN問題。

差分信

在FPGA設計中,你可能會發現對差分信號的處理存在最多的爭議。類似于SSN,最好從供應商、書籍和用戶群獲得盡可能多的信息。同時,在確定某個方案前咨詢你的布局部門以了解他們推薦的建議和信息。

主要爭論開始于差分信號對是否應該采用寬邊耦合還是邊緣耦合,以及每對之間到底應該存在多少耦合。答案通常是“根據具體情況確定”,所以需要進行具體研究。

如果你不能確定對于一個單端信號為什么需要選擇差分I/O標準,答案很簡單。使用差分信號,你幾乎可以完全控制信號的回路。因為這是信號對的一部分,而且理論上在任何一個接地(或者電源)平面上不應該出現來自信號對的電流。

這里假設走線對具有相等長度,布設在相鄰區域且間距不變,走線阻抗恒定且匹配。此外,利用單端信號,你很難控制信號回程,而且測試一個信號的返回也可能徒勞無益。

差分信號的主要缺點是他們需要兩根走線彼此臨近。當在一個PCB上分配幾百個差分信號時這可能是個難點。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601828 -

pcb

+關注

關注

4317文章

23004瀏覽量

396250

發布評論請先 登錄

相關推薦

PCB信號完整性分析入門

分享FPGA設計中信號完整性需要注意的幾個方面

分享FPGA設計中信號完整性需要注意的幾個方面

評論