很多計算機專業(yè)的學(xué)生都只是在理論層次學(xué)習(xí)計算機體系結(jié)構(gòu)方面的知識,比如數(shù)據(jù)路徑、控制結(jié)構(gòu)和存儲系統(tǒng)等,但是如何將這些組合起來則完全靠學(xué)生的想象力。MIPSfpga的出現(xiàn)讓這一切迎刃而解,它不同于其他課程的地方在于首次采用了一款純粹的商用軟核CPU用于研究目的,用戶可以在此課程的系統(tǒng)集成環(huán)境下詳細、深入的探索計算機架構(gòu)。

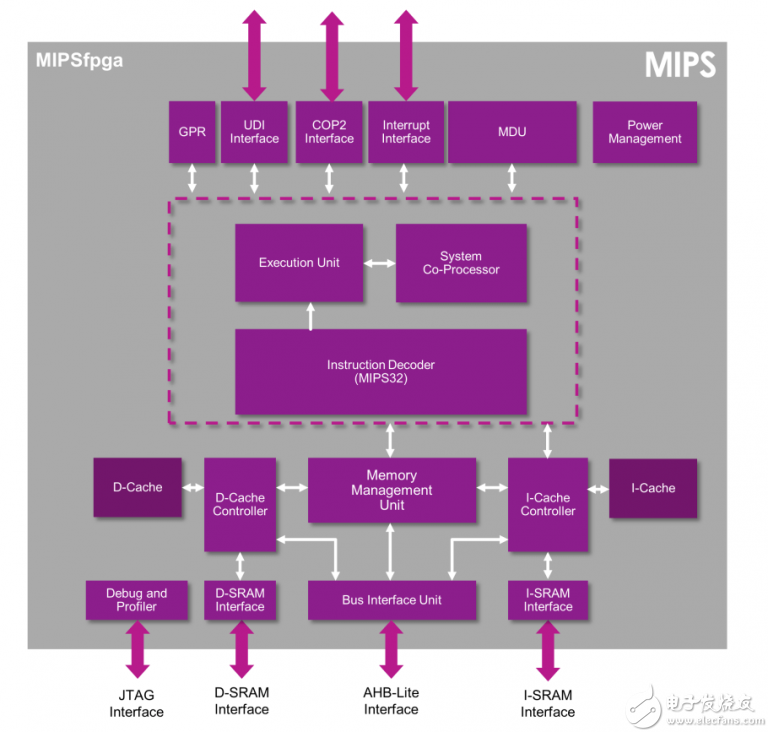

MIPSfpga使用一款MIPS系列軟核IP——具體來講是microAptiv核,PIC32MK處理器采用的既是此款軟核。該核面向的是可編程邏輯門陣列(FPGA)。Imagination公司除了授權(quán)可以使用這款實用的MIPS軟核處理器外,還準備了一系列的教學(xué)材料,從而可以使用戶快速入門、開發(fā),進而能夠修改該處理器和系統(tǒng)。

該課程提供了三部分材料引導(dǎo)用戶入門、使用和修改MIPSfpag:入門指南、實驗實例和SoC資料包。

第一部分材料包括MIPSfpga用到的Verilog設(shè)計文件和一些介紹MIPSfpga系統(tǒng)和使用方法的文檔。

第二部分材料(MIPSfpga實驗實例)包含25個需要動手操作的實驗,指導(dǎo)用戶如何學(xué)習(xí)計算機架構(gòu)和進行系統(tǒng)級的設(shè)計。比如,修改MIPSfpga系統(tǒng)與外設(shè)(如LCDs、傳感器等)的接口、使用性能計數(shù)器和中斷、改變緩存刷新策略、添加新的指令并且測量這些改變所帶來的性能差異等。由于使用的商用編譯器能夠清晰的看到因架構(gòu)或系統(tǒng)的修改帶來的性能改變,也幫助用戶在此方面的能力上得到較快的提升。

第三部分材料是MIPSfpga SoC,它向用戶展示了如何基于MIPSfpga搭建片上系統(tǒng)(SoC)并且移植開源的Linux操作系統(tǒng)。

最新的MIPSfpga v2.0在2017年7月1日正式推出,在之前版本的基礎(chǔ)上又增加了更多的特性和資源,比如增加了16個動手實驗(即動手實驗的個數(shù)從9個增加到25個),可以采用UART(串口)將程序下載到MIPSfpga,精簡了啟動代碼,增加了Windows和Linux系統(tǒng)的安裝指令,同時提供了Verilog和VHDL語言的系統(tǒng)級模塊,支持快速調(diào)試通道(FDC)和用戶自定義接口(UDI),支持使用printf這樣的I/O指令并且允許用戶定義自己的系統(tǒng)指令。

自從2015年5月以來,全世界已經(jīng)有超過600所大學(xué)獲得了授權(quán)并且下載使用MIPSfpga相關(guān)的資料--軟核IP以及入門資料和實驗練習(xí)。

通過提供全面開放的商業(yè)CPU IP軟核和系統(tǒng), 指導(dǎo)用戶使用和修改處理器和系統(tǒng),MIPSfpga正在轉(zhuǎn)變計算機體系結(jié)構(gòu)的教育方式。當然不僅這些,MIPSfpga還提供了一個在研究和高級項目中探索計算機架構(gòu)特性和增強功能的平臺。

這里提供了一些高級項目的鏈接,它們都是基于MIPSfpga實現(xiàn)的。

MIPS由于其足夠簡單和精致,在計算機架構(gòu)教學(xué)中已經(jīng)非常流行。MIPSfpga提供了一個強大的平臺,將計算機架構(gòu)和系統(tǒng)設(shè)計的理論教學(xué)與實踐操作聯(lián)系起來,從而讓用戶更加全面的了解計算機架構(gòu)設(shè)計。

-

FPGA

+關(guān)注

關(guān)注

1620文章

21510瀏覽量

598919 -

mips

+關(guān)注

關(guān)注

1文章

237瀏覽量

47581 -

imagination

+關(guān)注

關(guān)注

1文章

562瀏覽量

61118

發(fā)布評論請先 登錄

相關(guān)推薦

基于國產(chǎn)異構(gòu)雙核(RISC-V+FPGA)處理器,AG32開發(fā)板開發(fā)資料

淺談國產(chǎn)異構(gòu)雙核RISC-V+FPGA處理器AG32VF407的優(yōu)勢和應(yīng)用場景

FPGA的IP軟核使用技巧

關(guān)于FPGA IP核

Achronix FPGA增加對Bluespec提供的基于Linux的RISC-V軟處理器的支持,以實現(xiàn)可擴展數(shù)據(jù)處理

Achronix與Bluespec聯(lián)合宣布推出一款支持Linux的RISC-V軟處理器

FPGA優(yōu)質(zhì)開源模塊-SRIO IP核的使用

FPGA實現(xiàn)基于Vivado的BRAM IP核的使用

FPGA新IP核學(xué)習(xí)的正確打開方式

新思科技重磅發(fā)布全新RISC-V處理器系列擴大ARC IP組合

新思科技重磅發(fā)布全新RISC-V處理器系列,進一步擴大ARC處理器IP組合

基于CPLD/FPGA的多串口擴展設(shè)計方案

設(shè)置AMD以太網(wǎng)IP核的Pause幀處理

MIPSfpga軟核處理器IP設(shè)計方案

MIPSfpga軟核處理器IP設(shè)計方案

評論