經過這幾年的市場磨礪,Zynq-7000 FPGA SoC器件平臺在開發者中的認知度和接受度越來越高,這種“ARM處理器+可編程邏輯”的創新架構,可以幫助開發者在設計中找到高性能與靈活性的完美平衡,對此大家也心知肚明。

但是在實際的應用中,想要玩轉Zynq這種“異構”平臺,并非信手拈來這樣簡單。其中很大的一個原因就是以往的開發工具都是彼此分立且松散連接的,設計和實現效率不高,因此需要一種全新的設計方法和開發工具來支持Zynq的應用開發。

Xilinx推出的Vivado設計套件恰好能夠滿足這一需求。Vivado是一種以IP和系統為中心、支持7系列以及更新系列器件的(包括7系列FPGA、Zynq-7000 AP SoC、UltraScale / UltraScale Plus FPGA、Zynq US+ MPSoC等)全新集成開發環境,可解決用戶在系統級集成和實現過程中常見的生產力瓶頸問題。Vivado目前最新的HLx版本可為設計團隊提供實現基于C的設計、重用優化、IP子系統復用、集成自動化以及設計收斂加速所需的工具和方法,結合UltraFast高層次生產力設計方法,可幫助設計人員以高層次抽象形式開展工作,加速高層次設計、驗證和實現。

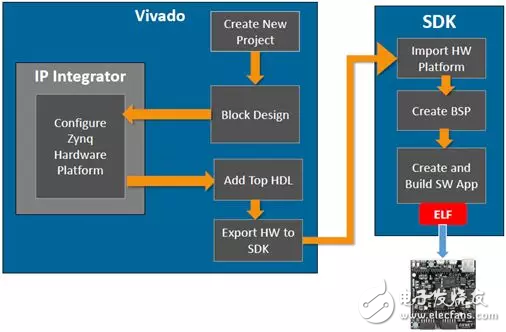

圖1,Zynq全可編程平臺設計開發流程

在近日舉辦的安富利MiniZed Speedway培訓活動中,一個重要的議程就是:如何幫助開發者使用Vivado設計套件創建一個符合用戶設計需求的Zynq-7000硬件平臺。

與傳統的處理器不同,Zynq平臺的處理器系統(PS)包含一系列常用的外設資源(如I2C、UART、CAN、GPIO、SPI、USB 2.0、Ethernet MAC、SDIO等)以及多端口DRAM Controller(可支持DDR2、DDR3/3L或LPDDR2顆粒組成一個16-bit或32-bit的存儲器系統)。而且,PS通過專用的端口可以直接和可編程邏輯(PL)進行通信和數據共享,使用PL可以創建用戶自定義IP,擴展PS的外設和處理能力。雖然說PS可以在沒有任何PL編程的情況下使用,但是為了充分利用PL中的軟IP資源,或者完成PS特定的外設與PL器件引腳間的連接布線,對PL的編程還是必要的。這也是Zynq平臺硬件設計不同于和優于傳統處理器的重要特征。

在為期一天的MiniZed Speedway培訓中,安富利講師詳細講解了Zynq-7000 SoC的系統架構,硬件開發的設計流程,核心的知識點包括:

Zynq-7000 SoC的架構

Xilinx嵌入式設計工具和設計流程

如何使用Vivado IPI配置PS、外設以及PS和PL之間的接口

如何使用Vivado IP Package創建一個用戶自定義IP

如何使用ILA和硬件管理器(Hardware Manger)調試用戶自定義IP

與此同時,安富利還為本次培訓精心準備了實操性的實驗環節,指導開發者完成硬件設計中的關鍵環節。例如:

創建一個基礎的Zynq設計項目

使用Vivado IP Integrator (IPI)配置PS

在Zynq設計中添加基于PL的外設

使用PS DMA優化PS和PL之間的數據流程

使用Vivado IP Packager創建一個用戶自定義IP

使用Vivado Hardware Manager調試基于PL的用戶自定義IP

可以看到,培訓中“手把手”地介紹了Zynq硬件平臺配置過程中Vivado的一些核心子工具的特性和使用方法,如Vivado IP集成器(IPI)。IPI可提供圖形化的基于Tcl、自動連線、自動檢查和糾正錯誤(correct-by-construction)的開發流程,可提供具有器件和平臺意識的互動環境,能支持關鍵IP接口的智能自動連接、一鍵式IP子系統生成、實時DRC等功能,此外還提供強大的調試功能。在IP之間建立連接時,設計人員工作在“接口(Interface)”而不是“信號(Signal)”的抽象層面上,能充分利用IP資源快速組裝復雜系統,從而大幅提高了生產力。通過利用Vivado中IPI和HLS(高層次綜合)工具的完美組合,客戶的開發效率相對于傳統的RTL方式可提高數倍之多。

總之,按照MiniZed Speedway培訓展示的“套路”,熟悉了Vivado這樣高效的設計工具,掌握了系統的設計方法,釋放出Zynq全可編程平臺的硬件潛能,并非難事!

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601843 -

Zynq

+關注

關注

9文章

608瀏覽量

47126

發布評論請先 登錄

相關推薦

一文教你如何玩轉Zynq平臺

一文教你如何玩轉Zynq平臺

評論