大量設備都使用數/模轉換器(DAC)來實現各種各樣的功能。高精度、電壓輸出DAC的常見應用有儀器儀表、自動測試以及測試/測量設備。在這些應用中,DAC產生直流電壓或任意波形。

對于這些電路,使用電壓輸出DAC進行設計的最具挑戰的部分就是真實了解這種怪獸在其規定精度范圍之內到底能夠跑多快。如果某款設備的時鐘頻率為50MHz,那么就電壓輸出更新速度來說,這意味著什么?或者,除了知道時鐘頻率之外,還需要更多信息嗎?

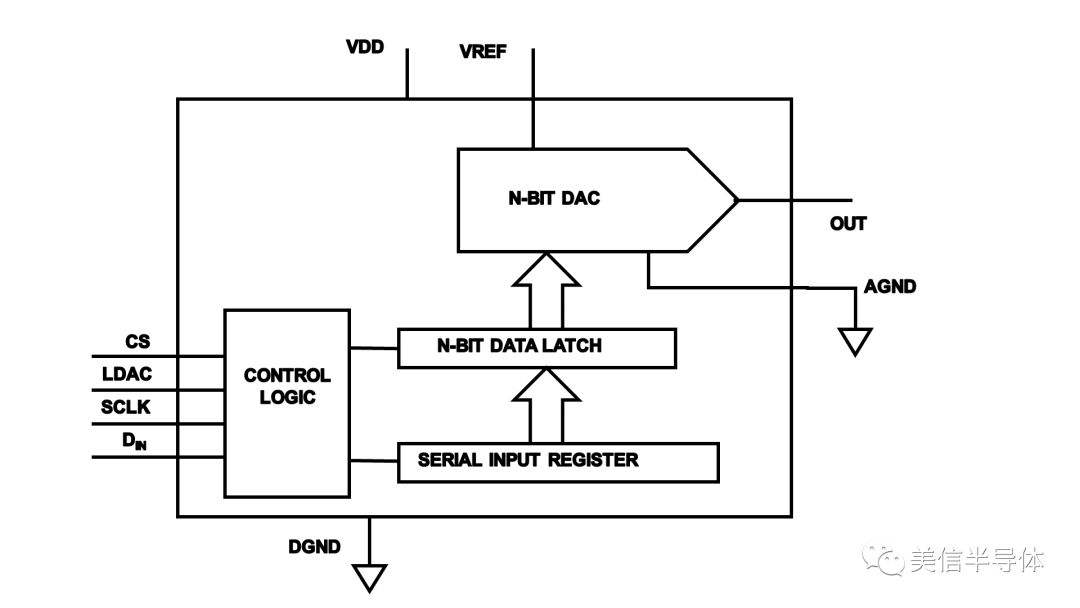

電壓輸出DAC采用FIFO方式,也就是先進先出(圖1)。通常情況下,用戶將DAC的輸入數字數據(DIN)裝載到DAC內部串行輸入寄存器,而將之前的數據編碼鎖存到N位DAC。

圖1. 高精度、電壓輸出DAC的通用方框圖

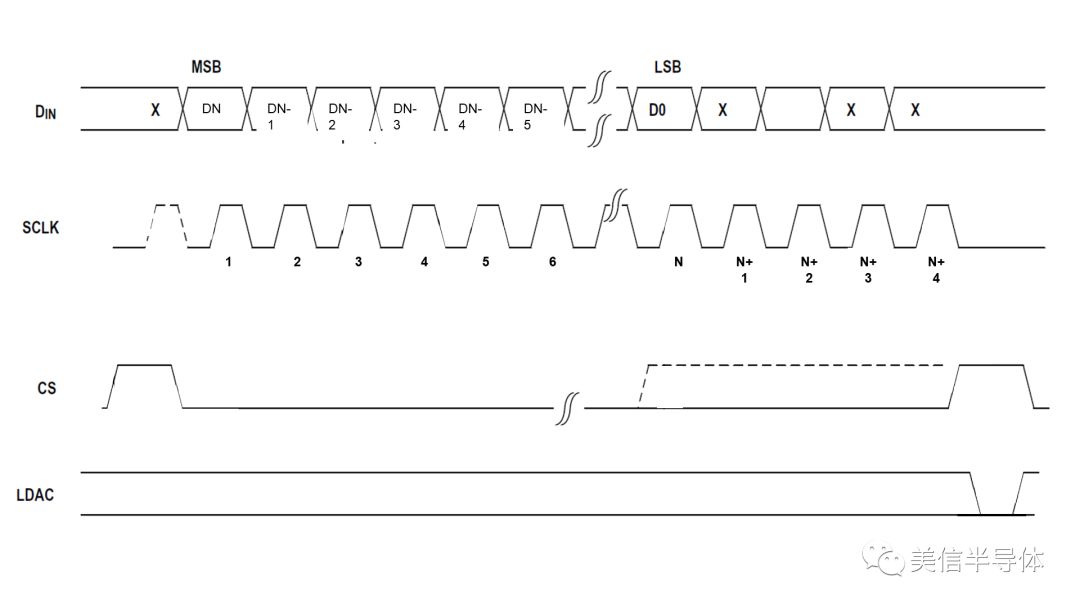

LDAC(裝載DAC)引腳為高電平時,串行數據流與SCLK(串行時鐘)配合,裝載DAC的串行輸入寄存器(圖2)。輸入寄存器填滿之后,LDAC低電平則將串行輸入寄存器裝載到N位數據鎖存器。LDAC再次變為高電平,模擬輸出電壓通過OUT引腳輸出并穩定到最終值。在建立時間期間,串行輸入寄存器接收下一個編碼。

圖2. 高精度、電壓輸出DAC的通用時序圖

理想情況下,DAC的理論吞吐速度等于SCLK/N,其中SCLK為外部時鐘速率,N為DAC的位數。例如,對于16位DAC,最大時鐘速率為50MHz,吞吐率為50MHz/16,即3.125MHz。

這是很了不起的DAC吞吐率!然而,這是非常不現實的,特別是如果您將模擬輸出電壓設置為滿幅或滿擺幅輸出。在這種情況下,您需要時間使輸出穩定到其滿幅值。

建立時間決定一切

所以,我們還是回到現實吧。高精度應用中的建立時間決定DAC的有效更新率,而不取決于時鐘的數據率。DAC的模擬輸出頻率結構通常是一階的。對于較大的信號,很容易利用R/C電路建立這種響應的模型。對于這種電路,可用以下公式描述模擬輸入/輸出行為。

VOUT = VIN(1 – e-t/RC) 式1

式中:

VOUT?模擬輸出電壓

VIN?模擬輸入電壓

R ?DAC輸出電阻

C ? DAC輸出電容

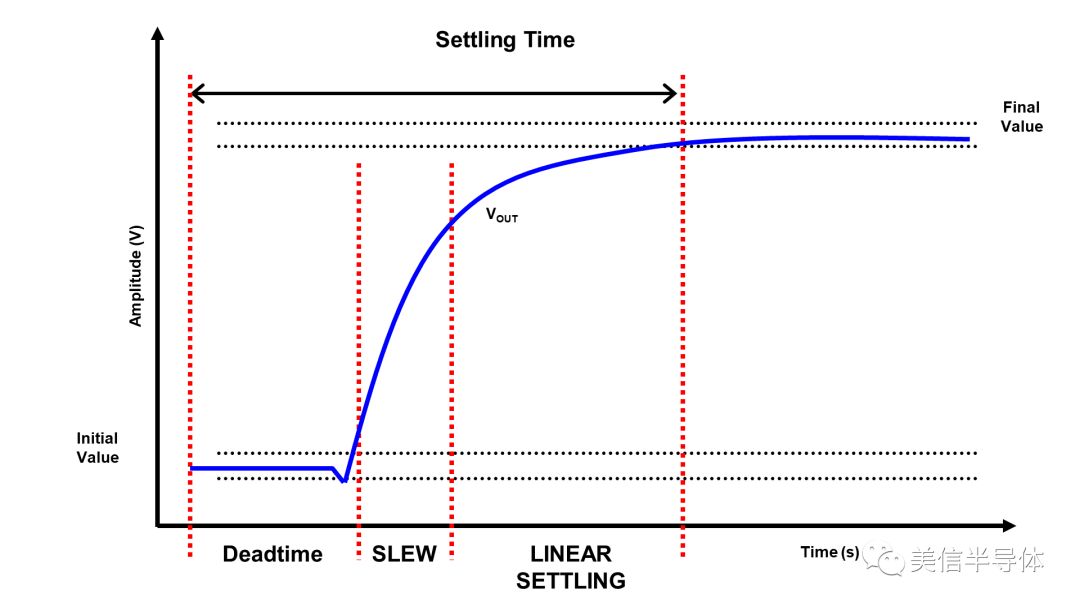

圖3所示為DAC系統的模擬信號建立時間響應,包括死區時間、擺動及線性建立部分。

圖3. DAC的理論輸出建立時間

死區時間是DAC使用數據鎖存寄存器更新模擬輸出的時間。如果發生較大的模擬輸入階躍,DAC將進入擺動區。在該信號響應結束時,最終值為理論最終值的±1/2 LSB。

DAC的數據手冊會列出建立時間指標。以MAX5717 16位、50MHz、電壓輸出DAC為例,建立時間為0.75us。初看之下,會以為DAC的吞吐率為50MHz除以16,即2.33MHz。如果您將DAC的建立時間考慮在內,該DAC的實際吞吐率為建立時間的倒數,即1.33MHz。

重要的工作優先

大量使用DAC的設備都要求DAC行為實現最優化,這取決于系統要求。對于儀器儀表、自動測試和測試/測量應用,吞吐率是主要技術指標。DAC精度性能的細節非常重要,但切記建立時間是使您能夠立即洞察DAC速度是否足夠滿足電路的最佳指標。

-

寄存器

+關注

關注

31文章

5322瀏覽量

120018 -

dac

+關注

關注

43文章

2272瀏覽量

190842

原文標題:Maxim設計指南 | 找到最優的建立時間

文章出處:【微信號:Maxim_Integrated,微信公眾號:美信半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于雙12位DAC的高精度直流電壓/電流源設計

基于MSP430F149_DAC7811的數控直流電壓源程序

示波器如何測量直流電壓?

DAC產生直流電壓或任意波形

DAC產生直流電壓或任意波形

評論