大家好,到了每日學習的時間了。今天我們來聊一聊FPGA的片內資源相關知識。

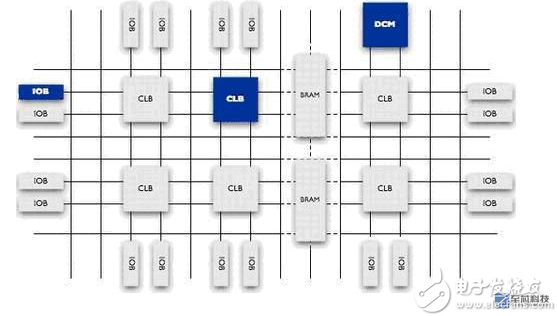

主流的FPGA仍是基于查找表技術的,已經遠遠超出了先前版本的基本性能,并且整合了常用功能(如RAM、DCM和DSP)的硬核(ASIC型)模塊。如圖所示,FPGA芯片主要由7部分組成,分別為:可編程輸入輸出單元(IOB)、基本可編程邏輯單元(CLB)、完整的時鐘管理(DCM)、嵌入式塊RAM、豐富的布線資源、內嵌的底層功能單元和內嵌專用硬件模塊。

1.可編程輸入輸出單元(IOB)

可編程輸入/輸出單元簡稱I/O單元,是芯片與外界電路的接口部分,完成不同電氣特性下對輸入/輸出信號的驅動與匹配要求。FPGA內的I/O按組分類,每組都能狗獨立地支持不同的I/O標準。通過軟件的靈活配置,可是配不通電氣標準與I/O物理特性,可以調整驅動電流的大小,可以改變上、下拉電阻。I/O口的頻率也越來越高。

為了便于管理和適應多種電氣標準,FPGA的IOB被劃分為若干組(bank),每個bank的接口標準由其接口電壓VCCO決定,一個bank只能有一種VCCO,但不同的bank可以有不同的VCCO,只有相同電氣標準的接口才能連接在一起。

2.可配置邏輯塊(CLB)

CLB是FPGA內的基本邏輯單元,CLB的實際數量和特性會因為器件的不同而不同,但是每個CLB都包含一個可配置開關矩陣,此矩陣由4或6個輸入、一些選型電路(MUX)和觸發器組成。開關矩陣是高度靈活的,可以對其進行配置以組成組合邏輯、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB有多個相同的Slice和附加邏輯組成,每個CLB模塊不僅可以用于實現組合邏輯、時序邏輯,還可以配置為分布式RAM和分布式ROM。

Slice是Xilinx公司定義的基本邏輯單位,一個Slice由兩個4輸入的函數發生器(LUT)、進位邏輯、算數邏輯、存儲邏輯和函數復用器組成。

3.數字時鐘管理模塊(DCM)

業內大多數FPGA均提供數字時鐘管理(Xilinx全部FPGA都有這種特性)。Xilinx推出最先進的數字時鐘管理和相位環路鎖定。DCM可以完成對時鐘的分頻倍頻功能,并能維持各時鐘之間的相位關系,即零時鐘偏差。

4.嵌入式塊RAM(BRAM)

BRAM有很高的靈活性,可以被配置位單端口RAM、雙端口RAM、內容地址存儲器(CAM)以及FIFO等常用存儲結構。在實際應用中,芯片內部BRAM數量是芯片選型的一個重要因素,單片塊RAM的容量是18kbits,即位寬為18比特、深度為1024。也可以根據需要更改其位寬與深度(位寬不得大于36bits)。亦可以將多塊BRAM級聯起來形成更大的RAM。

5.豐富的布線資源

布線資源連通FPGA內部所有單元,而連線長度和工藝決定著信號在連線上的驅動能力和傳輸速度。FPGA芯片內部有著豐富的不限資源,根據工藝、長度、寬度和分布位置而劃分為4類不同的類別。第一類是全局布線資源,用于芯片內部全局時鐘和全局復位/置位的布線;二、長線資源,用以完成芯片bank之間的高速信號和第二全局時鐘信號的布線;三、是短線資源,用于完成基本邏輯單元之間的邏輯鏈接和布線;四、分布式的布線資源,用于專有時鐘、復位等控制信號線。

6.底層內嵌功能單元

內嵌功能模塊主要是指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU等軟處理核。

7.內嵌專用硬核

內嵌專用硬核是相對底層遷入的軟核而言的,等效于ASIC電路。為了提高FPGA性能,芯片生產商在芯片內部集成了一些專用的硬核。例如:專用乘法器,串并收發器(SERDES)可以達到數十Gbps收發速度。

今天就聊到這里,各位,加油。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601838

發布評論請先 登錄

相關推薦

聊一聊FPGA低功耗設計的那些事兒

從焊接角度聊一聊,設計PCB的5個建議

來聊一聊Altium中Fill,Polygon Pour,Plane的區別和用法

聊一聊stm32的低功耗調試

聊一聊7系列FPGA的供電部分

聊一聊IIC總線設計

聊一聊華為云彈性公網IP的那些事兒

聊一聊FPGA的片內資源相關知識

聊一聊FPGA的片內資源相關知識

評論