設計原理:

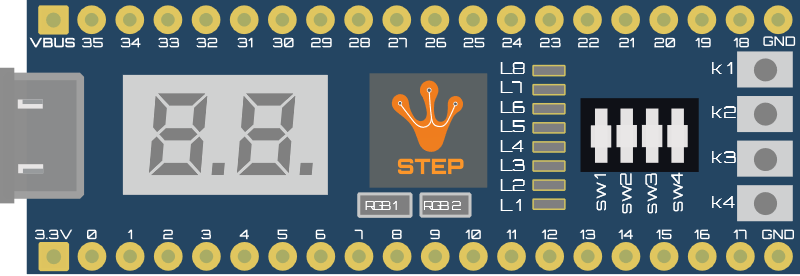

在以后的設計中,用的開發板都將是我們至芯科技自主設計的開發板,我們的芯片用的是Cyclone4系列的EP4CE10F17C8,在以后的設計中我們將不再討論我們的開發板

今天的設計是流水燈,在單片機中我們也了解到流水燈的點亮,不就是高電平或者低電平亮或者滅,然后通過依次的點亮LED燈,就形成了流水

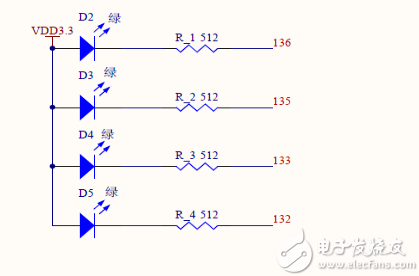

我們用的開發板的電路圖如下

在點圖中我們可以了解到我們的點亮電路,幾個燈都是公用的是高電平也就是3.3V,所以只要給一個低電平就可以點亮我們的流水燈

我們的開發板提供的晶振是50M的,50M一個周期是20ns,我們人眼能夠分辨的的速度是45ms左右,也就是物體如果45ms移動一次我們看清它是停一下走一下的,如果快于這個時間的話,那么我們看到的物體的移動就是連貫的。我們要設計出人眼可以分辨的流水就需要我們設計出大于這個時間燈亮滅,然后形成人眼可以分辨的流水。

本次我們的設計流水燈的流水時間是1s,那么我們就需要一個時間寄存器,當計數到1s的時候我們點亮一個燈,等下一個1s來的時候,我們點亮下一個等,然后形成流水,50M是20ns,1s是1hz,那么我們需要計數50 000 000

值得提的是我們算計數的時間是一面的等式 :計數 = 晶振 / 需要的頻率 ,計數的時間就是我們1hz的周期,那么計數到一半的時候就是半個周期,我們可以在計數一半的時候clk 翻轉,那么當技計數到的時候就是占空比50%的1hz的周期

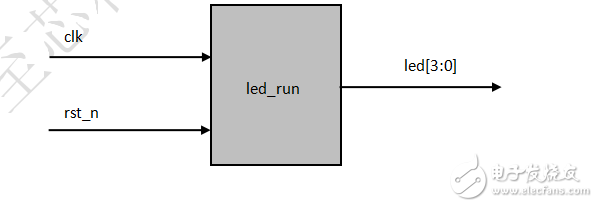

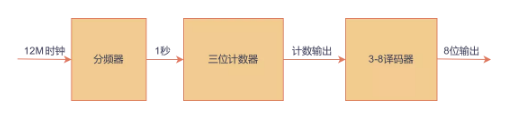

設計架構圖:

設計代碼:

設計模塊

0moduleled_run (clk,rst_n,led);

1

2 inputclk,rst_n;

3

4 outputreg[3:0]led;

5

6 reg[25:0]count;

7 regclk_1hz;

8

9 always@(posedgeclk)

10 if(!rst_n)

11 begin

12 clk_1hz <=1;

13 count <=0;

14 end

15 elseif(count <(50_000_000/1/2-1))//計數

16 count <=count +1'd1;

17 else

18 begin //當計數到的時候,得到1hz的時鐘

19 count <=26'd0;

20 clk_1hz <=~clk_1hz;//~時鐘翻轉

21 end

22

23 always@(posedgeclk_1hz)

24 if(!rst_n)

25 led <=4'b0111; //復位點亮第四個燈,熄滅1 2 3 燈

26 else

27 led <={led[0],led[3:1]};//當時鐘上升沿來的時候把led的第一位 放在

28 //第四位,2 -- 4位放在 3 -- 1位,依次的移位,也就是把復位中的低電平 不停的

29 //移動在4 --1 位之中的某一位,從而實現流水

30endmodule

測試模塊

0`timescale1ns/1ps

1

2moduletb();

3

4 regclk,rst_n;//定義模塊的端口

5 wire[3:0]led;

6

7 initialbegin

8

9 clk =1;

10 rst_n =0;

11

12 #200.1rst_n =1;

13

14 #20000$stop;//延遲20000 Ns后 停止計數

15

16 end

17

18 always#10clk =~clk;//產生一個50M的時鐘

19

20 led_run dut( //例化設計模塊

21 .clk(clk),

22 .rst_n(rst_n),

23 .led(led)

24 );

25

26endmodule

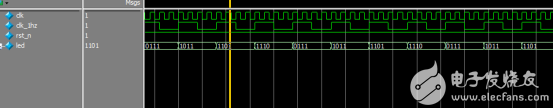

仿真圖:

在仿真中我們可以調下我們設計模塊的中的計數值,這樣在仿真中我們可以我們可以快速的等到仿真結果,要不然你仿真幾個小時可能才會出結果

在仿真中我們可以可以看到在我們的1hz時鐘的上升沿,我們led的4位中的一位將有一位變化為0,從而實現流水

大家可以下板測試

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602022 -

流水燈

+關注

關注

21文章

432瀏覽量

59645

發布評論請先 登錄

相關推薦

基于FPGA的音樂流水燈控制系統設計

基于Verilog FPGA 流水燈設計_流水燈源碼_明德揚資料

FPGA零基礎學習:LED流水燈設計

使用FPGA實現流水燈的詳細資料說明

詳解基于FPGA的數字電路對流水燈的實驗

51單片機學習筆記———8.點亮流水燈的一種奇葩算法

【STM32學習】(3)流水燈的實現

基于FPGA開發板流水燈的設計實現

FPGA學習系列:8. 流水燈的設計

FPGA學習系列:8. 流水燈的設計

評論