對于一個終端用戶來說,打開一個電子設備很簡單;只需按下按鈕就可以了。然而,需要花費大量的精力來創建一個平滑順暢的加電體驗。系統接通的過快將會導致由不可控的涌入電流大尖峰所引起的電源故障。對于那些基于微處理器或FPGA的應用來說,正確的運行需要特定的電源軌排序。有時候,在啟用下游電路之前,最好讓特定的子系統加電。使用負載開關來管理電源排序可以更輕松地為終端用戶提供平滑順暢的加電體驗。

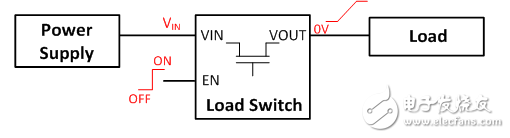

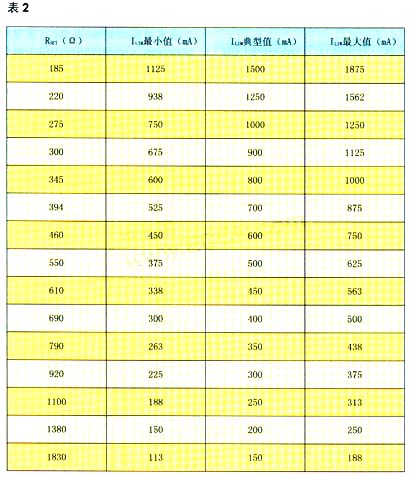

在大多數系統中,在一個設計中遍布著電容器,以確保不會出現電源軌壓降。在最開始加電時,為這些電容器充電會導致涌入電流;而這個涌入電流會超過下游電路的最大電流額定值。如果聽之任之,這會使得電壓軌處于穩壓之外,從而使系統進入不利的狀態。不對涌入電流進行檢查和限制也會損壞電路板連接器和電路板跡線,這是因為涌入電流超過了它們的承載能力。為了管理涌入電流,施加到電容負載上的電壓需要具有一個受控的上升時間。所有德州儀器 (TI) 負載開關都具有一個集成軟啟動,而某些器件甚至提供針對變化電容負載的可調上升時間。圖1顯示的是這個集成軟啟動。

圖1:一個為系統負載提供受控上升時間的負載開關

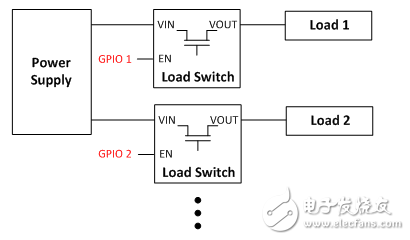

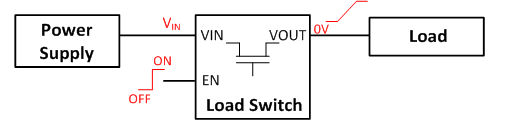

在電源和電容負載之間放置一個負載開關能夠極大地降低接通/啟用負載時的涌入電流。很多處理器和FPGA具有非常明確的電源排序要求,以及一個特定的電源軌接通順序。負載開關使滿足電源排序要求變得更加簡單,從而實現針對每個電源軌的負載點控制。那么,為每個電源軌供電就簡單到只需將正確的GPIO信號發送給正確的負載開關。圖2顯示了這個概念。

圖2:為每個負載使用單獨GPIO的電源排序

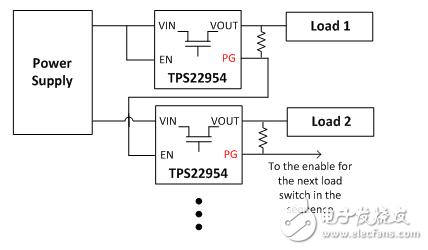

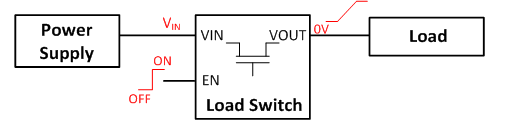

某些負載開關甚至具有一個電源正常 (PG) 信號;這個信號表示輸出何時完全接通。通過將PG信號接至序列中下一個負載開關的啟用引腳,對于所有電源軌來說,電源排序就只需要一個GPIO信號了。圖3顯示了這個配置。

圖3:無需GPIO信號的電源排序

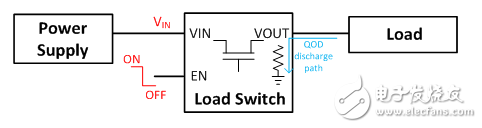

負載開關對于系統斷電同樣有效。負載開關的下降時間由輸出負載對其電容的放電速度決定。為了加快這個放電過程,并且確保一個0V狀態,某些負載開關具有一個快速輸出放電 (QOD) 特性,如圖4所示,這個特性通過一個內部電阻將輸出放電至接地電平。

圖4:一個支持QOD的負載開關

不論系統是加電還是放電,負載開關都能使時序和排序要求簡單到按下一個按鈕即可完成。

-

電源管理器

+關注

關注

0文章

43瀏覽量

12027 -

負載開關

+關注

關注

2文章

181瀏覽量

18844 -

GPIO

+關注

關注

16文章

1196瀏覽量

51915

發布評論請先 登錄

相關推薦

什么是負載開關,為什么需要負載開關

電源中的負載管理與負載開關設計與實現

教你如何選擇正確的負載開關

Load Switch負載開關詳解

在使用負載開關時,時序的作用是怎樣的

如何使用負載開關來管理電源排序

如何使用負載開關來管理電源排序

評論