你評(píng)估過一個(gè)ADC的噪聲性能,并且發(fā)現(xiàn)測得的性能不同于器件數(shù)據(jù)表中所給出的額定性能嗎?在高精度數(shù)據(jù)采集系統(tǒng)中實(shí)現(xiàn)高分辨率需要對(duì)模數(shù)轉(zhuǎn)換器 (ADC) 噪聲有一定的認(rèn)識(shí)和了解。有必要了解數(shù)據(jù)表如何指定噪聲性能,以及外部噪聲源對(duì)總體系統(tǒng)性能的影響方式。其中的一個(gè)噪聲源示例就是我的同事Ryan Andrews在他的博文,“小心!你的ADC的性能也許只和它的電源性能差不多。”中所談到過的電源噪聲。在這篇博文中,我將會(huì)看一看基準(zhǔn)噪聲如何影響增量-累加ADC中的DC噪聲性能。

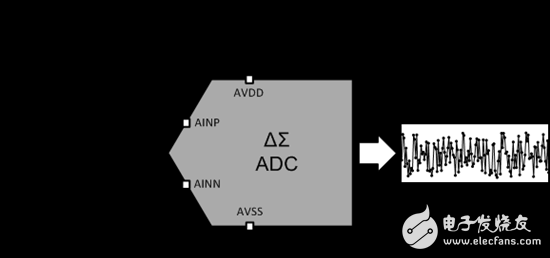

如圖1所示,你可以用短接至中電源電壓的正負(fù)輸入來指定和測量一個(gè)ADC的DC噪聲性能。通過測量這個(gè)條件下的噪聲,ADC輸出代碼內(nèi)的噪聲幾乎不受基準(zhǔn)電壓、基準(zhǔn)噪聲或輸入信號(hào)噪聲變化的影響。雖然這個(gè)測試條件相對(duì)于實(shí)際應(yīng)用來說是一個(gè)過于理想的情況,它的確較好地給出了一個(gè)不受某些外部噪聲源影響的ADC噪聲性能。

圖1:ADC噪聲性能測試(和調(diào)試)配置

提示:調(diào)試時(shí),在開始其它系統(tǒng)噪聲性能測試之前,用評(píng)估隔離式ADC噪聲性能的短接輸入測試來開始評(píng)估系統(tǒng)的噪聲性能。

基準(zhǔn)噪聲如何影響ADC DC噪聲性能

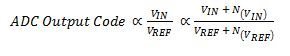

這個(gè)影響與ADC的基本任務(wù)相關(guān);而ADC的基本任務(wù)就是提供一個(gè)輸出代碼,來表示輸入信號(hào)電壓與基準(zhǔn)電壓的比率。輸入和基準(zhǔn)電壓都會(huì)將一個(gè)噪聲項(xiàng)添加到這個(gè)比率中,如方程式1所示:

(1)

輸入信號(hào)噪聲,

,對(duì)于ADC轉(zhuǎn)換結(jié)果的影響是非常直接的。ADC將捕捉未被濾除掉的任何噪聲—使用外部電阻-電容 (RC) 濾波器,或者增量-累加ADC的信號(hào)濾波器進(jìn)行過濾。由于

對(duì)于方程式1中的比率有直接影響,你可以在輸出代碼中進(jìn)行觀察。

提示:在評(píng)估ADC噪聲性能時(shí),由于輸入信號(hào)的噪聲直接影響ADC的輸出結(jié)果,請(qǐng)確保輸入信號(hào)是一個(gè)低噪聲源。

然而,基準(zhǔn)噪聲,

,對(duì)于ADC轉(zhuǎn)換結(jié)果的影響并不直接,這是因?yàn)?/p>

出現(xiàn)在分母中。當(dāng)分子為零時(shí)(就與ADC輸入被短接的情況一樣),這個(gè)比率始終為零,而

項(xiàng)將不會(huì)影響比率。當(dāng)分子與分母大體相等時(shí),

將會(huì)對(duì)比率有很大的影響。當(dāng)比率介于0和1之間時(shí),

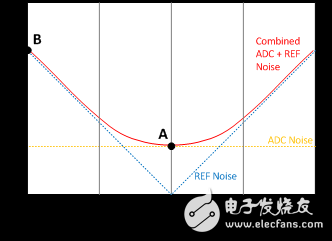

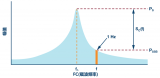

的影響由比率值來衡量。圖2顯示的是得出的特性運(yùn)行方式。

圖2:ADC和基準(zhǔn)噪聲與輸入電壓之間的關(guān)系

當(dāng)通過使用均方根增加的方法將基準(zhǔn)噪聲添加到ADC的噪聲中時(shí),這個(gè)組合噪聲是輸入電壓的函數(shù),它會(huì)在正或負(fù)輸入電壓變大時(shí)增加。在圖2中的曲線上,有幾個(gè)點(diǎn)需要注意:

-

點(diǎn)A,這是用ADC數(shù)據(jù)表中給出的短接輸入測得的ADC噪聲。

-

點(diǎn)B,這是總帶寬限制基準(zhǔn)噪聲,通常受到ADC數(shù)字濾波器帶寬的限制。

如果你知道針對(duì)噪聲源的噪聲頻譜密度和噪聲帶寬的話,你就能夠計(jì)算出基準(zhǔn)噪聲(點(diǎn)B);否則的話,將一個(gè)滿量程電壓輸入施加到ADC上,并且測量噪聲性能,這樣通常能夠獲得一個(gè)比較好的基準(zhǔn)噪聲測量值。

如何選擇一個(gè)基準(zhǔn)電壓源

對(duì)于在整個(gè)ADC輸入范圍內(nèi)實(shí)現(xiàn)低噪聲/高分辨率性能來說,一個(gè)低噪聲基準(zhǔn)十分重要。基準(zhǔn)噪聲需求將取決于系統(tǒng)的目標(biāo)分辨率、輸入信號(hào)范圍和數(shù)據(jù)速率(而這通常限制了輸入和基準(zhǔn)噪聲帶寬)。當(dāng)噪聲帶寬受到較慢數(shù)據(jù)速率限制時(shí),或者輸入信號(hào)跨度被限制在ADC滿量程范圍內(nèi)的一個(gè)較小區(qū)間內(nèi),系統(tǒng)能夠耐受額外的基準(zhǔn)噪聲。

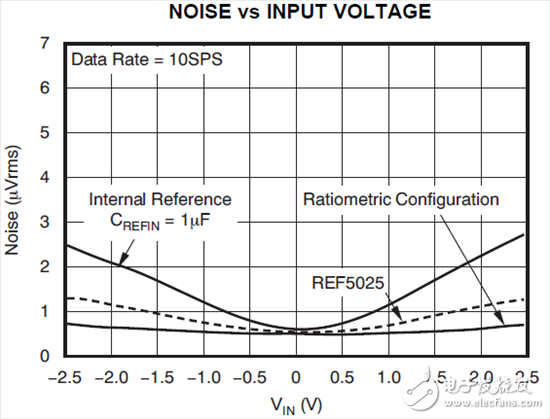

很多增量-累加ADC包含一個(gè)集成基準(zhǔn),它為大多數(shù)應(yīng)用提供了充足的性能。對(duì)于要求更加嚴(yán)格的應(yīng)用,使用一個(gè)外部基準(zhǔn)也許可以提升輸入處于正和負(fù)滿量程范圍附近時(shí)的噪聲性能。外部高精度基準(zhǔn)可以實(shí)現(xiàn)更低的噪聲性能,這是因?yàn)樗鼈兊墓母摺D3將24位ADS1259增量-累加ADC的噪聲性能與內(nèi)部基準(zhǔn)源、一個(gè)外部REF5025電壓源,以及一個(gè)比例換算的基準(zhǔn)源進(jìn)行比較。

圖3:具有內(nèi)部、外部和比例換算基準(zhǔn)源的ADS1259噪聲性能

雖然外部基準(zhǔn)也許能夠?qū)崿F(xiàn)比集成基準(zhǔn)更好的噪聲性能,而比例換算基準(zhǔn)配置的表現(xiàn)更佳。一個(gè)比例換算配置在基準(zhǔn)電壓和輸入信號(hào)激勵(lì)方面共用同樣的電壓源。通過共用一個(gè)共同的電壓和噪聲源,方程式1中的和往往在比率中相互抵消。

當(dāng)你下次評(píng)估ADC的噪聲性能時(shí),請(qǐng)確保將基準(zhǔn)噪聲效應(yīng)考慮在內(nèi)。此外,只要傳感器需要一個(gè)激勵(lì)源,比例換算測量實(shí)現(xiàn)方式應(yīng)該成為你的首選。

-

測試測量

+關(guān)注

關(guān)注

25文章

884瀏覽量

90576 -

adc

+關(guān)注

關(guān)注

98文章

6438瀏覽量

544106 -

基準(zhǔn)電壓源

+關(guān)注

關(guān)注

1文章

138瀏覽量

20810

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ADC噪聲系數(shù)對(duì)射頻接收器的影響

adc的噪聲分析與優(yōu)化方法

怎樣準(zhǔn)確合理測試單板上DAC80504輸入的系統(tǒng)噪聲?

為什么運(yùn)放和ADC的PSRR不能把LDO輸出的內(nèi)部噪聲抑制的干干凈凈呢?

ADC靜態(tài)測試全流程:以斜坡測試為例(二)

ADC靜態(tài)測試全流程:以斜坡測試為例(一)

如何描述相位噪聲的大小 相位噪聲測試和意義

ADC噪聲性能測試和調(diào)試配置

ADC噪聲性能測試和調(diào)試配置

評(píng)論