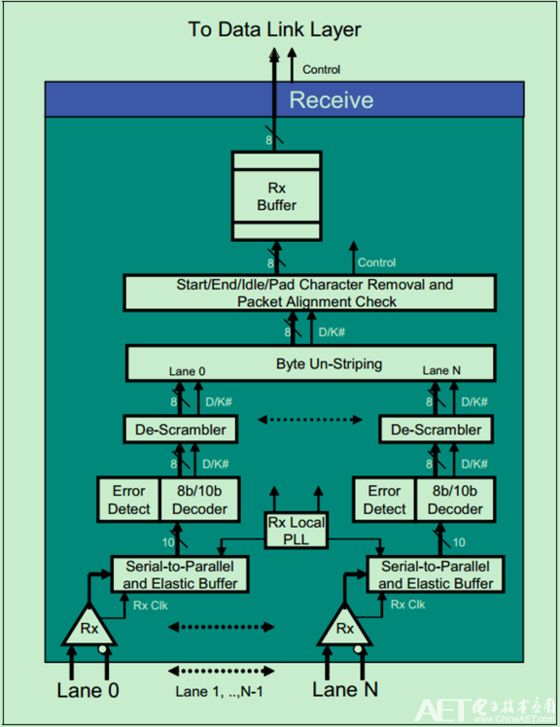

這一篇文章來繼續聊一聊接收端物理層邏輯子層的實現細節。回顧一下之前的那張圖片:

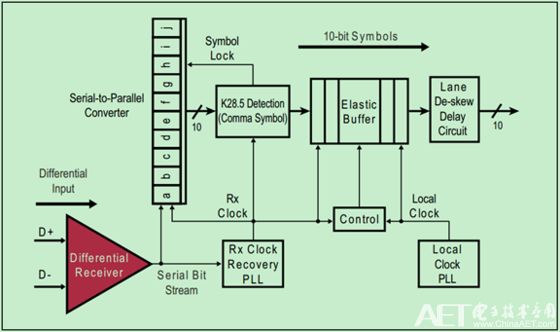

其中的一個Lane的具體邏輯如下圖所示:

其中,Rx Clock Recovery從輸入的串行數據流中提取出Rx Clock。當Rx Clock穩定在Tx Clock的頻率上(Rx Clock locked on to the Tx Clock Freq)時,我們就稱接收端取得了Bit Lock。

如果鏈路(Link)處于低功耗狀態(比如L0s或者L1)時,接收端此時會失去同步(即Losing Bit Lock)。為了避免物理層認為這是一個錯誤(異常),發送端會發送一個電氣空閑命令集(Electrical Idle Ordered Sets,EIOS)通知接收端,即將進入低功耗狀態。此時,接收端會臨時關閉(De-gate)其輸入。

注:這里的關閉(De-gate)并非是直接關閉輸入端口,只是暫時不對輸入端口上的數據進行處理。

當發送端需要喚醒鏈路(Link)時,會首先發送一定數量的FTS Ordered Sets,并重新取得Bit Lock和Symbol Lock。

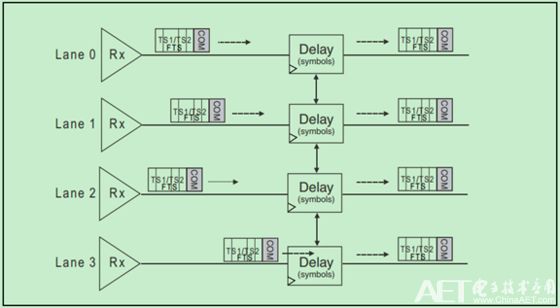

接收端的鏈路De-Skew邏輯如下圖所示:

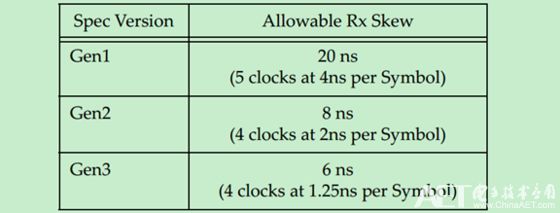

Gen1和Gen2的PCIe采用COM字符來進行De-Skew,如果COM沒有同事出現在每個Lane上,那么先到達的COM會被延時一會,以實現Lane的同步。很顯然,這種機制只能校正比較小的Skew,也就是說Lane-to-Lane的Skew有一個最大值,超出這個最大值,De-Skew也無能為力了。如下表所示:

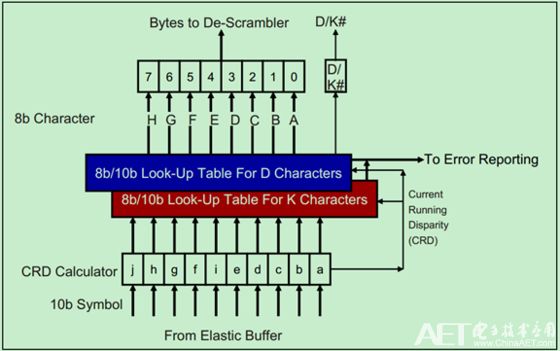

接收端的8b/10b解碼器結構如下圖所示:

以下情況,被認為是編碼沖突(Code Violation),即該字符在傳輸過程中發生了錯誤:

關于解擾碼器(Descrambler)和Byte Un-striping都比較簡單了,這里就不在詳細地介紹了。具體可以參考PCIe Spec的相關內容。

-

PCIe

+關注

關注

15文章

1217瀏覽量

82441 -

物理層

+關注

關注

1文章

148瀏覽量

34287

原文標題:【博文連載】PCIe掃盲——物理層邏輯部分基礎(三)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

無線網絡物理層借口操作與功能

CAN總線不同的物理層

什么是以太網物理層?Ethernet物理層有哪些功能?

WCDMA系統的物理層(FDD)

物理層的作用

PCIe物理層實現了一對收發差分對,可以實現全雙工的通信方式

PCIe物理層接口定義了物理層中的,媒介層和物理編碼子層之間的統一接口

WLAN物理層關鍵通信技術

聊一聊接收端物理層邏輯子層的實現細節

聊一聊接收端物理層邏輯子層的實現細節

評論