所有芯片的設計跟普通的產品一樣,需有一個標準規范化的流程(flow)。然后工程師們按照流程,運行和調試參數來得到一個合格的結果。

隨著EDA軟件的不斷發展,新的技術不斷涌現,flow的選擇性也呈現出多元化的趨勢。所以了解新知識,新技術對于我們來說,是相當有必要的。

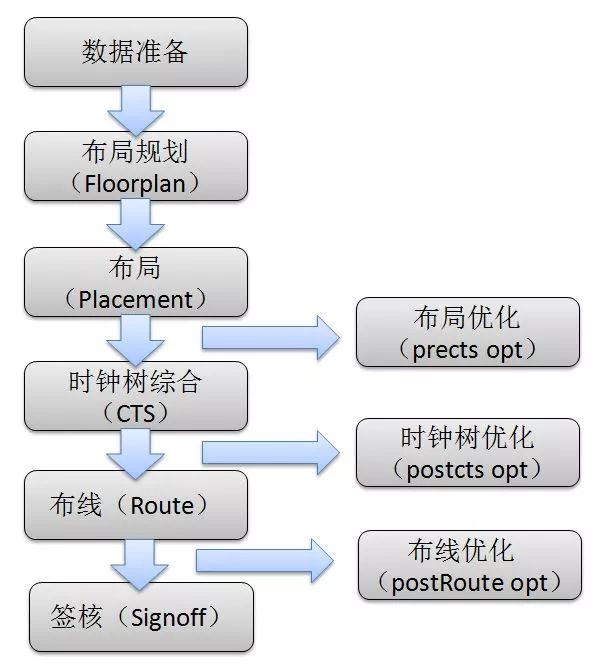

從設計的大方向上講,flow分為傳統的展平式設計(flat flow)和層次化設計(hierarchical flow)。展平式設計是集成電路設計中最基本的一種方法,芯片在全局范圍內進行優化,通過布局繞線實現物理設計,提取RC參數進行時序分析,最后產生GDSII文檔完成全部過程。簡單的可以參考如下flat flow示意圖:

展平式設計通常能取得更好的時序結果,但是卻要花費極長的設計周期。隨著電子技術的極速發展,單個芯片上的邏輯單元已經從幾萬們增加到幾千萬門,甚至幾億門。這對EDA工具,工程師,甚至計算機硬件都是一個極大的挑戰。這時候就產生了層次化設計方案(hierarchical flow,簡稱Hier flow)。

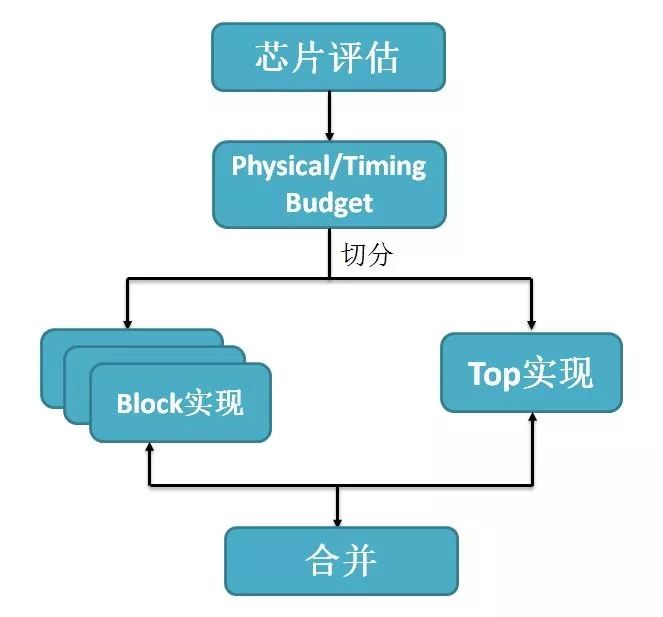

層次化設計是指對一個普通設計,在邏輯上定義出層次化器件(hinst),在物理上給予層次化器件一個物理約束(physical constraint),然后將具有物理約束的層次化器件定義為一個劃分(partition),再將各個劃分切出整個設計,剩下的部分保存為頂層設計(top),而各個劃分則單獨保存,對于頂層而言,切出去的劃分視為黑盒(black box),而對于單個劃分而言,在做分塊實現(blockimplementation)的時候則視為片級設計(chip level design)。在完成分塊實現以及頂層實現(top implementation)之后,最后將各個劃分合并(assemble)到一起,完成全芯片(full chip)的簽收(sign off)。簡單的示意圖如下所示:

層次化設計的方案的最大優點是它將很大的設計化成多個小設計,如果有時序問題可能存在于個別模塊,再去重點解決,則復雜性變小,而且是局部的。同時,每個工程師分擔的工作量也變小,完成設計的周期會縮短,從而加快了設計收斂。

當然,層次化設計也有許多不可避免的缺陷,最突出就是來源于時序預估時產生的誤差。這種誤差往往使得做劃分的物理實現時,時序難以收斂。或者盡管劃分滿足時序收斂條件,在全芯片合并后,會發現一些時序路徑又會變得極差無比。在手工ECO無效時,這種情況可能需要重做時序預估和劃分的物理實現,最壞可能導致重新調整布圖規劃的風險。為了解決這些問題,傳統的層次化設計方法也提出了許多更為先進的設計理念來提高時序精度,這些方法應用于層次化設計中的各個步驟中。從時序收斂的角度,展平化設計要比層次化設計精準很多。所以當設計的規模沒有達到無法采用展平的設計方法完成時,設計者會偏向采用展平的設計方法來實施。

-

芯片

+關注

關注

453文章

50406瀏覽量

421824 -

集成電路

+關注

關注

5381文章

11385瀏覽量

360871 -

eda

+關注

關注

71文章

2708瀏覽量

172881

原文標題:空間的藝術——展平式設計與層次化設計

文章出處:【微信號:IC_Physical_Design,微信公眾號:數字后端IC芯片設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

展平式設計是集成電路設計中最基本的一種方法

展平式設計是集成電路設計中最基本的一種方法

評論