本設計實例中使用分立晶體管對由相關精密電阻所控制的五個三態引腳中每一個的三態加權電流(1、3、9、27、81μA)進行求和。每個阻值由其特定屈特的電流權重與施加兩端的參考電壓之比決定。

Trit:屈特,名詞(計算),用一位表述三態,是可以有三種不同狀態的基本信息單位。

EDN主編Michael Dunn寫過一篇有趣的文章“三進制DAC:分辨率更高,位數更少”(見《EDN電子技術設計》4月刊),文中探索了一個有趣的想法:從那些能夠單獨編程為輸出和三態(即0、高阻、1,分別對應三態值0、1、2)的端口引腳,得到比通常單個比特更多的信息。從信息論的角度看,1屈特≈1.58比特,這是很有意義的,例如,只需5屈特就可獲得接近8比特的分辨率。

然而,從一個資深模擬設計師的角度看,最有趣的是將理論轉化為精確的輸出,同時適應溫度變化、單軌電源帶有噪聲并可變等現實世界的復雜問題。Michael的文章闡述了一些有趣方法。圖1是另一種方法。

圖1:三態DAC將分立晶體管與并聯基準結合起來。

我的設計是使用分立晶體管對相關精密電阻所控制的五個三態引腳中每一個的三態加權電流(1、3、9、27、81μA)進行求和。每個阻值由其特定屈特的電流權重與施加其上的電壓參考比決定,對于t = 0、1、2、3、4 ...,根據公式1,有:

Rt=1M?(2V ? 0.06?log10(3t)) / 2V/3t (1)

讀者可能看出0.06?log項是正向偏置雙極結(在此為2N5087的發射極/基極結)兩端電壓常見的二極管公式,它對源于每個DAC屈特的不同電流的VBE產生影響。2V項來自LM4040參考,它提高了PSRR(電源抑制比)精度, 2N5089的射極跟隨器阻抗耦合進其20kΩ偏置電阻會影響PSRR精度。

PSRR = 20kΩ/(26mV/120μA)=39dB (2)

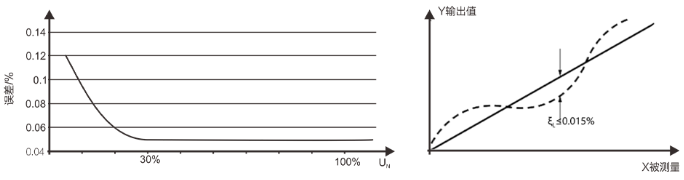

用圖1中的標準值代替公式1中計算出的值就可得出圖2中預測的不錯的性能,包括良好的單調性、積分線性和準確性。

圖2:三態DAC具有良好的線性和單一性。

圖3:仔細觀察積分非線性,右軸為電壓。

盡管將普通的二進制輸出多路復用至各種便宜且容易獲得的單片DAC芯片有多種可選方法,本文還是介紹了這種可節省幾個端口引腳的器件密集方法。當然,前述均不能解決其明顯的實用性或性價比問題。想一想,這可能是一件好事。

或許,并非所有令人愉悅的難題一定要實用?

-

dac

+關注

關注

43文章

2226瀏覽量

190439 -

比特

+關注

關注

0文章

16瀏覽量

10460

發布評論請先 登錄

相關推薦

VS高精度電壓傳感器

關于比特率與波特率的定義與區別介紹

馬斯克:比特幣是有價值的

富特科技將在深交所創業板上市

富特科技創業板IPO注冊生效

vs1053模塊怎么接喇叭

比特幣價格突破42000美元 比特幣價格創下年內新高

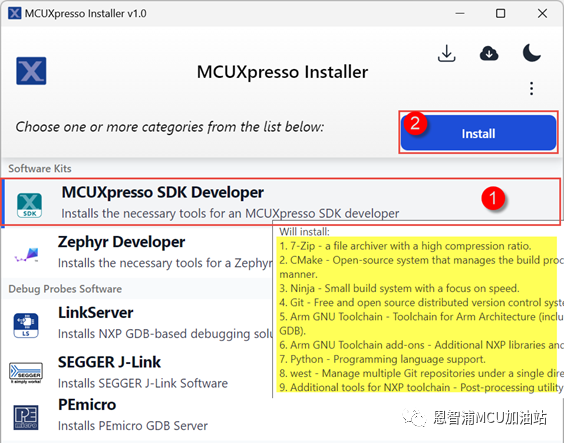

MCUXpresso for VS Code保姆式教程免費送!

關于屈特 vs 比特的相關設計

關于屈特 vs 比特的相關設計

評論