聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

552文章

7962瀏覽量

348265 -

ti

+關注

關注

112文章

7966瀏覽量

212136 -

Cache

+關注

關注

0文章

129瀏覽量

28298

發布評論請先 登錄

相關推薦

請問C6748分別在simu和emu下調用運算庫DSP_dotprod,cycle數不對,emulation下慢4倍,這是為什么?

支持C67芯片,不知道C64的庫是不是全支持,現在運算結果是正確的)DSP_dotprod.h中說cycle=N/4+16,在CCS5.4的

發表于 06-21 06:21

在DSP/BIOS想將L2的64k配置成cache,請問需要怎么操作?

您好,我使用的芯片是C6748,使用DSP/BIOS。C6748的L1P L1D L2都可以部分配置成緩存或RAM。DSP/BIOS

發表于 08-02 06:54

AVS變換算法在C64x+DSP上的實現

討論了音視頻編碼標準AVS 中比較耗時的部分——8x8 IDCT 變換的一維快速算法,提出了變換算法在TI 公司的TMS320DM6446 芯片的C64x+ DSP 子系統上的快速實現

發表于 08-24 08:38

?10次下載

TI C64XX DSP特點及線性匯編程序分析

TI C64XX DSP特點及線性匯編程序分析

TI的DSP C64XX系列的EMIF口是否能在不同的CE空間掛兩種不同的同步器件請教一個

發表于 04-07 10:48

?36次下載

采用Linux內核的C64x系列(TI)

采用Linux內核的C64x系列(TI)

德州儀器 (TI) 推出為其 C64x 系列數字信號處理器 (DSP) 與多內核片

發表于 05-11 17:29

?1386次閱讀

32位DSP兩級cache的結構設計

本文參照計算機存儲結構,利用虛擬存儲技術,對存儲系統的結構進行了改進。在DSP中引入二級Cache存儲器結構,在較小的硬件開銷下提高了

發表于 12-10 16:25

?2203次閱讀

TMS320C64x+ DSP 大字節DSP庫 程序員參考

TMS320C64x + TMS320C64X數字信號處理器(DSP)的TMS320C6000系列DSP

發表于 04-13 16:55

?7次下載

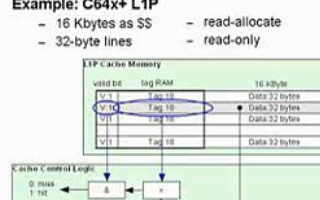

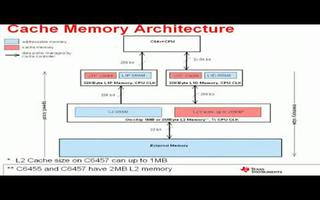

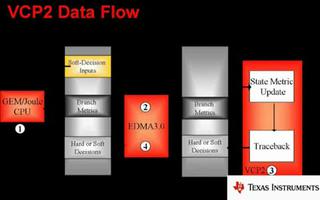

基于c64+的DSP芯片的特點

此次培訓課程,會讓您了解到,基于c64+的DSP芯片,能滿足電信,醫療,視頻處理應用領域中,高性能DSP的需求。由DSP高性能部門技術支持工程師為您全程指導,敬請觀看。

TMS320C64x在高性能DSP應用中的高速緩存使用情況

電子發燒友網站提供《TMS320C64x在高性能DSP應用中的高速緩存使用情況.pdf》資料免費下載

發表于 10-21 09:43

?0次下載

DSP上Cache 在 C64+ 系列中的應用(2)

DSP上Cache 在 C64+ 系列中的應用(2)

評論