聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

601999 -

Altera

+關(guān)注

關(guān)注

37文章

777瀏覽量

153859 -

DIY

+關(guān)注

關(guān)注

176文章

886瀏覽量

348281 -

數(shù)字時(shí)鐘

+關(guān)注

關(guān)注

2文章

150瀏覽量

20310

發(fā)布評論請先 登錄

相關(guān)推薦

DIY個人的Linux開發(fā)板教程

作者簡介:大佬已在硬創(chuàng)社開源了近50款開發(fā)板,動手能力極強(qiáng),于去年年底開始接觸學(xué)習(xí)Linux,并由全志V3s、F1C200S等芯片開始上手DIY個人的Linux開發(fā)板。

【Runber FPGA開發(fā)板】配套視頻教程——數(shù)字鐘實(shí)驗(yàn)

本視頻是Runber FPGA開發(fā)板的配套視頻課程,本實(shí)驗(yàn)設(shè)計(jì)一個具有計(jì)時(shí)功能和校時(shí)功能的數(shù)字時(shí)鐘。數(shù)碼管顯示小時(shí)和分鐘,秒鐘用LED閃爍標(biāo)

發(fā)表于 04-13 14:25

Altium推出智能FPGA開發(fā)板NanoBoard 300

Altium推出智能FPGA開發(fā)板NanoBoard 3000產(chǎn)品系列

Altium 宣布推出 NanoBoard FPGA 開發(fā)板產(chǎn)品系列的最新產(chǎn)品。

NanoBoard

發(fā)表于 11-04 17:01

?1186次閱讀

FPGA實(shí)現(xiàn)數(shù)字時(shí)鐘

在Quartus Ⅱ開發(fā)環(huán)境下,用Verilog HDL硬件描述語言設(shè)計(jì)了一個可以在FPGA芯片上實(shí)現(xiàn)的數(shù)字時(shí)鐘. 通過將設(shè)計(jì)代碼下載到FPGA

發(fā)表于 11-29 16:51

?183次下載

電源、時(shí)鐘和復(fù)位電路圖(Altera FPGA開發(fā)板)

電源、時(shí)鐘和復(fù)位電路圖(Altera FPGA開發(fā)板)如圖所示:

發(fā)表于 08-15 14:42

?9628次閱讀

采用FPGA DIYK開發(fā)板控制模為60的計(jì)數(shù)器數(shù)碼管動態(tài)顯示

FPGA diy作業(yè)實(shí)現(xiàn)模為60的計(jì)數(shù)器數(shù)碼管動態(tài)顯示。

采用FPGA DIY開發(fā)板實(shí)現(xiàn)數(shù)碼管動態(tài)顯示60計(jì)數(shù)

asean的 FPGA DIY 數(shù)碼管動態(tài)顯示60計(jì)數(shù)視頻

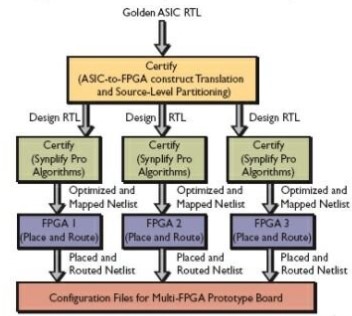

采用FPGA的原型開發(fā)板進(jìn)行ASIC驗(yàn)證與開發(fā)設(shè)計(jì)

在不太遙遠(yuǎn)的過去,對ASIC設(shè)計(jì)團(tuán)隊(duì)而言,在這類情況下主要的解決方案就是在內(nèi)部建立他們自己的定制多個FPGA的原型開發(fā)板。然而,今天,使用現(xiàn)成的多個FPGA原型開發(fā)板——例如,由Syn

fpga開發(fā)板與linux開發(fā)板區(qū)別

(Field-Programmable Gate Array)是一種可編程邏輯器件,它可以通過編程改變硬件邏輯電路的功能和結(jié)構(gòu)。FPGA采用了可編程的門極,可以根據(jù)需要重新配置內(nèi)部電路,從而實(shí)現(xiàn)不同的功能和邏輯關(guān)系。而Linux開發(fā)板

fpga開發(fā)板是什么?fpga開發(fā)板有哪些?

FPGA開發(fā)板是一種基于FPGA(現(xiàn)場可編程門陣列)技術(shù)的開發(fā)平臺,它允許工程師通過編程來定義和配置FPGA芯片上的邏輯電路,以實(shí)現(xiàn)各種

采用FPGA DIY開發(fā)板設(shè)計(jì)數(shù)字時(shí)鐘顯示

采用FPGA DIY開發(fā)板設(shè)計(jì)數(shù)字時(shí)鐘顯示

評論